## 3.75 kV<sub>RMS</sub>, 4.5-A/9-A Isolated Single Channel Gate Driver

# NCV51152

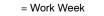

The NCV51152 is a family of isolated single-channel gate driver with 4.5–A/9–A source and sink peak current respectively. They are designed for fast switching to drive power MOSFETs, and SiC MOSFET power switches. The NCV51152 offers short and matched propagation delays. The NCV51152xA provides a split output that controls the rise and fall times ndividually. The NCV51152xB has its  $V_{CC}$  UVLO referenced to GND2 to get a true UVLO.

The NCV51152 is available in a 4 mm SOIC–8 package and can support isolation voltage up to  $3.75 \text{ kV}_{RMS}$ .

The NCV51152 offers other important protection function such as independent under-voltage lockout for both-side driver.

## Features

- Feature Options

- Separated Outputs (NCV51152xA)

- Wide Bias Voltage Range Including Negative V<sub>EE</sub> and V<sub>CC</sub> UVLO Referenced to GND2 (NCV51152xB)

- 3-V to 20-V Input Supply Voltage

- Output Supply Voltage from 6.5 V to 30 V with 5–V and 8–V for MOSFET, 12–V and 17–V for SiC, Threshold

- 4.5-A Peak Source, 9-A Peak Sink Output Current Capability

- 200 V/ns dV/dt Immunity

- Negative 5–V Handling Capability on Input Pins

- Propagation Delay Typical 36 ns with

- 5 ns Max Delay Matching

- Gate Clamping During Short Circuit (NCV51152xA)

- AEC-Q100 Qualified for Automotive Application Requirements

- Isolation & Safety

- 3.75 kV<sub>RMS</sub> Isolation for 1 Minute (per UL1577 Requirements) (Planned)

- CQC Certification per GB4943.1-2011 (Planned)

- SGS FIMO Certification per IEC 62386-1 (Planned)

## **Typical Applications**

- On-board Chargers

- xEV DC-DC Converters

- Traction Inverters

- Charging Stations

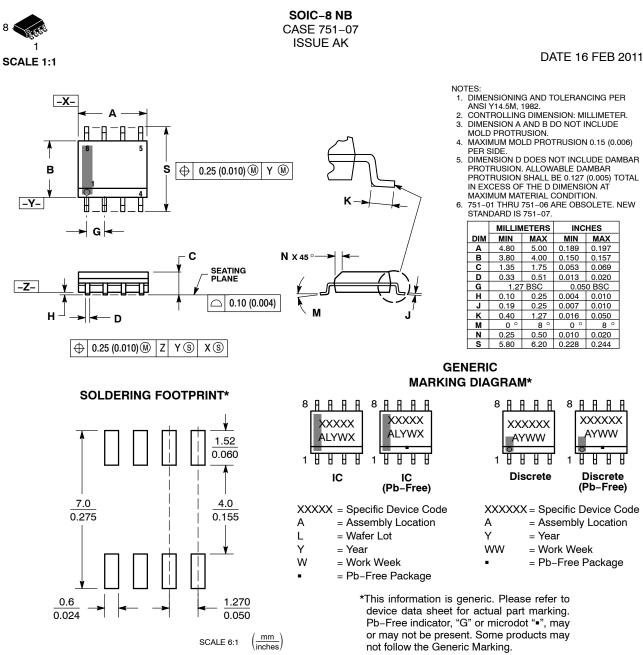

CASE 751-07

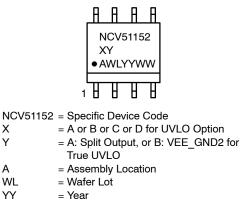

## MARKING DIAGRAM

ww

## **ORDERING INFORMATION**

See detailed ordering and shipping information on page 22 of this data sheet.

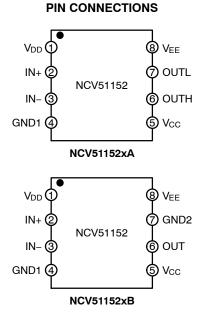

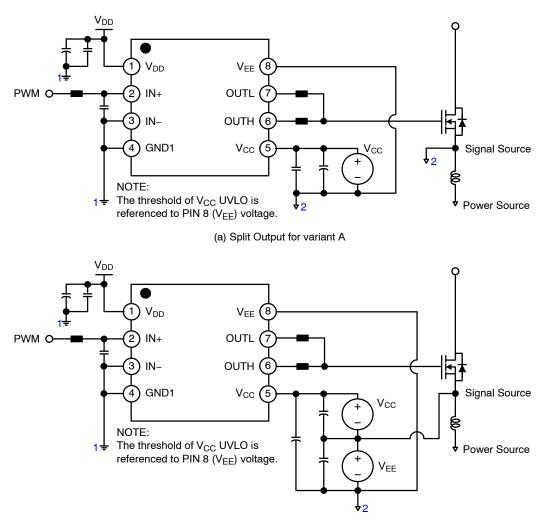

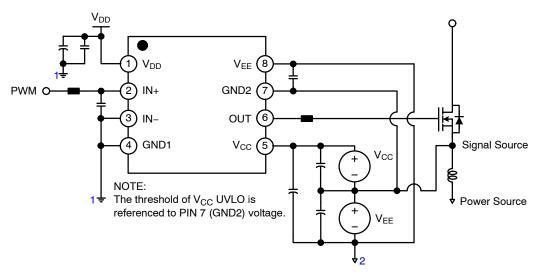

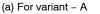

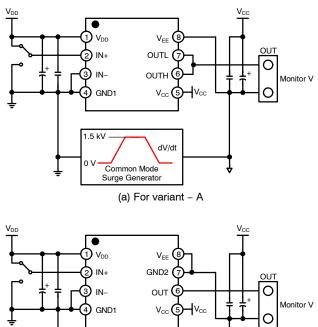

## **TYPICAL APPLICATION CIRCUIT**

(b) Split Output and external negative bias for variant A

(c) External negative bias for variant B

#### Figure 1. Typical Application Schematic

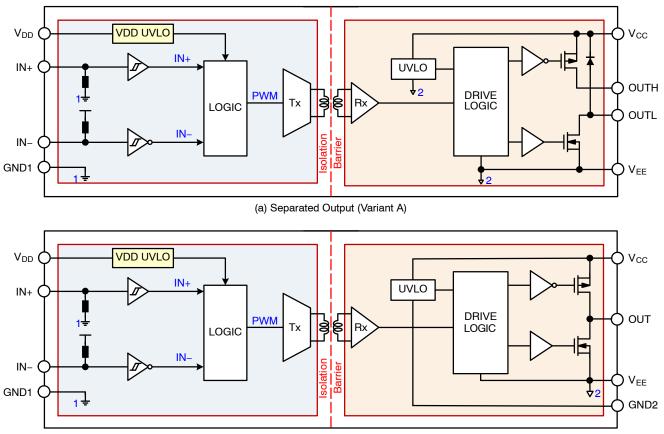

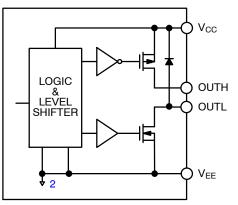

## FUNCTIONAL BLOCK DIAGRAM

(b)  $V_{CC}$  UVLO Referenced to GND2 and external negative bias (Variant B)

Figure 2. Simplified Block Diagram

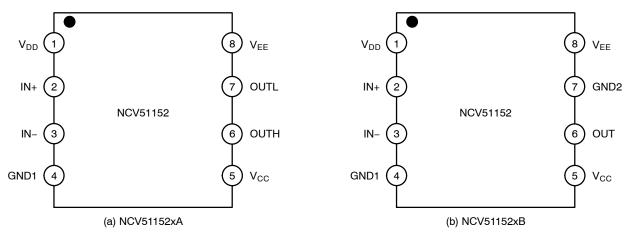

## **PIN CONNECTIONS**

|                 | Pin        | No.        |        |                                                                                                                     |

|-----------------|------------|------------|--------|---------------------------------------------------------------------------------------------------------------------|

| Pin Name        | NCV51152xA | NCV51152xB | I/O    | Description                                                                                                         |

| V <sub>DD</sub> | 1          | 1          | Power  | Input-side Supply Voltage.<br>It is recommended to place a bypass capacitor from V <sub>DD</sub> to GND1.           |

| IN+             | 2          | 2          | Input  | Non-inverting Logic Input with internal pull-down resistor to GND1.                                                 |

| IN-             | 3          | 3          | Input  | Inverting Logic Input with internal pull-up resistor to V <sub>DD</sub> .                                           |

| GND1            | 4          | 4          | Power  | Ground Input-side. (all signals on input-side are referenced to this ground)                                        |

| V <sub>CC</sub> | 5          | 5          | Power  | Positive Output Supply Rail.                                                                                        |

| OUTH            | 6          | 6          | Output | Gate Drive Pull-up Output.                                                                                          |

| OUTL            | 7          | -          | Output | Gate Drive Pull-down Output.                                                                                        |

| GND2            | _          | 7          | Power  | Gate-drive common pin. Connect this pin to the MOSFET source. $V_{\rm CC}$ UVLO with respect to GND2 for variant B. |

| V <sub>EE</sub> | 8          | 8          | Power  | Negative output supply rail for variant B, and ground for variant A.                                                |

## **PIN DESCRIPTION**

#### **INSULATION RATINGS**

| Symbol            | Parameter                                                                                                                 |                        | Value           | Unit             |

|-------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------|------------------|

|                   | Installation Classifications per DIN VDE 0110/1.89 Table 1 Rated                                                          | <150 V <sub>RMS</sub>  | I–IV            |                  |

|                   | Mains Voltage                                                                                                             | <300 V <sub>RMS</sub>  | I–IV            |                  |

|                   |                                                                                                                           | <450 V <sub>RMS</sub>  | I–IV            |                  |

|                   |                                                                                                                           | <600 V <sub>RMS</sub>  | I–IV            |                  |

|                   |                                                                                                                           | <1000 V <sub>RMS</sub> | I–III           |                  |

| CTI               | Comparative Tracking Index (DIN IEC 112/VDE 0303 Part 1)                                                                  |                        | 600             |                  |

|                   | Climatic Classification                                                                                                   |                        | 40/125/21       |                  |

|                   | Pollution Degree (DIN VDE 0110/1.89)                                                                                      |                        | 2               |                  |

| V <sub>PR</sub>   | Input–to–Output Test Voltage, Method b, $V_{IORM} x 1.875 = V_{PR}$ , 100 Test with $t_m = 1$ s, Partial Discharge < 5 pC | 0% Production          | 2250            | V <sub>PK</sub>  |

| VIORM             | Maximum Repetitive Peak Isolation Voltage                                                                                 |                        | 1200            | V <sub>PK</sub>  |

| V <sub>IOWM</sub> | Maximum Working Voltage                                                                                                   |                        | 870             | V <sub>RMS</sub> |

| V <sub>IOTM</sub> | Maximum Transient Isolation Voltage                                                                                       |                        | 6300            | V <sub>PK</sub>  |

| E <sub>CR</sub>   | External Creepage                                                                                                         |                        | 4.0             | mm               |

| E <sub>CL</sub>   | External Clearance                                                                                                        |                        | 4.0             | mm               |

| DTI               | Insulation Thickness                                                                                                      |                        | 17.3            | μm               |

| R <sub>IO</sub>   | Insulation Resistance at T <sub>S</sub> , V <sub>IO</sub> = 500 V                                                         |                        | 10 <sup>9</sup> | Ω                |

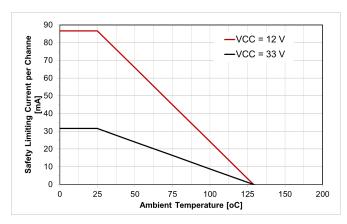

## SAFETY LIMITING VALUE

| Symbol         | Parameter           | Test Condition                                                          | Side   | Value | Unit |

|----------------|---------------------|-------------------------------------------------------------------------|--------|-------|------|

| PS             | Safety Supply Power | $R_{\theta JA} = 100^{\circ}C/W, T_A = 25^{\circ}C, T_J = 150^{\circ}C$ | INPUT  | 0.21  | W    |

|                |                     |                                                                         | OUTPUT | 1.04  | W    |

|                |                     |                                                                         | TOTAL  | 1.25  | W    |

| T <sub>S</sub> | Safety Temperature  |                                                                         |        | 150   | °C   |

#### MAXIMUM RATINGS

| Symbo                         | ol           | Parameter                                          | Min                   | Max                                                                                          | Unit |

|-------------------------------|--------------|----------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------|------|

| V <sub>DD</sub> to G          | ND1          | Power Supply Voltage – Input Side (Note 2)         | -0.3                  | 25                                                                                           | V    |

| V <sub>CC</sub> – GI          | ND2          | Positive Supply Voltage – Driver Side              | -0.3                  | 33                                                                                           | V    |

| VEE – G                       | ND2          | Negative Supply Voltage for Only B Version         | -18                   | 0.3                                                                                          | V    |

| V <sub>CC</sub> – V           | ΈE           | Differential Supply Voltage – Driver Side (Note 3) | -0.3                  | 33                                                                                           | V    |

| OUT to \                      | /EE          | Driver Output Voltage (Note 3)                     | V <sub>EE</sub> - 0.3 | V <sub>CC</sub> + 0.3                                                                        | V    |

| OUT to V<br>Transient for 200 | ,            |                                                    | V <sub>EE</sub> – 2   | V <sub>CC</sub> + 0.3                                                                        | V    |

| IN+, and                      | IN-          | Input Signal Voltages (Note 2)                     | -5                    | V <sub>DD</sub> + 0.3                                                                        | V    |

| TJ                            |              | Junction Temperature                               | -40                   | +150                                                                                         | °C   |

| Τ <sub>S</sub>                |              | Storage Temperature                                | -65                   | +150                                                                                         | °C   |

| Electrostatic                 | HBM (Note 5) | Human Body Model                                   | -                     | 0.3<br>33<br>V <sub>CC</sub> + 0.3<br>V <sub>CC</sub> + 0.3<br>V <sub>DD</sub> + 0.3<br>+150 | kV   |

| Discharge Capability          | CDM (Note 5) | Charged Device Model                               | -                     | 1                                                                                            | kV   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected. 1. Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe

Operating parameters.

- All voltage values are given with respect to GND1 pin.

All voltage values are given with respect to VEE pin.

This parameter verified by design and bench test, not tested in production.

- This balance verified by design and bench test, not tested in production.

This device series incorporates ESD protection and is tested by the following methods: ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114)

ESD Charged Device Model tested per AEC-Q100-011 (EIA/JESD22-C101) Latch up Current Maximum Rating: ≤100 mA per JEDEC standard: JESD78F.

## THERMAL CHARACTERISTICS

| Symbol        | Parameter                                             | Min             | Max  | Unit |

|---------------|-------------------------------------------------------|-----------------|------|------|

| $\theta_{JA}$ | Secondary Thermal Resistance of Junction-Air (Note 6) | Type–A (Note 7) | 100  | °C/W |

|               |                                                       | Type-B (Note 8) | 120  |      |

| $\Psi_{JT}$   | Thermal Characterization Parameter Junction-Case Top  | Type–A (Note 7) | 8    |      |

|               |                                                       | Type-B (Note 8) | 8    |      |

| PD            | Secondary Power Dissipation (Note 6)                  | Type–A (Note 7) | 1.25 | W    |

|               |                                                       | Type-B (Note 8) | 1.04 |      |

6. Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

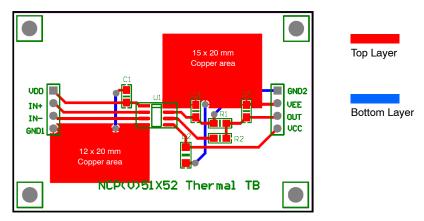

7. As specified for a reference layout shown in Figure 4. The DUT is mounted on a 60 x 40 x 1.6 mm FR4 substrate with an additional heat spreading copper of 240 mm<sup>2</sup>/300 mm<sup>2</sup> (Primary/Secondary). The copper thickness is 1 oz and test conditions is under natural convection or zero air flow.

Figure 4. Reference Layout for the Type-A

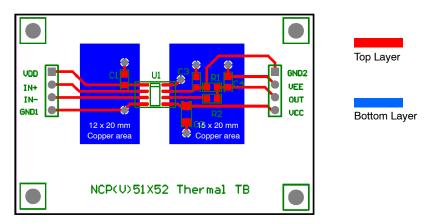

As specified for a reference layout shown in Figure 5. The DUT is mounted on a 60 x 40 x 1.6 mm FR4 substrate with an additional heat spreading copper of 240 mm<sup>2</sup>/300 mm<sup>2</sup> (Primary/Secondary). The copper thickness is 1oz and test conditions is under natural convection or zero air flow.

Figure 5. Reference Layout for the Type-B

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol          | Rating                                                  |                   | Min  | Max             | Unit  |

|-----------------|---------------------------------------------------------|-------------------|------|-----------------|-------|

| V <sub>DD</sub> | Power Supply Voltage – Input Side                       |                   | 3.0  | 20              | V     |

| V <sub>CC</sub> | Power Supply Voltage – Driver Side (Note 9)             | 5-V UVLO Version  | 6.5  | 30              | V     |

|                 |                                                         | 8-V UVLO Version  | 9.5  | 30              | V     |

|                 |                                                         | 12-V UVLO Version | 13.5 | 30              | V     |

|                 |                                                         | 17-V UVLO Version | 18.5 | 30              | V     |

| VEE – GND2      | Negative Supply Voltage for only Variant B (NCV51152xB) | -                 | -15  | 0               | V     |

| V <sub>IN</sub> | Logic Input Voltage at Pins IN+, and IN-                |                   | 0    | V <sub>DD</sub> | V     |

| T <sub>A</sub>  | Ambient Temperature                                     |                   | -40  | +125            | °C    |

| TJ              | Junction Temperature                                    |                   | -40  | +125            | °C    |

| CMTI            | Common Mode Transient Immunity                          |                   | 200  | -               | kV/μs |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

9. All V<sub>CC</sub> UVLO threshold voltages of the variant A and B are given with respect to V<sub>EE</sub> and GND2 pins respectively.

#### **ISOLATION CHARACTERISTICS**

| Symbol                | Parameter                         | Condition                                                                                            | Value            | Unit             |

|-----------------------|-----------------------------------|------------------------------------------------------------------------------------------------------|------------------|------------------|

| VISO, INPUT TO OUTPUT | Input to Output Isolation Voltage | $T_A$ = 25°C, Relative Humidity < 50%, t = 1.0 minute, $I_{I-O}$ < 30 $\mu A,$ 50 Hz (Note 10,11,12) | 3750             | V <sub>RMS</sub> |

| R <sub>ISO</sub>      | Isolation Resistance              | V <sub>I_O</sub> = 500 V (Note 10)                                                                   | 10 <sup>11</sup> | Ω                |

10. Device is considered a two-terminal device: pins 1 to 4 are shorted together and pins 5 to 8 are shorted together.

11.3,750 V<sub>RMS</sub> for 1-minute duration is equivalent to 4,500 V<sub>RMS</sub> for 1-second duration for input to output isolation test, and Impulse Test > 10 ms; sample tested for between channel isolation test.

12. The input-output isolation voltage is a dielectric voltage rating per UL1577. It should not be regarded as an input-output continuous voltage

12. The input–output isolation voltage is a dielectric voltage rating per UL1577. It should not be regarded as an input–output continuous voltage rating. For the continuous working voltage rating, refer to equipment–level safety specification or DIN VDE V 0884–11 Safety and Insulation Ratings Table.

| ELECTRICAL CHARACTERISTICS (V <sub>DD</sub> = 5 V, V <sub>CC</sub> = 15 V, or 20 V (V <sub>EE</sub> = 0 V for NCV51151xB) (Note 15) for typical values |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $T_J = T_A = 25^{\circ}C$ , for min/max values $T_J = -40^{\circ}C$ to +125°C, unless otherwise specified. (Note 15))                                  |  |

| Symbol             | Parameter                                                                  | Condition                                                            | Min | Тур | Max  | Unit |

|--------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------|-----|-----|------|------|

| PRIMARY P          | POWER SUPPLY SECTION (VDD)                                                 |                                                                      | •   |     |      |      |

| I <sub>QVDD</sub>  | V <sub>DD</sub> Quiescent Current                                          | $V_{IN+} = V_{IN-} = 0 V, V_{DD} = 5 V$                              | 500 | 715 | 1000 | μA   |

|                    |                                                                            | $V_{IN+} = V_{IN-} = 0 V, V_{DD} = 15 V$                             | 600 | 870 | 1100 | μA   |

|                    |                                                                            | $V_{IN+} = V_{IN-} = V_{DD}, V_{DD} = 5 V$                           | 500 | 720 | 1000 | μA   |

|                    |                                                                            | $V_{IN+} = V_{IN-} = V_{DD}, V_{DD} = 15 V$                          | 600 | 870 | 1100 | μΑ   |

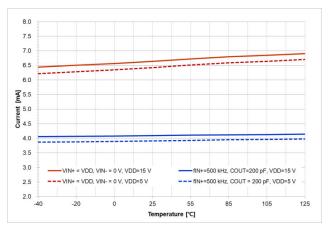

| I <sub>VDD</sub>   | V <sub>DD</sub> Operating Current                                          | $V_{IN+} = V_{DD}, V_{IN-} = 0 V, V_{DD} = 5 V$                      | 4.5 | 6.4 | 8.0  | mA   |

|                    |                                                                            | $V_{IN+} = V_{DD}, V_{IN-} = 0 V, V_{DD} = 15 V$                     | 5.0 | 6.6 | 8.4  | mA   |

|                    |                                                                            | $f_{IN+}$ = 500 kHz, $C_{OUT}$ = 200 pF,<br>V_{DD} = 5 V             | 2.9 | 3.9 | 5.0  | mA   |

|                    |                                                                            | $\rm f_{IN+}$ = 500 kHz, $\rm C_{OUT}$ = 200 pF, $\rm V_{DD}$ = 15 V | 3.0 | 4.1 | 5.2  | mA   |

| V <sub>DDUV+</sub> | V <sub>DD</sub> Supply Under–Voltage<br>Positive–Going Threshold           | V <sub>DD</sub> = Sweep                                              | 2.7 | 2.8 | 2.9  | V    |

| V <sub>DDUV-</sub> | V <sub>DD</sub> Supply Under-Voltage<br>Negative-Going Threshold           | V <sub>DD</sub> = Sweep                                              | 2.6 | 2.7 | 2.8  | V    |

| V <sub>DDHYS</sub> | V <sub>DD</sub> Supply Under-Voltage<br>Lockout Hysteresis                 | V <sub>DD</sub> = Sweep                                              | -   | 0.1 | -    | V    |

| t <sub>VDDUV</sub> | Debounce Time (Note 16)                                                    |                                                                      | -   | -   | 10   | μs   |

| SECONDAF           | RY POWER SUPPLY SECTION                                                    |                                                                      | •   |     |      |      |

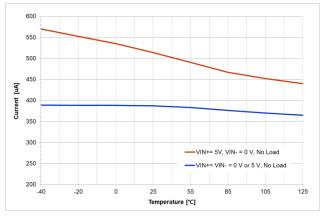

| I <sub>QVCC</sub>  | V <sub>CC</sub> Quiescent Current                                          | $V_{IN+} = V_{IN-} = 0 V \text{ or } 5 V$ , No Load                  | 200 | 385 | 700  | μA   |

|                    |                                                                            | $V_{IN+} = 5 \text{ V}, V_{IN-} = 0 \text{ V}, \text{ No Load}$      | 200 | 507 | 800  | μA   |

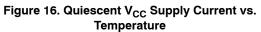

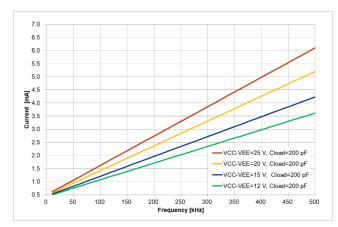

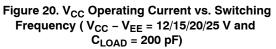

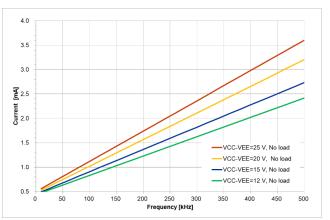

| Ivcc               | V <sub>CC</sub> Operating Current                                          | $f_{\rm IN+}$ = 500 kHz, $C_{\rm OUT}$ = 200 pF, $V_{\rm CC}$ = 15 V | 3.0 | 4.2 | 5.0  | mA   |

|                    |                                                                            | $f_{\rm IN+}$ = 500 kHz, $C_{\rm OUT}$ = 200 pF, $V_{\rm CC}$ = 20 V | 3.7 | 5.2 | 6.2  | mA   |

| VCC UVLO           | THRESHOLD (6-V UVLO VERSION)                                               |                                                                      |     |     |      |      |

| V <sub>CCUV+</sub> | V <sub>CC</sub> Supply Under–Voltage<br>Positive–Going Threshold (Note 13) |                                                                      | 5.7 | 6.0 | 6.4  | V    |

| V <sub>CCUV-</sub> | V <sub>CC</sub> Supply Under–Voltage<br>Negative–Going Threshold           |                                                                      | 5.3 | 5.7 | 6.0  | V    |

| V <sub>CCHYS</sub> | Under-Voltage Lockout Hysteresis                                           |                                                                      | -   | 0.3 | -    | V    |

| tvccuv             | UVLO Filter Debounce Time (Note 16)                                        |                                                                      | -   | -   | 10   | μs   |

| VCC UVLO           | THRESHOLD (8-V UVLO VERSION)                                               | _                                                                    | _   | _   | _    | _    |

| V <sub>CCUV+</sub> | V <sub>CC</sub> Supply Under–Voltage<br>Positive–Going Threshold (Note 13) |                                                                      | 8.2 | 8.7 | 9.2  | V    |

| V <sub>CCUV-</sub> | V <sub>CC</sub> Supply Under-Voltage<br>Negative-Going Threshold           |                                                                      | 7.7 | 8.2 | 8.7  | V    |

| V <sub>CCHYS</sub> | Under-Voltage Lockout Hysteresis                                           |                                                                      | -   | 0.5 | -    | V    |

| t <sub>VCCUV</sub> | UVLO Filter Debounce Time (Note 16)                                        |                                                                      | -   | _   | 10   | μs   |

| VCC UVLO           | THRESHOLD (12-V UVLO VERSION)                                              |                                                                      |     |     |      |      |

| V <sub>CCUV+</sub> | V <sub>CC</sub> Supply Under–Voltage<br>Positive–Going Threshold (Note 13) |                                                                      | 11  | 12  | 13   | V    |

| V <sub>CCUV-</sub> | V <sub>CC</sub> Supply Under-Voltage<br>Negative-Going Threshold           |                                                                      | 10  | 11  | 12   | V    |

| V <sub>CCHYS</sub> | Under-Voltage Lockout Hysteresis                                           |                                                                      | -   | 1.0 | -    | V    |

| t <sub>VCCUV</sub> | UVLO Filter Debounce Time (Note 16)                                        |                                                                      | -   | -   | 10   | μs   |

| Symbol               | Parameter                                                                                                 | Condition                                                                         | Min  | Тур  | Max | Unit |

|----------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------|------|-----|------|

|                      | THRESHOLD (17-V UVLO VERSION)                                                                             |                                                                                   |      |      |     |      |

| V <sub>CCUV+</sub>   | V <sub>CC</sub> Supply Under-Voltage<br>Positive-Going Threshold (Note 13)                                |                                                                                   | 16   | 17   | 18  | V    |

| V <sub>CCUV-</sub>   | V <sub>CC</sub> Supply Under-Voltage<br>Negative-Going Threshold                                          |                                                                                   | 15   | 16   | 17  | V    |

| V <sub>CCHYS</sub>   | Under-Voltage Lockout Hysteresis                                                                          |                                                                                   | _    | 1.0  | -   | V    |

| t <sub>VCCUV</sub>   | UVLO Filter Debounce Time (Note 16)                                                                       |                                                                                   | _    | -    | 10  | μs   |

| LOGIC INPU           | IT SECTION (IN+, AND IN-)                                                                                 |                                                                                   |      |      |     |      |

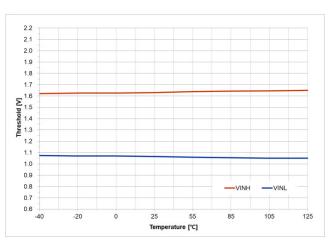

| V <sub>INH</sub>     | High Level Input Voltage                                                                                  |                                                                                   | 1.4  | 1.63 | 2.0 | V    |

| V <sub>INL</sub>     | Low Level Input Voltage                                                                                   |                                                                                   | 0.8  | 1.08 | 1.4 | V    |

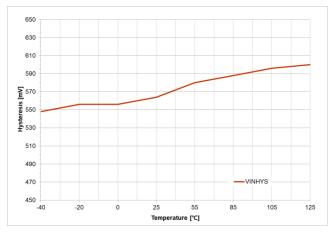

| V <sub>INHYS</sub>   | Input Logic Hysteresis                                                                                    |                                                                                   | -    | 0.55 | -   | V    |

| I <sub>IN+H</sub>    | High Level Logic Input Bias Current at IN+                                                                | V <sub>IN+</sub> = 5 V                                                            | 33   | 40   | 52  | μA   |

| I <sub>IN+L</sub>    | Low Level Logic Input Bias Current at IN-                                                                 | V <sub>IN+</sub> = GND1                                                           | _    | -    | 1.0 | μA   |

| I <sub>IN-H</sub>    | High Level Logic Input Bias Current at IN+                                                                | V <sub>IN-</sub> = 5 V                                                            | -1.0 | -    | -   | μA   |

| I <sub>IN-L</sub>    | Low Level Logic Input Bias Current at IN-                                                                 | V <sub>IN-</sub> = GND1                                                           | -52  | -40  | -33 | μA   |

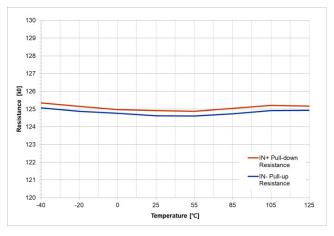

| R <sub>IN</sub>      | Logic Input Pull-Up/Down Resistance                                                                       |                                                                                   | 95   | 125  | 155 | kΩ   |

| SHORT CIR            | CUIT SECTION                                                                                              |                                                                                   |      |      |     |      |

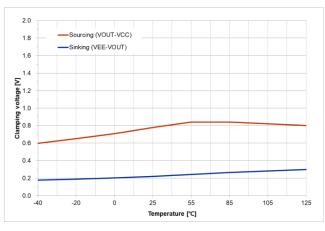

| V <sub>CLP-OUT</sub> | Clamping Voltage, Sourcing<br>(V <sub>OUTH</sub> –V <sub>CC</sub> or V <sub>OUT</sub> – V <sub>CC</sub> ) | IN+ = High, IN- = Low, $t_{CLAMP}$ = 10 $\mu s$ $I_{OUTH}$ or $I_{OUT}$ = 500 mA  | -    | 0.7  |     | V    |

|                      | Clamping Voltage, Sinking<br>(V <sub>EE</sub> – V <sub>OUTL</sub> or V <sub>EE</sub> – V <sub>OUT</sub> ) | IN+ = Low, IN- = High, $t_{CLAMP}$ = 10 $\mu s$ $I_{OUTH}$ or $I_{OUT}$ = –500 mA | -    | 0.24 | 0.5 | V    |

| GATE DRIVE           | ESECTION                                                                                                  |                                                                                   |      |      |     |      |

| I <sub>OUT+</sub>    | Source Peak Current (Note 16)                                                                             | $V_{IN+}$ = 5 V, PW $\leq$ 5 $\mu$ s                                              | 2.6  | 4.5  | -   | Α    |

| I <sub>OUT-</sub>    | Sink Peak Current (Note 16)                                                                               | $V_{IN+} = 0 \text{ V}, \text{ PW} \le 5 \ \mu \text{s}$                          | 7.0  | 9.0  | -   | Α    |

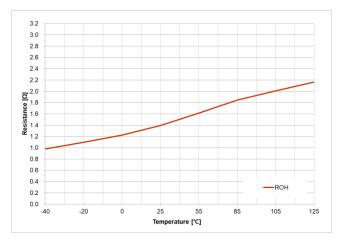

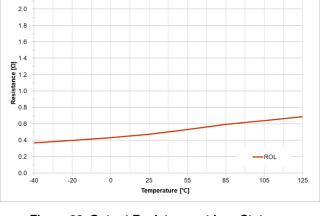

| R <sub>OH</sub>      | Output Resistance at High State                                                                           | I <sub>OUTH</sub> = 100 mA                                                        | _    | 1.4  | 2.8 | Ω    |

| R <sub>OL</sub>      | Output Resistance at Low State                                                                            | I <sub>OUTL</sub> = 100 mA                                                        | -    | 0.5  | 1.0 | Ω    |

| V <sub>OH</sub>      | High Level Output Voltage (V <sub>CC</sub> – V <sub>OUT</sub> )                                           | I <sub>OUTH</sub> = 100 mA                                                        | -    | 140  | 280 | mV   |

| V <sub>OL</sub>      | Low Level Output Voltage (V <sub>OUT</sub> – V <sub>EE</sub> )                                            | I <sub>OUTL</sub> = 100 mA                                                        | _    | 50   | 100 | mV   |

| ELECTRICAL CHARACTERISTICS (V <sub>DD</sub> = 5 V, V <sub>CC</sub> = 15 V, or 20 V (V <sub>EE</sub> = 0 V for NCV51151xB) (Note 15) for typical values |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $T_J = T_A = 25^{\circ}C$ , for min/max values $T_J = -40^{\circ}C$ to +125°C, unless otherwise specified. (Note 15)) (continued)                      |  |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

13. All V<sub>CC</sub> UVLO threshold voltages are given with respect to GND2 pin. 14. Performance guaranteed over the indicated operating temperature range by design and/or characterization tested at  $T_J = T_A = 25^{\circ}$ C. 15. V<sub>CC</sub> = 15 V is used for the test condition of 5–V, and 8–V UVLO, V<sub>CC</sub> = 20 V is used for 12–V and 17–V UVLO. 16. These parameters verified by bench test only and not tested in production

## DYNAMIC ELECTRICAL CHARACTERISTICS

| Symbol                   | Parameter                                                        | Condition                  | Min | Тур | Max | Unit |

|--------------------------|------------------------------------------------------------------|----------------------------|-----|-----|-----|------|

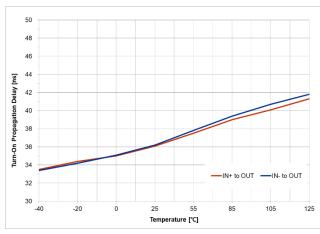

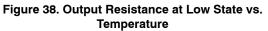

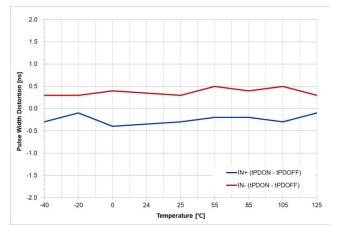

| t <sub>PDON</sub>        | Turn-On Propagation Delay from IN to OUT                         | C <sub>LOAD</sub> = 0 nF   | 20  | 36  | 55  | ns   |

| t <sub>PDOFF</sub>       | Turn-Off Propagation Delay from IN to OUT                        |                            | 20  | 36  | 55  | ns   |

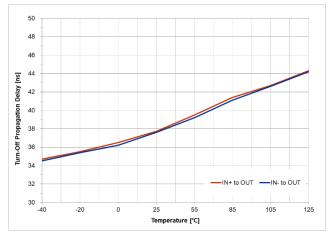

| t <sub>PWD</sub>         | Pulse Width Distortion (t <sub>PDON</sub> – t <sub>PDOFF</sub> ) |                            | -5  | -   | 5   | ns   |

| t <sub>SK(PP)</sub>      | Propagation Part-to-part Skew (Note 17)                          |                            | -20 | -   | 20  | ns   |

| t <sub>VPOR to OUT</sub> | Power-up Delay from the V <sub>POR</sub> to Output (Note 17)     | See the Figure 47          | -   | 18  | -   | μs   |

| t <sub>R</sub>           | Turn-On Rise Time                                                | C <sub>LOAD</sub> = 1.8 nF | -   | 12  | 22  | ns   |

| t <sub>F</sub>           | Turn-Off Fall Time                                               | C <sub>LOAD</sub> = 1.8 nF | -   | 8.3 | 22  | ns   |

| t <sub>PW</sub>          | Minimum Input Pulse Width that Change Output State               | C <sub>LOAD</sub> = 0 nF   | -   | 15  | 35  | ns   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

17. These parameters verified by bench test only and not tested in production

## INSULATION CHARACTERISTICS CURVES

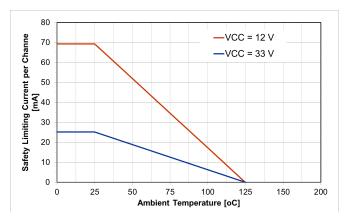

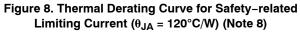

Figure 7. Thermal Derating Curve for Safety–related Limiting Power ( $\theta_{JA} = 100^{\circ}$ C/W) (Note 7)

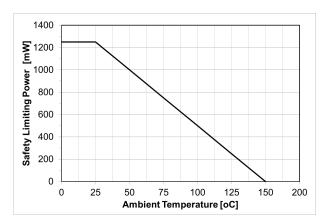

Figure 9. Thermal Derating Curve for Safety–related Limiting Power ( $\theta_{JA}$  = 120°C/W) (Note 8)

## **TYPICAL CHARACTERISTICS**

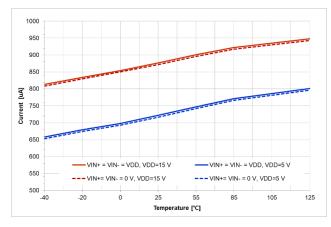

Figure 10. V<sub>DD</sub> Quiescent Current vs. Temperature

Figure 11. V<sub>DD</sub> Quiescent Current vs. Temperature

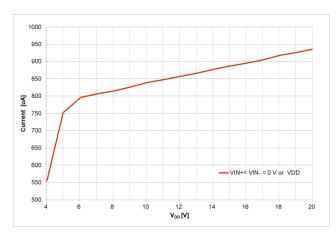

Figure 12. V<sub>DD</sub> Quiescent Current vs. V<sub>DD</sub>

6

5

**[**4

Current 3

2

0

10

20

30

40

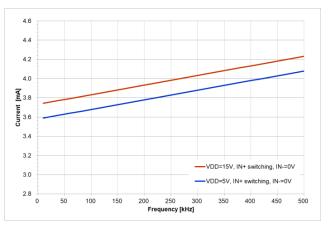

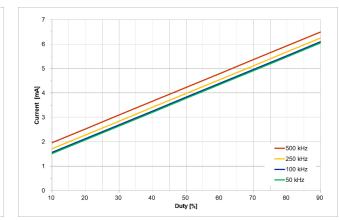

Figure 13. V<sub>DD</sub> Operating Current vs. Switching Frequency

50

Duty [%]

60

70

-500 kHz

250 kHz

100 kHz

50 kHz

90

80

Figure 17. V<sub>CC</sub> Operating Current vs. Temperature

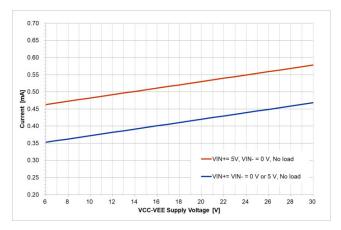

Figure 18. Quiescent  $V_{CC}$  Supply Current vs.  $V_{CC}$  Supply Voltage

Figure 19. V<sub>CC</sub> Operating Current vs. Switching Frequency (  $V_{CC}$  –  $V_{EE}$  = 12/15/20/25 V and No Load)

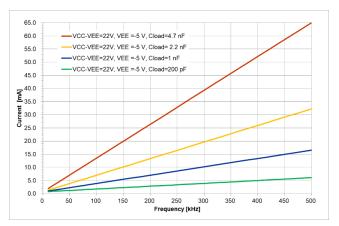

Figure 21. V<sub>CC</sub> Operating Current vs. Switching Frequency (V<sub>CC</sub> – V<sub>EE</sub> = 20 V and Different C<sub>LOAD</sub>)

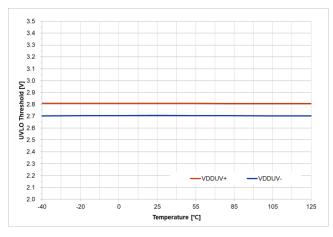

Figure 22. V<sub>DD</sub> UVLO vs. Temperature

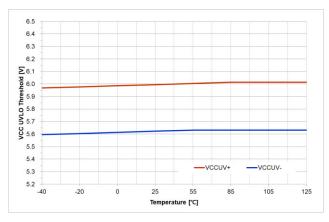

Figure 24. V<sub>CC</sub> 6–V UVLO Threshold vs. Temperature

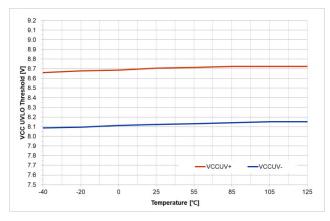

Figure 26. V<sub>CC</sub> 8–V UVLO Threshold vs. Temperature

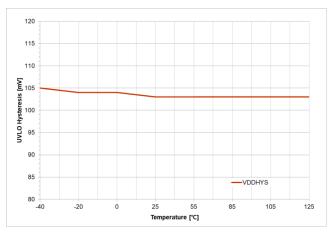

Figure 23.  $V_{DD}$  UVLO Hysteresis vs. Temperature

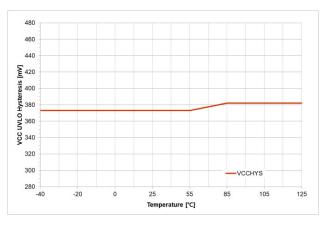

Figure 25. V<sub>DD</sub> 6–V UVLO Hysteresis vs. Temperature

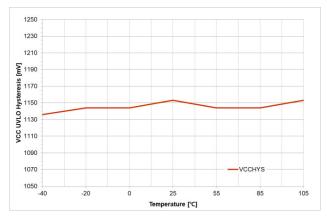

Figure 27. V<sub>DD</sub> 8–V UVLO Hysteresis vs. Temperature

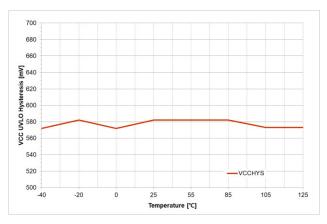

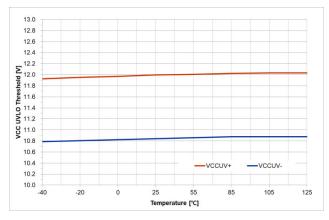

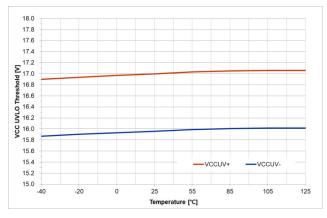

Figure 28. V<sub>CC</sub> 12–V UVLO Threshold vs. Temperature

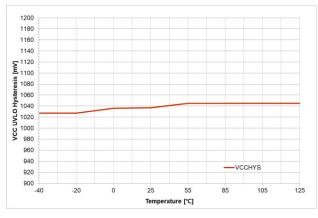

Figure 29. V<sub>CC</sub> 12–V UVLO Hysteresis vs. Temperature

Figure 30. V<sub>CC</sub> 17–V UVLO Threshold vs. Temperature

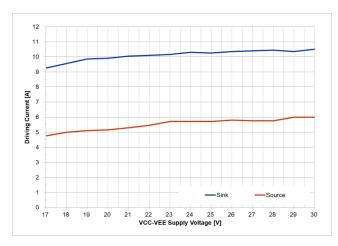

Figure 32. Figure 32. Output Current vs. V<sub>CC</sub> Supply Voltage

Figure 31. V<sub>CC</sub> 17–V UVLO Hysteresis vs. Temperature

Figure 33. Input Logic Threshold vs. Temperature

## **TYPICAL CHARACTERISTICS (CONTINUED)**

Figure 34. Input Logic Hysteresis vs. Temperature

Figure 35. Logic Input Pull-Up/Down Resistance vs. Temperature

Figure 36. Clamping Voltage vs. Temperature

2.2

Figure 37. Output Resistance at High State vs. Temperature

Figure 40. Turn-off Propagation Delay vs. Temperature (C<sub>LOAD</sub> = 0 nF)

Figure 42. Pulse Width Distortion vs. Temperature (CLOAD = 0 nF)

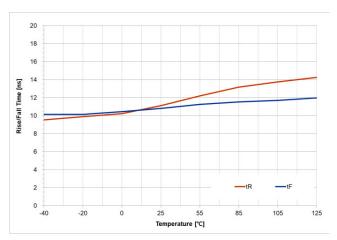

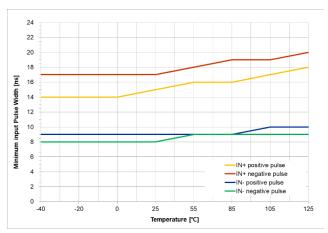

Figure 41. Rise/Fall Time vs. Temperature  $(C_{LOAD} = 1.8 \text{ nF})$

Figure 43. Minimum Input Pulse Width vs. Temperature

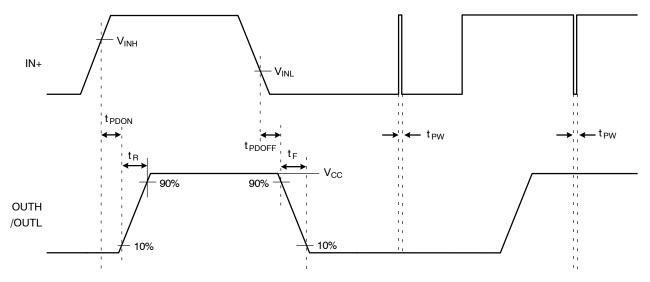

## PARAMETER MEASUREMENT DEFINITION

#### **Switching Time Definitions**

Figure 44 shows the switching time waveforms definitions of the turn-on  $(t_{PDON})$  and turn-off  $(t_{PDOFF})$

propagation delay times among the driver's input signal IN+ and output signal OUT. The typical values of the propagation delay ( $t_{PDON}$ ,  $t_{PDOFF}$ ), pulse width distortion ( $t_{PWD}$ ) and delay matching between channels times are specified in the electrical characteristics table.

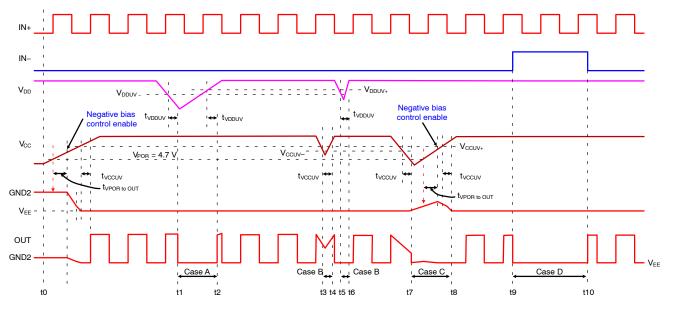

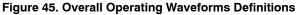

#### Input to Output Operation Definitions

The NCV51152 provides important protection functions such as independent under-voltage lockout for gate driver. Figure 45 shows an overall input to output timing diagram. Under-Voltage Lockout protection on the primary- and secondary-sides power supplies events in the CASE-A, B and C and the gate driver output (OUT) is immediately turn-off when two input signal (IN+ and IN-) are HIGH at same time in the CASE-D.

## **PROTECTION FUNCTION**

The NCV51152 provides the protection features include Under–Voltage Lockout (UVLO) of power supplies on primary–side ( $V_{DD}$ ), and secondary–side ( $V_{CC}$ ).

#### Under-Voltage Lockout Protection V<sub>DD</sub> and V<sub>CC</sub>

The NCV51152 provides the Under–Voltage Lockout (UVLO) protection function for  $V_{DD}$  in primary–side and gate drive output for  $V_{CC}$  in secondary–side as shown in Figure 46. The gate driver is running when the  $V_{DD}$  supply voltage is greater than the specified under–voltage lockout threshold voltage (e.g. typically 2.8 V).

In addition, gate output driver has an under-voltage lockout protection (UVLO) function in secondary-side. (e.g.  $V_{CC}$ ).

The variant A and B need to be greater than specified UVLO threshold level with respect to  $V_{EE}$  and GND2 respectively to let the output operate per input signal. The typical  $V_{CC}$  UVLO threshold voltage levels for each option respectively as are per Table 1.

|   |        | V <sub>CC</sub> UVLO | V <sub>CC</sub> UVLO |           |      |

|---|--------|----------------------|----------------------|-----------|------|

| C | Option | Threshold            | Variant A            | Variant B | Unit |

|   | 5-V    | 6.0                  | $V_{EE}$             | GND2      | V    |

|   | 8-V    | 8.7                  | V <sub>EE</sub>      | GND2      | V    |

| Γ | 12–V   | 12                   | V <sub>EE</sub>      | GND2      | V    |

|   | 17–V   | 17                   | V <sub>EE</sub>      | GND2      | V    |

Figure 46. Timing Chart Under-Voltage Lockout Protection

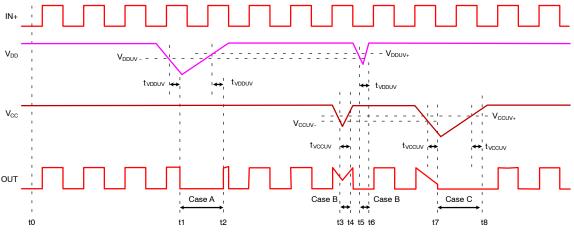

#### Power-up V<sub>CC</sub> UVLO Delay to OUTPUT

To provide a variety of Under–Voltage Lockout (UVLO) thresholds NCV51152 has a power–up delay time during initial VCC start–up or after POR event.

Before the gate driver is ready to deliver a proper output state, there is a power-up delay time from the  $V_{CC}$  power-on reset (POR) threshold to output and it is defined as  $t_{VPOR \ to \ OUT}$ . (e.g. typically18  $\mu$ s). Figure 47 shows the  $V_{CC}$  power-up UVLO delay time diagram.

Figure 47. V<sub>CC</sub> Power-up UVLO Delay Time

## FUNCTIONAL MODES TABLE

Table 2 and Table 3 shows the functional modes for the NCV51152 variant A and B assuming  $V_{DD}$  and  $V_{CC}$  are in the recommended range.

| Ing         | but         | Gate Drive Output |      |  |

|-------------|-------------|-------------------|------|--|

| IN+         | IN-         | OUTH              | OUTL |  |

| LOW         | X (Note 18) | Hi–Z              | LOW  |  |

| X (Note 18) | HIGH        | Hi–Z              | LOW  |  |

| HIGH        | LOW         | HIGH              | Hi–Z |  |

#### Table 2. FUNCTIONAL MODES FOR THE VARIANT A

Table 3. FUNCTIONAL MODES FOR THE VARIANT B

| Ing         | Gate Drive Output |      |

|-------------|-------------------|------|

| IN+         | IN-               | OUT  |

| LOW         | X (Note 18)       | LOW  |

| X (Note 18) | HIGH              | LOW  |

| HIGH        | LOW               | HIGH |

18.X: Don't care

## **APPLICATION INFORMATION**

This section provides application guidelines when using the NCV51152.

#### Power Supply Recommendations

The NCV51152 variant A and B are designed to support unipolar or bipolar power supply respectively.

• In Unipolar power supply the driver is typically supplied with a positive voltage at  $V_{CC}$ . For operation with unipolar supply, the  $V_{CC}$  supply is connected to 15 V with respect to  $V_{EE}$  pin for IGBTs and MOSFET, and 20 V for SiC MOSFETs. (variant A)

In bipolar power supply the driver is typically supplied of the V<sub>CC</sub> and V<sub>EE</sub> output supplies for bipolar operation are 15 V and –8 V with respect to GND2 for IGBTs and 20 V and –5 V for SiC MOSFETs. Negative power supply prevents the power device from unintentionally turning on because of current induced from the Miller effect. (variant B)

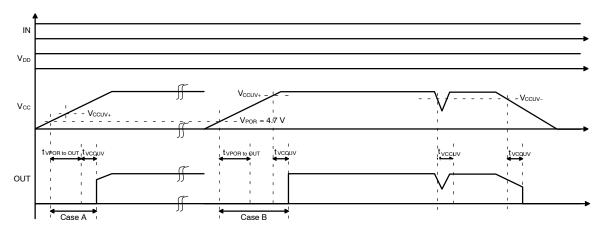

#### Input Stage

Figure 48. Schematic of Input Stage

The input signal pins (IN+, and IN–) of the NCV51152 are based on the TTL compatible input–threshold logic that is independent of the  $V_{DD}$  supply voltage.

The logic level compatible input provides a typically HIGH and LOW threshold of 1.6 V and 1.1 V respectively. The input signal pins impedance is 125 k $\Omega$  typically and the IN+ pin is pulled to GND1 pin and IN- pin is pulled to V<sub>DD</sub> pin as shown in Figure 48. For non-inverting input logic input signal is applied to IN+ while the IN- input can be used as an enable function. If IN- is pulled HIGH, the driver output remains LOW state, regardless of the state of IN+. To enable the driver output, IN- should be tied to GND1 through a few ten k $\Omega$  resistor (e.g.10 k $\Omega$ ) or can be used as an active LOW enable pull down.

- Non-inverting input IN+ controls the driver output while inverting input IN- is set to LOW

- Inverting input IN- controls the driver output while non-inverting input IN+ is set to HIGH

An RC filter is recommended to be added on the input signal pins to reduce the impact of system noise and ground bounce, the time constant of the RC filter as shown in Figure 48. Such a filter should use an  $R_{IN}$  in the range of 0  $\Omega$  to 100  $\Omega$  and a  $C_{IN}$  between 10 pF and 100 pF.

The V<sub>DD</sub> input power supply supports a wide voltage range from 3 V to 20 V and the V<sub>CC</sub> output supply supports a voltage range from 6.5 V to 30 V. The  $V_{CC}$  local bypass capacitor should be placed between the  $V_{CC}$  and  $V_{EE}$  pins with a value of at least ten times the gate capacitance, and an additional capacitor 100-nF in parallel for device biasing and both capacitors located as close to the device as possible. A low ESR, ceramic surface mount capacitors are recommended. In additional, for the negative bias supply capacitor should be placed between GND2 and V<sub>EE</sub> pins with a value of at least few hundred nanofarads. (variant B). Similarly, the V<sub>DD</sub> bypass capacitor should also be placed between the V<sub>DD</sub> and GND1 pins for input logic power supply. We recommend using 2 capacitors; at least 100 nF ceramic surface-mount capacitor with few microfarads added in parallel and both capacitors also located as close to the pins of the device as shown in Figure 48.

### **Output Stage**

The NCV51152 have different output stages of the variant A and B as shown in Figure 49.

For the variant A is designed to support separate source (OUTH) and sink (OUTL) outputs. This scheme allows a single resistor between each pin and the MOSFET gate to independently control gate ringing as well as fine tuning dV<sub>DS</sub>/dT turn-on and turn-off transitions present on the MOSFET drain-source voltage.

(b) For variant - B

Figure 49. Schematic of Output Stage

The output impedance of the pull up and pull down switches shall be able to provide about +4.5 A and -9 A peak currents typical at 25°C and the minimum sink and source peak currents are -7 A sink and +2.6 A source at 125°C.

#### **Common Mode Transient Immunity Testing**

Figure 50 shows a simplified diagram of the Common Mode Transient Immunity (CMTI) testing configuration for each the variant A and B. CMTI is the maximum sustainable common-mode voltage slew rate while maintaining the correct output. CMTI applies to both rising and falling common-mode voltage edges. CMTI is tested with the transient generator connected between GND1 and V<sub>EE</sub>.  $(V_{CM} = 1500 \text{ V}).$

Figure 50. Common Mode Transient Immunity Test Circuit

#### **PCB Layout Guideline**

To improve the switching characteristics and efficiency of design, the following should be considered before beginning a PCB layout.

#### **Component Placement**

- Keep the input/output traces as short as possible. Minimize influence of the parasitic inductance and capacitance on the layout. (To maintain low signal-path inductance, avoid using via.)

- Placement and routing for supply bypass capacitors for V<sub>DD</sub>, V<sub>CC</sub> and V<sub>EE</sub>, and gate resistors need to be located as close as possible to the gate driver.

- The gate driver should be located switching device as close as possible to decrease the trace inductance and avoid output ringing.

#### Grounding Consideration

• Have a solid ground plane underneath the high-speed signal layer.

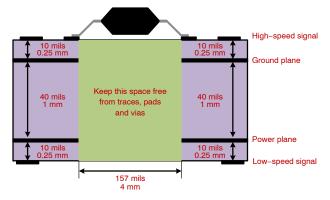

#### High-Voltage (VISO) Consideration

• To ensure isolation performance between the primary and secondary side, any PCB traces or copper should be not placed under the driver device as shown in Figure 51. A PCB cutout is recommended to avoid contamination that may impair the isolation performance of NCV51152.

Figure 51. Recommended Layer Stack

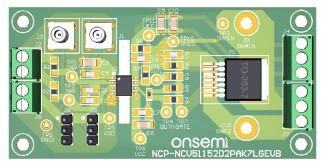

Figure 52 shows the 3D layout of the top view of an evaluation board. The component's location of the PCB  $\,$

cutout between primary and secondary sides ensures isolation performance.

Figure 52. 3–D PCB View

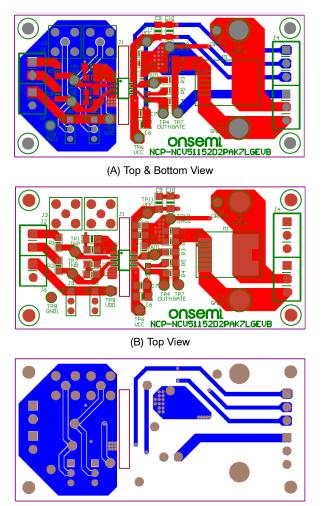

Figure 53 shows the top and bottom layer traces and copper of printed circuit board layout.

(C) Bottom View

Figure 53. Printed Circuit Board

## **ORDERING INFORMATION**

| Device          | Description                                                      | Package                | UVLO | OUTPUT/UVLO/NEG | Shipping <sup>†</sup> |

|-----------------|------------------------------------------------------------------|------------------------|------|-----------------|-----------------------|

| NCV51152AADR2G* | High current single<br>isolated MOS driver                       | SOIC-8 NB<br>(Pb-Free) | 6 V  | Split OUTPUT    | 2500 / Tape & Reel    |

| NCV51152BADR2G  |                                                                  | SOIC-8 NB<br>(Pb-Free) | 8 V  |                 | 2500 / Tape & Reel    |

| NCV51152CADR2G  |                                                                  | SOIC-8 NB<br>(Pb-Free) | 12 V |                 | 2500 / Tape & Reel    |

| NCV51152DADR2G* |                                                                  | SOIC-8 NB<br>(Pb-Free) | 17 V |                 | 2500 / Tape & Reel    |

| NCV51152ABDR2G* | High current single<br>isolated MOS driver with<br>true VCC UVLO | SOIC-8 NB<br>(Pb-Free) | 6 V  | TRUE VCC UVLO   | 2500 / Tape & Reel    |

| NCV51152BBDR2G* |                                                                  | SOIC-8 NB<br>(Pb-Free) | 8 V  |                 | 2500 / Tape & Reel    |

| NCV51152CBDR2G* |                                                                  | SOIC-8 NB<br>(Pb-Free) | 12 V |                 | 2500 / Tape & Reel    |

| NCV51152DBDR2G* |                                                                  | SOIC-8 NB<br>(Pb-Free) | 17 V |                 | 2500 / Tape & Reel    |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

\*Option on demand

# onsemí

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

## STYLES ON PAGE 2

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SOIC-8 NB   |                                                                                                                                                                                     | PAGE 1 OF 2 |  |  |

| onsemi and ONSEMi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others. |             |                                                                                                                                                                                     |             |  |  |

#### SOIC-8 NB CASE 751-07 **ISSUE AK**

STYLE 1: PIN 1. EMITTER COLLECTOR 2. 3. COLLECTOR 4. EMITTER 5. EMITTER BASE 6. 7 BASE EMITTER 8. STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN DRAIN 4. GATE 5. 6. GATE SOURCE 7. 8. SOURCE STYLE 9: PIN 1. EMITTER, COMMON COLLECTOR, DIE #1 COLLECTOR, DIE #2 2. З. EMITTER, COMMON 4. 5. EMITTER, COMMON 6 BASE. DIE #2 BASE, DIE #1 7. 8. EMITTER, COMMON STYLE 13: PIN 1. N.C. 2. SOURCE 3 GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. DRAIN 8. STYLE 17: PIN 1. VCC 2. V2OUT V10UT З. TXE 4. 5. RXE 6. VFF 7. GND 8. ACC STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3 CATHODE 3 CATHODE 4 4. 5. CATHODE 5 6. COMMON ANODE COMMON ANODE 7. 8. CATHODE 6 STYLE 25: PIN 1. VIN 2 N/C REXT З. 4. GND 5. IOUT IOUT 6. IOUT 7. 8. IOUT STYLE 29: BASE, DIE #1 PIN 1. 2 EMITTER, #1 BASE, #2 З. EMITTER, #2 4. 5 COLLECTOR, #2 COLLECTOR, #2 6.

STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 COLLECTOR, #2 3. 4 COLLECTOR, #2 BASE, #2 5. EMITTER, #2 6. 7 BASE #1 EMITTER, #1 8. STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN SOURCE 4. SOURCE 5. 6. GATE GATE 7. 8. SOURCE STYLE 10: GROUND PIN 1. BIAS 1 OUTPUT 2. З. GROUND 4. 5. GROUND 6 BIAS 2 INPUT 7. 8. GROUND STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3 P-SOURCE P-GATE 4. P-DRAIN 5 6. P-DRAIN N-DRAIN 7. N-DRAIN 8. STYLE 18: PIN 1. ANODE ANODE 2. SOURCE 3. GATE 4. 5. DRAIN 6 DRAIN CATHODE 7. CATHODE 8. STYLE 22 PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3 COMMON CATHODE/VCC 4. I/O LINE 3 COMMON ANODE/GND 5. 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND STYLE 26: PIN 1. GND 2 dv/dt З. ENABLE 4. ILIMIT 5. SOURCE SOURCE 6. SOURCE 7. 8. VCC STYLE 30: DRAIN 1 PIN 1. DRAIN 1 2 GATE 2 З. SOURCE 2 4 SOURCE 1/DRAIN 2 SOURCE 1/DRAIN 2 5.

6.

7.

8 GATE 1

SOURCE 1/DRAIN 2

STYLE 3: PIN 1. DRAIN, DIE #1 DRAIN, #1 2. DRAIN, #2 З. DRAIN, #2 4. GATE, #2 5. SOURCE, #2 6. 7 GATE #1 8. SOURCE, #1 STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS THIRD STAGE SOURCE GROUND З. 4. 5. DRAIN 6. GATE 3 SECOND STAGE Vd 7. FIRST STAGE Vd 8. STYLE 11: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. З. GATE 2 4. 5. DRAIN 2 6. DRAIN 2 DRAIN 1 7. 8. DRAIN 1 STYLE 15: PIN 1. ANODE 1 2. ANODE 1 ANODE 1 3 ANODE 1 4. 5. CATHODE, COMMON CATHODE, COMMON CATHODE, COMMON 6. 7. CATHODE, COMMON 8. STYLE 19: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 MIRROR 1 8. STYLE 23: PIN 1. LINE 1 IN COMMON ANODE/GND COMMON ANODE/GND 2. 3 LINE 2 IN 4. LINE 2 OUT 5. COMMON ANODE/GND COMMON ANODE/GND 6. 7. 8. LINE 1 OUT STYLE 27: PIN 1. ILIMIT OVI O 2 UVLO З. 4. INPUT+ 5. 6. SOURCE SOURCE SOURCE 7. 8 DRAIN

#### DATE 16 FEB 2011

STYLE 4: PIN 1. 2. ANODE ANODE ANODE З. 4. ANODE ANODE 5. 6. ANODE 7 ANODE COMMON CATHODE 8. STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 З. BASE #2 COLLECTOR, #2 4. COLLECTOR, #2 5. 6. EMITTER, #2 EMITTER, #1 7. 8. COLLECTOR, #1 STYLE 12: PIN 1. SOURCE SOURCE 2. 3. GATE 4. 5. DRAIN 6 DRAIN DRAIN 7. 8. DRAIN STYLE 16 EMITTER, DIE #1 PIN 1. 2. BASE, DIE #1 EMITTER, DIE #2 3 BASE, DIE #2 4. 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 COLLECTOR, DIE #1 7. COLLECTOR, DIE #1 8. STYLE 20: PIN 1. SOURCE (N) GATE (N) SOURCE (P) 2. 3. 4. GATE (P) 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 24: PIN 1. BASE EMITTER 2. 3 COLLECTOR/ANODE COLLECTOR/ANODE 4. 5. CATHODE 6. CATHODE COLLECTOR/ANODE 7. 8. COLLECTOR/ANODE STYLE 28: PIN 1. SW\_TO\_GND 2. DASIC OFF DASIC\_SW\_DET З. 4. GND 5. 6. V MON VBULK 7. VBULK 8 VIN

| DOCUMENT NUMBER: | 98ASB42564B Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |             |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|--|--|

| DESCRIPTION:     | SOIC-8 NB                                                                                                                                                                                       |  | PAGE 2 OF 2 |  |  |

|                  |                                                                                                                                                                                                 |  |             |  |  |

onsem and of isor in are trademarks or semiconductor compension instructions, the do onsem or its subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced stat purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

7.

8

COLLECTOR, #1

COLLECTOR, #1

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent\_Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at <u>www.onsemi.com/support/sales</u>