JANUARY 2001 REV. P1.1.2

#### GENERAL DESCRIPTION

**XY** EXAR

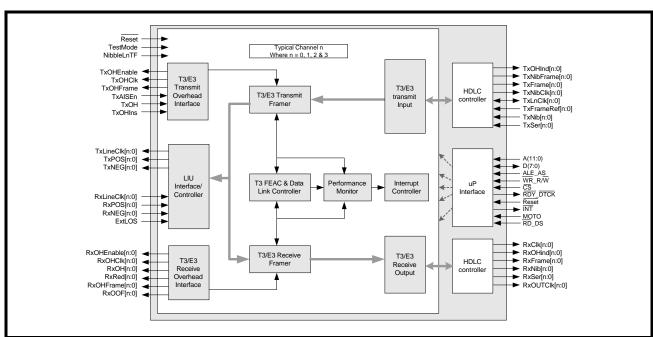

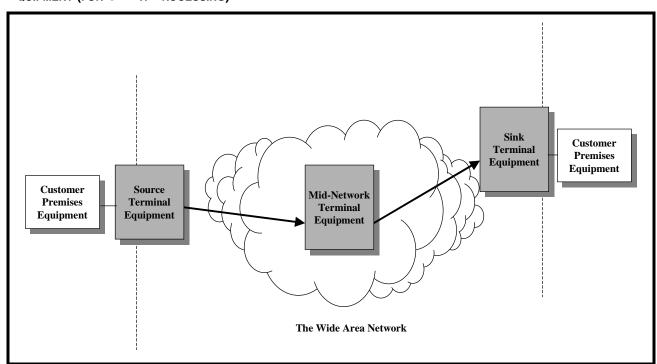

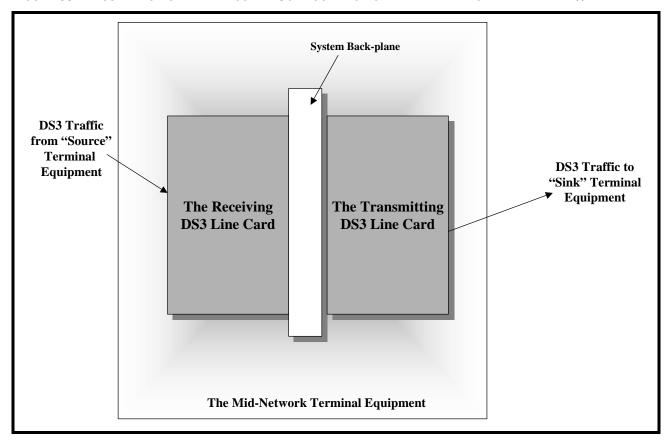

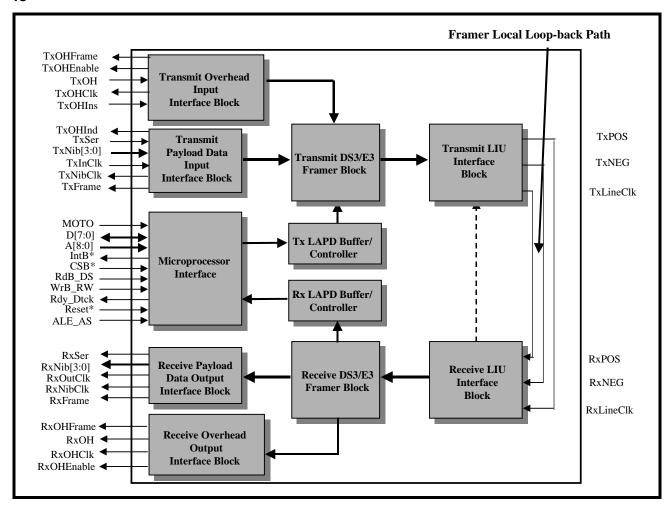

The XRT72L54, 4 Channel DS3/E3 Framer IC is designed to accept "User Data" from the Terminal Equipment and insert this data into the "payload" bit-fields within an "outbound" DS3/E3 Data Stream. Further, the Framer IC is also designed to receive an "inbound" DS3/E3 Data Stream (from the Remote Terminal Equipment) and extract out the "User Data".

The XRT72L54 DS3/E3 Framer device is designed to support full-duplex data flow between Terminal Equipment and an LIU (Line Interface Unit) IC. The Framer Device will transmit, receive and process data in the DS3-C-bit Parity, DS3-M13, E3-ITU-T G.751 and E3-ITU-T G.832 Framing Formats.

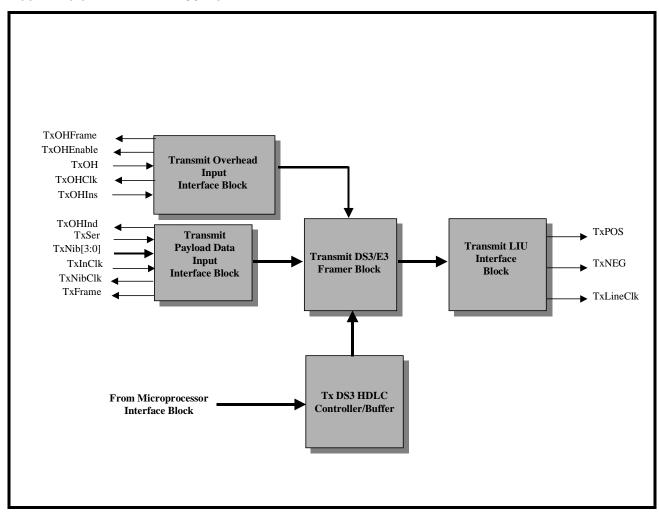

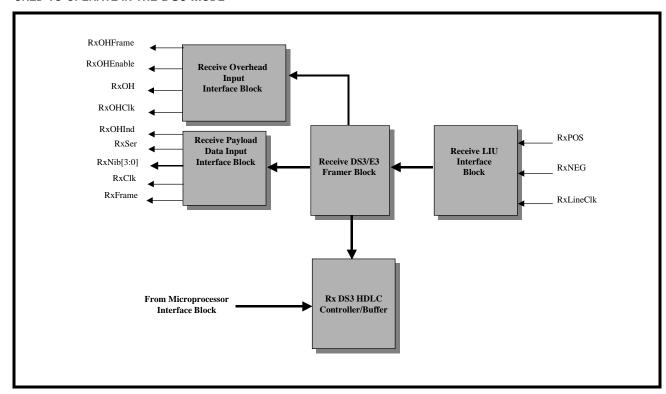

The XRT72L54 DS3/E3 Framer IC consists of Four Transmit sections, Four Receiver sections, Four Performance Monitor Sections and a Microprocessor interface.

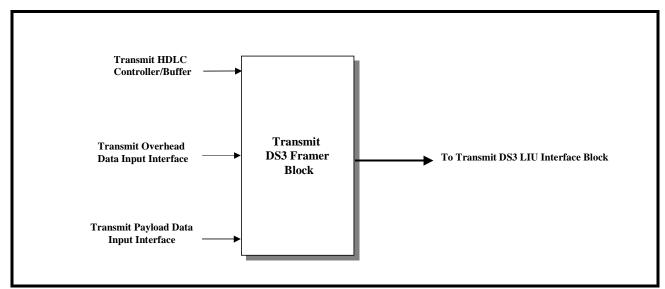

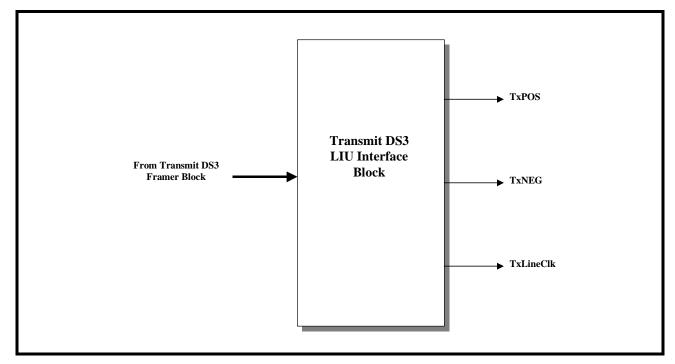

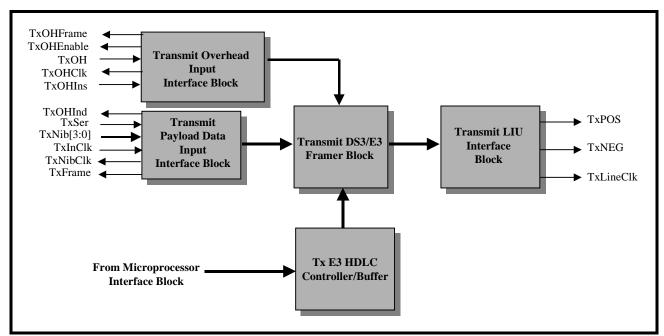

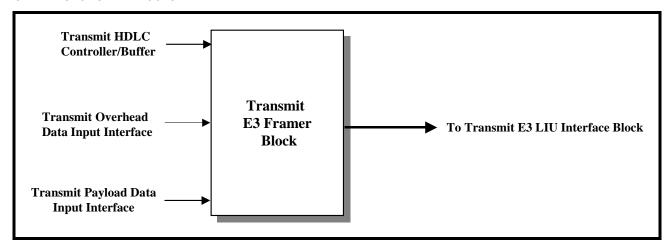

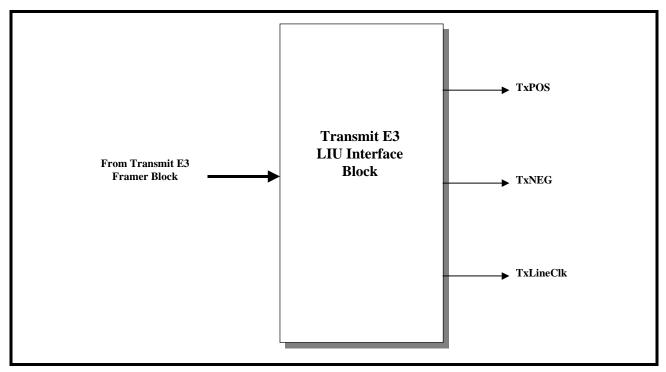

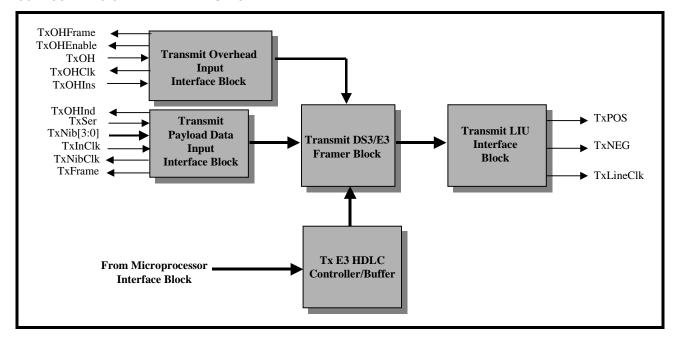

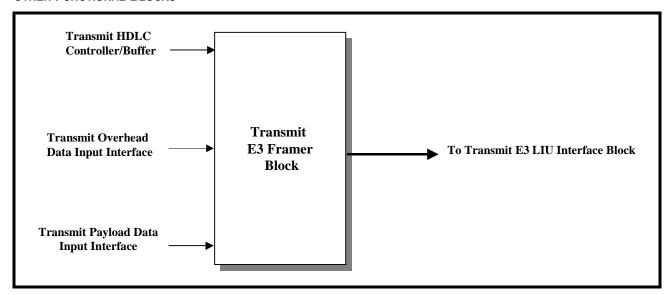

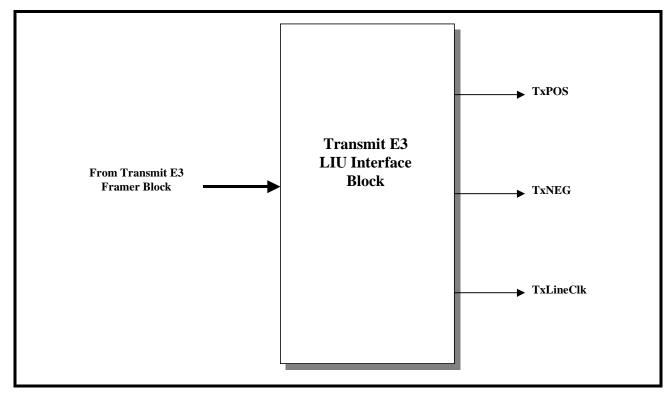

The Transmit Sections, include a Transmit Payload Data Input Interface, a Transmit Overhead data Input Interface Section, a Transmit HDLC Controller, a Transmit DS3/E3 Framer block and a Transmit LIU Interface Block which permits the Terminal Equipment to transmit data to a remote terminal.

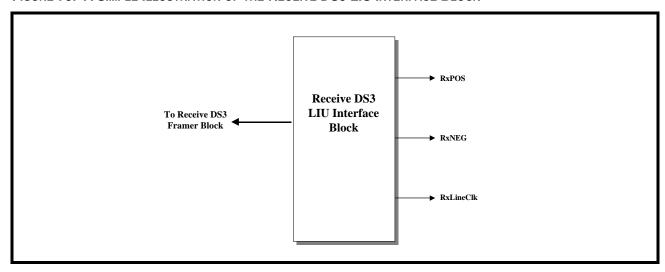

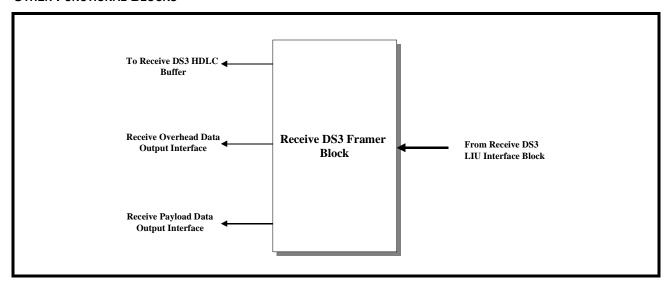

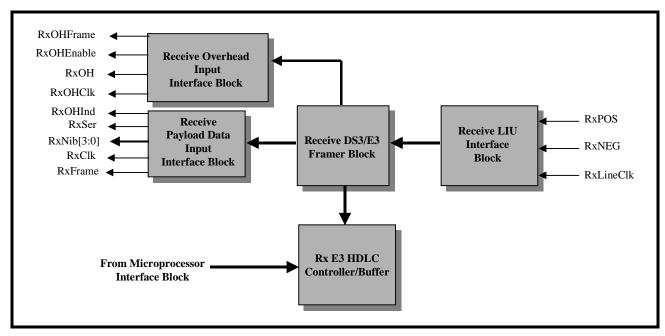

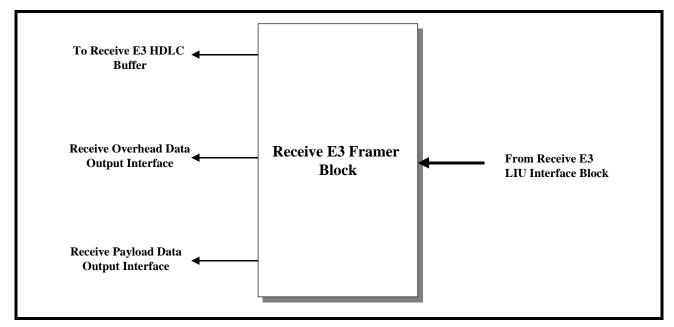

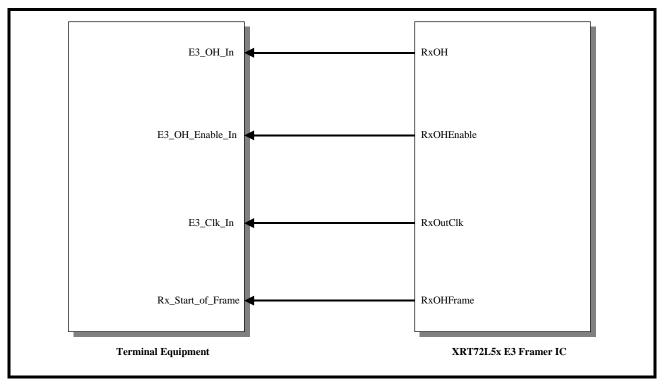

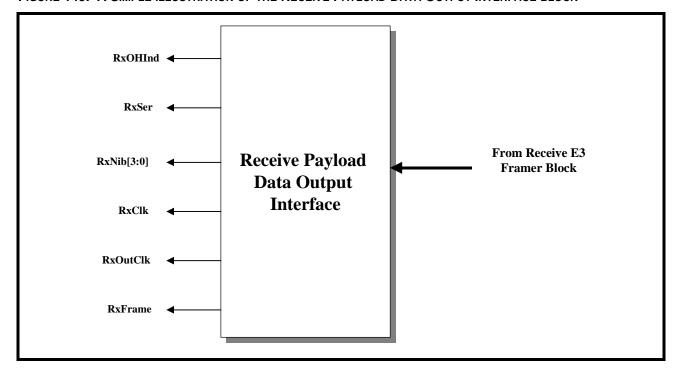

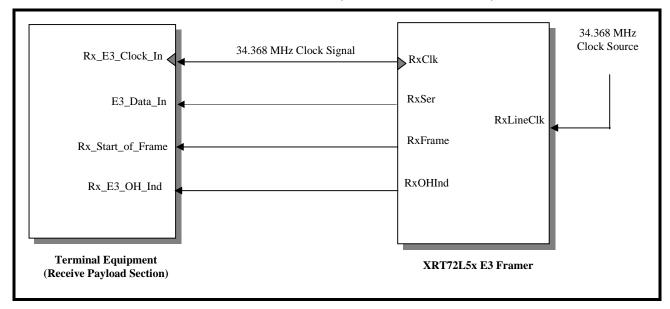

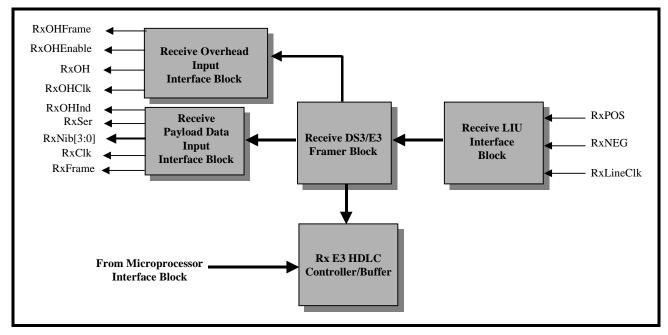

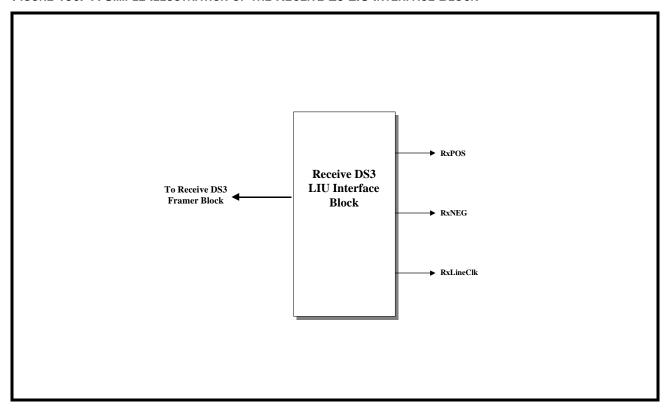

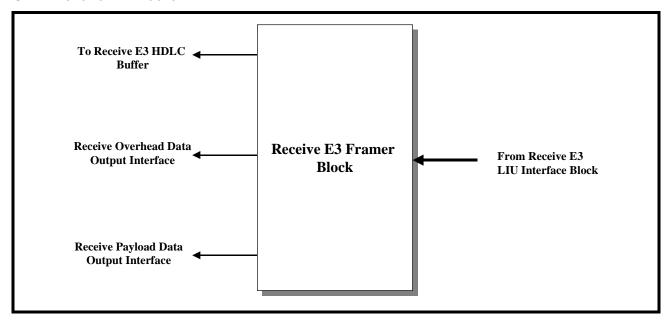

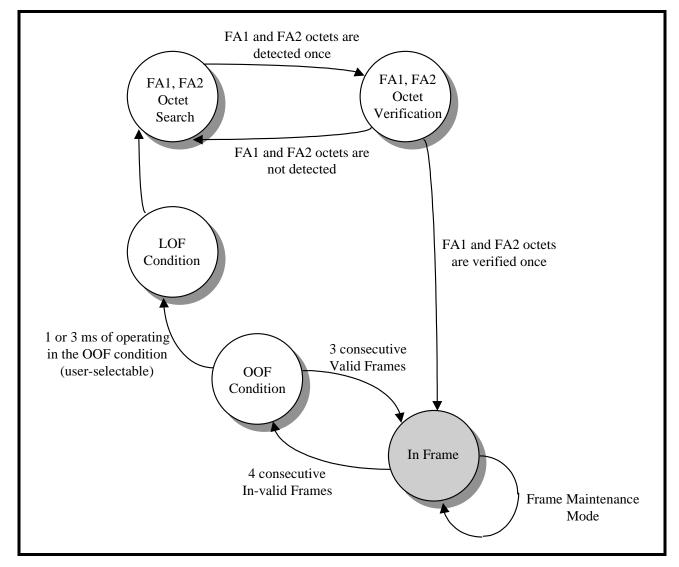

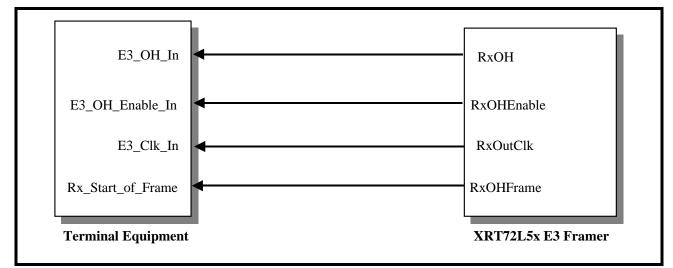

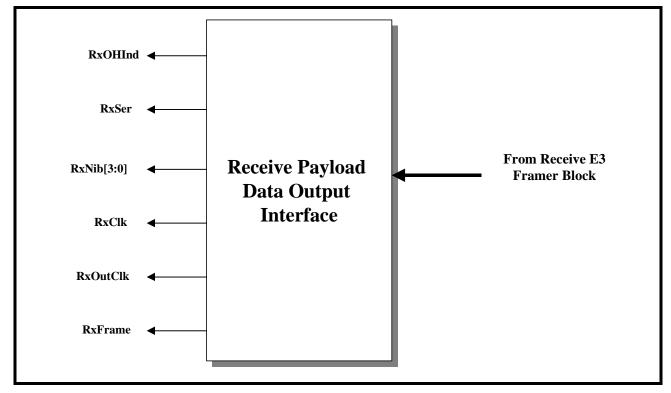

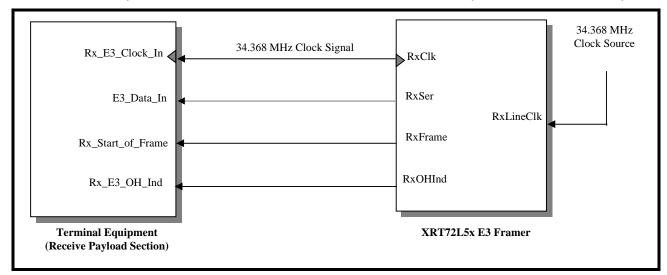

The Receive Sections, consist of a Receive LIU Interface, a Receive DS3/E3 Framer, a Receive HDLC Controller, a Receive Payload Data Output Interface, and a Receive Overhead Data Interface which allows

the local terminal equipment to receive data from remote terminal equipment.

The Microprocessor Interface is used to configure the Framer IC in different operating modes and monitor the performance of the Framer.

The Performance Monitor Sections consist of a large number of "Reset-upon-Read" and "Read-Only" registers that contain cumulative and "one-second" statistics that reflect the performance/health of the Four channels of the Framer IC/system.

#### **FEATURES**

- Transmits, Receives and Processes data in the DS3-C-bit Parity, DS3-M13, E3-ITU-T G.751 and E3-ITU-T G.832 Framing Formats.

- 6 Channel HDLC Controller Tx and Rx

- Interfaces to all Popular Microprocessors

- Integrated Framer Performance Monitor

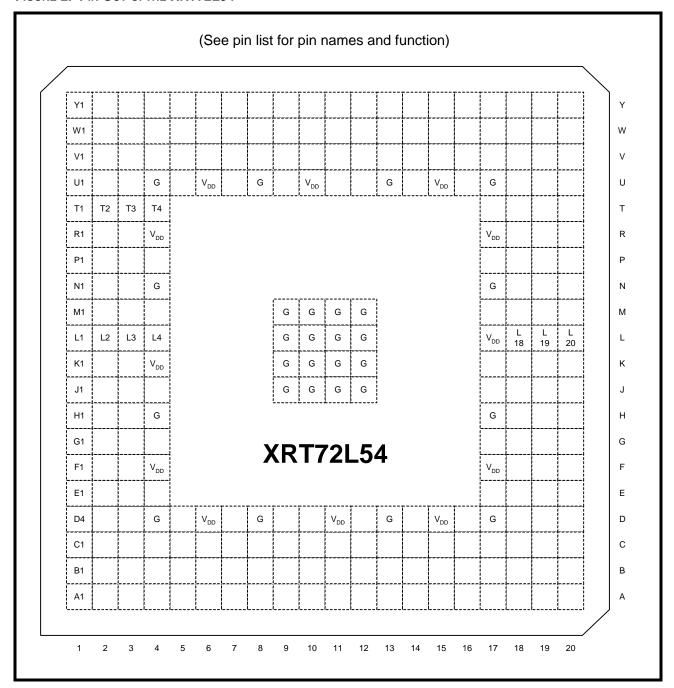

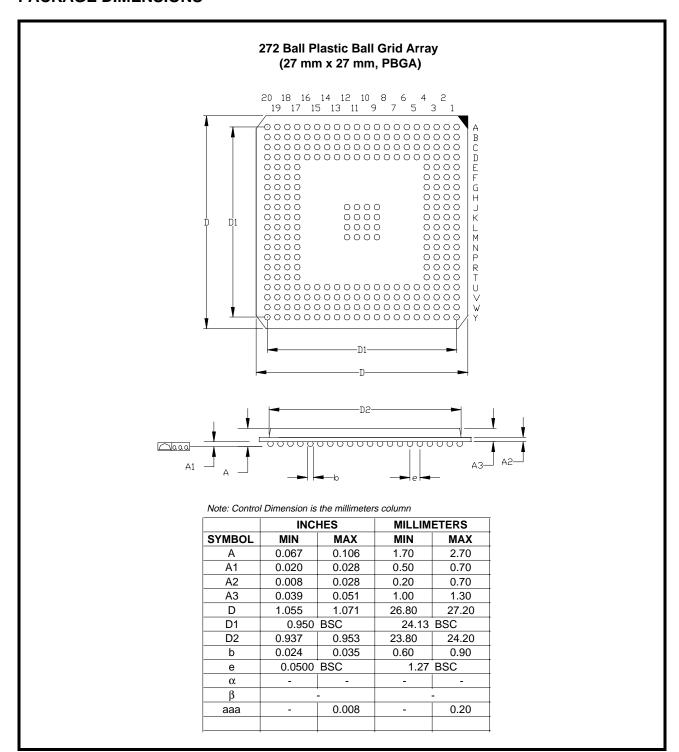

- Available in a 272 Ball PBGA package

- 3.3V Power Supply, 5V Tolerant I/O

- Operating Temperature -40°C to +85°C

#### **APPLICATIONS**

- · Network Interface Units

- · CSU/DSU Equipment.

- PCM Test Equipment

- Fiber Optic Terminals

- DS3/E3 Frame Relay Equipment

FIGURE 1. BLOCK DIAGRAM OF THE XRT72L54

FIGURE 2. PIN OUT OFTHE XRT72L54

### **ORDERING INFORMATION**

| PART NUMBER | PACKAGE TYPE           | OPERATING TEMPERATURE RANGE |

|-------------|------------------------|-----------------------------|

| XRT72L54    | 27x27 mm 272 Ball PBGA | -40°C to +85°C              |

**EXAR**

### **TABLE OF CONTENTS**

| GENERAL DESCRIPTION                                                                                                                                                                    |         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| FEATURES                                                                                                                                                                               |         |

| APPLICATIONS                                                                                                                                                                           |         |

| Figure 1. Block Diagram of the XRT72L54                                                                                                                                                |         |

| Figure 2. Pin Out ofthe XRT72L54                                                                                                                                                       |         |

| ORDERING INFORMATION                                                                                                                                                                   |         |

| ELECTRICAL CHARACTERISTICS                                                                                                                                                             |         |

| Absolute Maximums                                                                                                                                                                      |         |

| DC ELECTRICAL CHARACTERISTICS                                                                                                                                                          |         |

| AC ELECTRICAL CHARACTERISTICS                                                                                                                                                          |         |

| AC ELECTRICAL CHARACTERISTICS (CONT.)                                                                                                                                                  |         |

| 1.0 Timing Diagrams                                                                                                                                                                    |         |

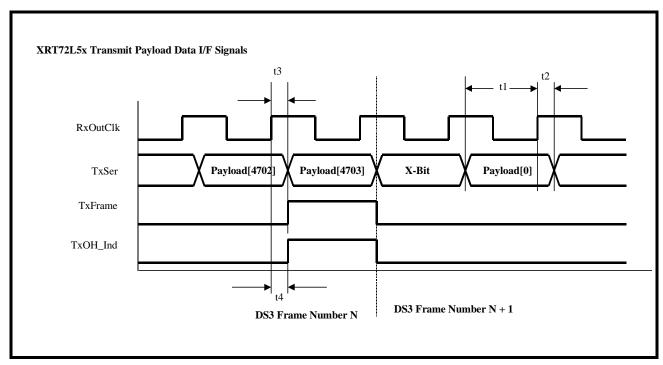

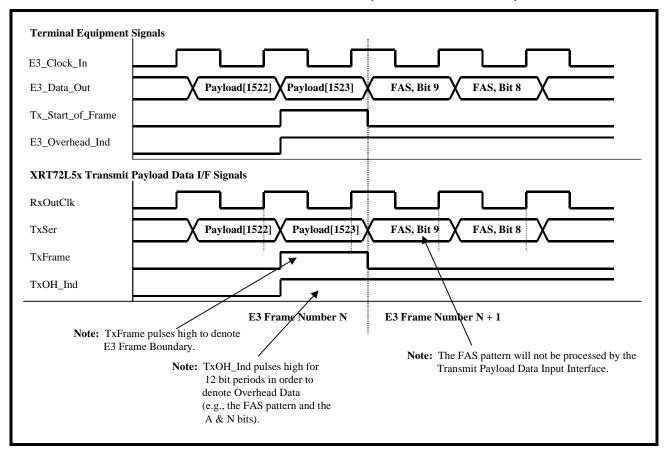

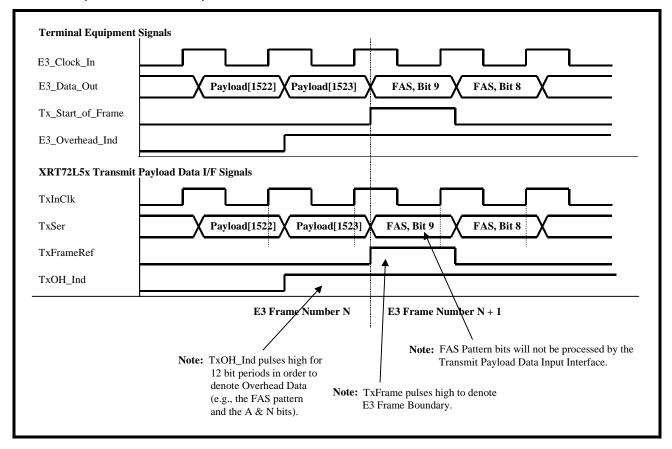

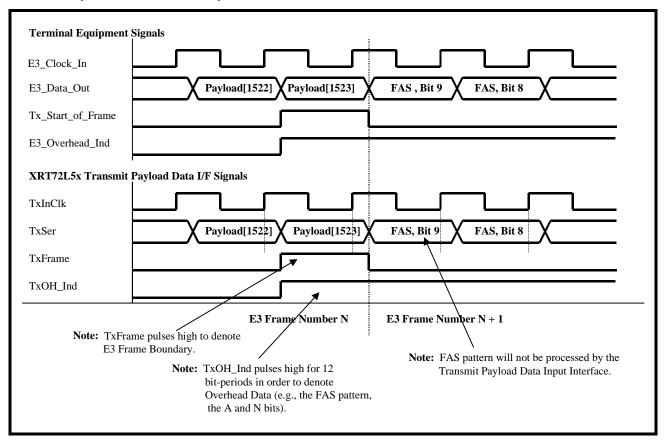

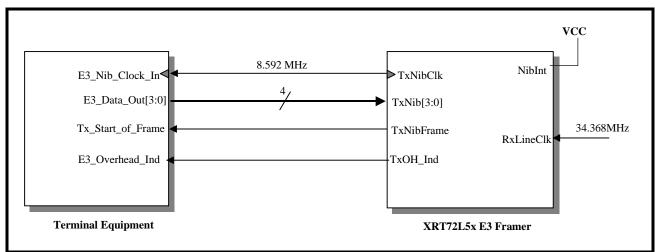

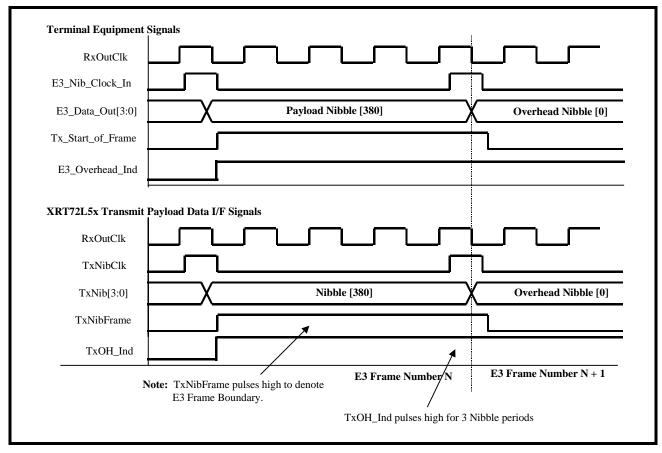

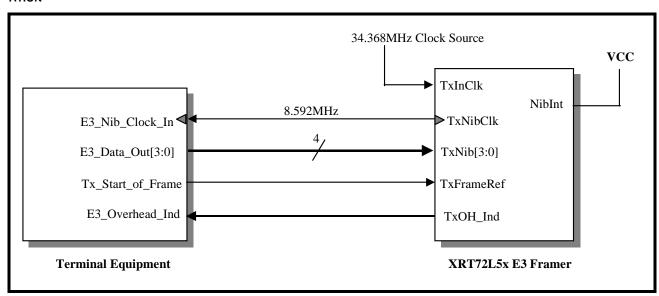

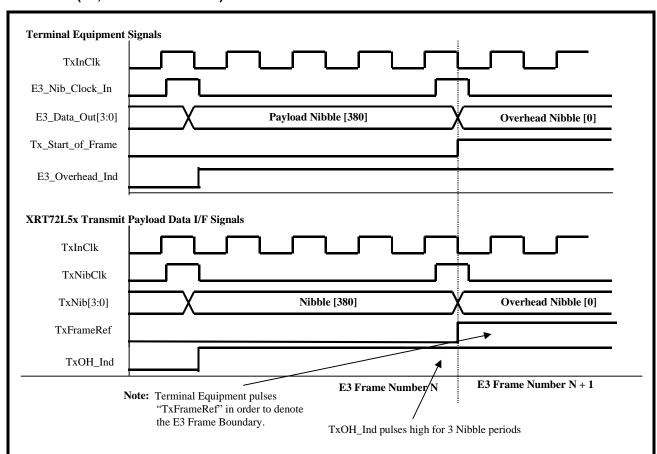

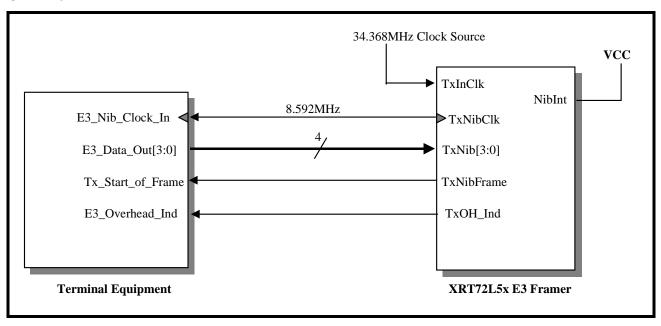

| Figure 3. Timing Diagram for Transmit Payload Input Interface, when the XRT72L54 Device is open                                                                                        | -       |

| both the DS3 and Loop-Timing Modes                                                                                                                                                     | 34      |

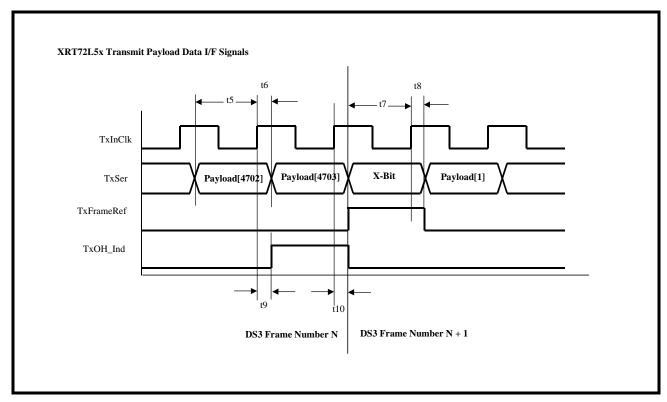

| Figure 4. Timing Diagram for the Transmit Payload Input Interface, when the XRT72L54 Device is op                                                                                      | erating |

| in both the DS3 and Local-Timing Modes                                                                                                                                                 | 34      |

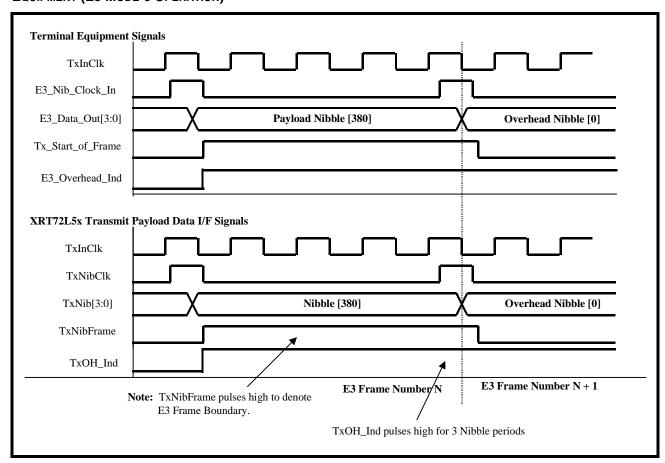

| Figure 5. Timing Diagram for the Transmit Payload Data Input Interface, when the XRT72L54 Dev                                                                                          |         |

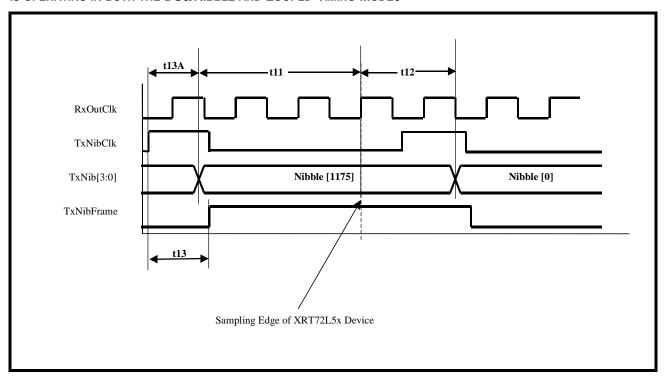

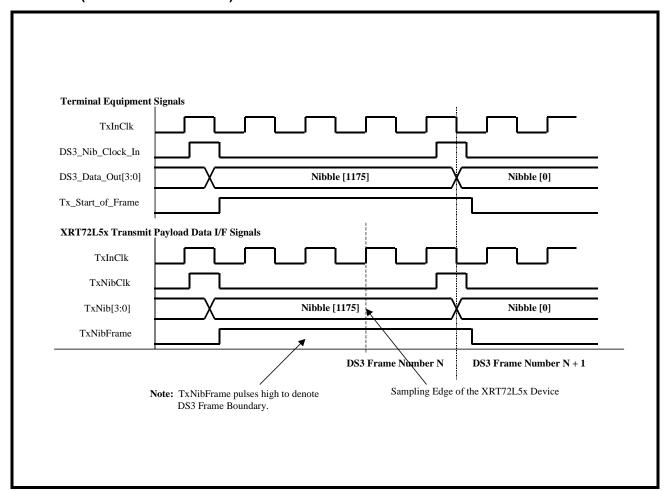

| operating in both the DS3/Nibble and Looped-Timing Modes                                                                                                                               |         |

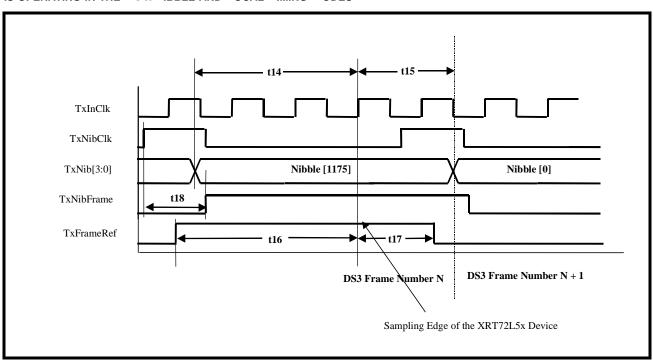

| Figure 6. Timing Diagram for the Transmit Payload Data Input Interface, when the XRT72L54 Dev                                                                                          |         |

| operating in the DS3/Nibble and Local-Timing Modes                                                                                                                                     |         |

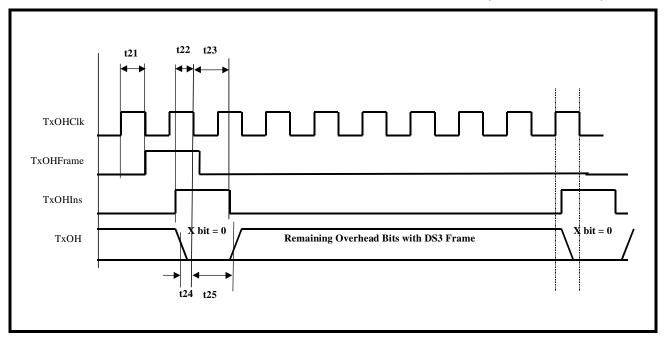

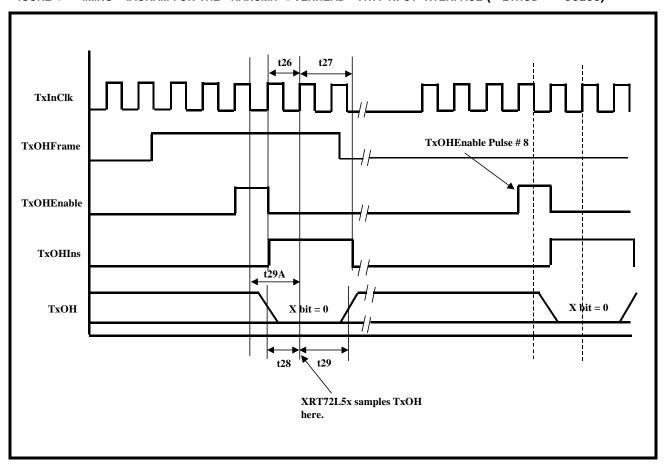

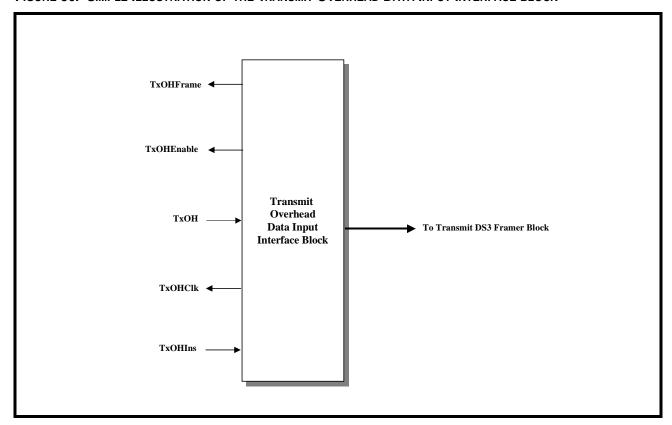

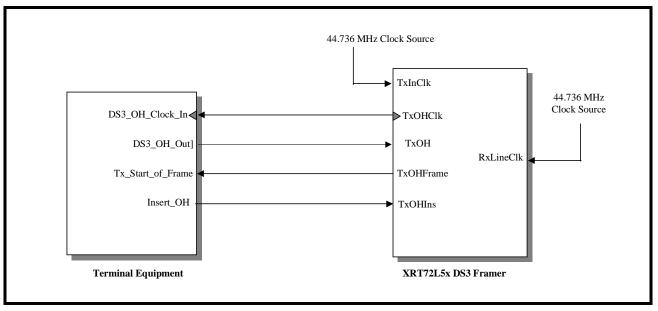

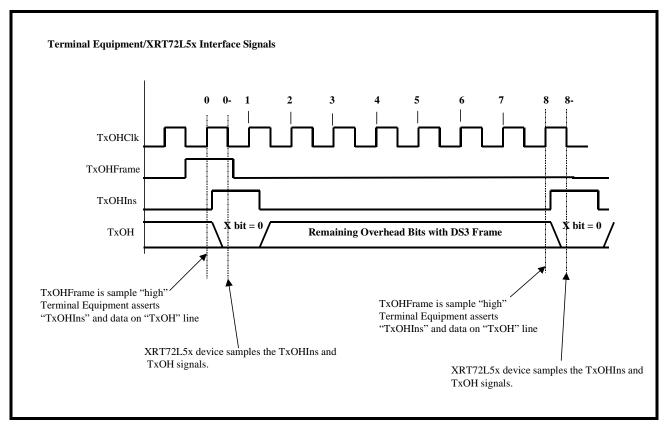

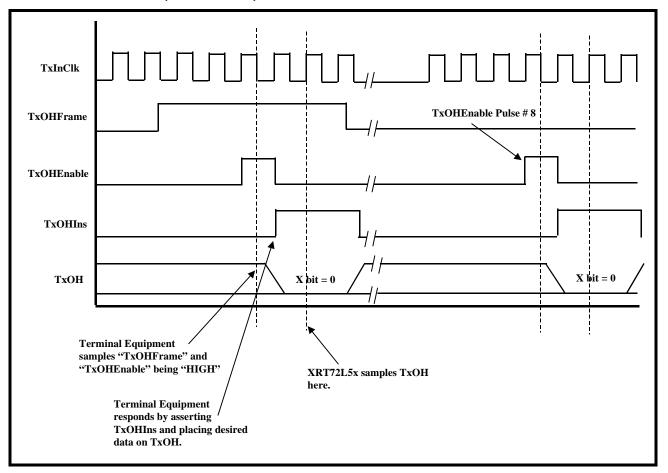

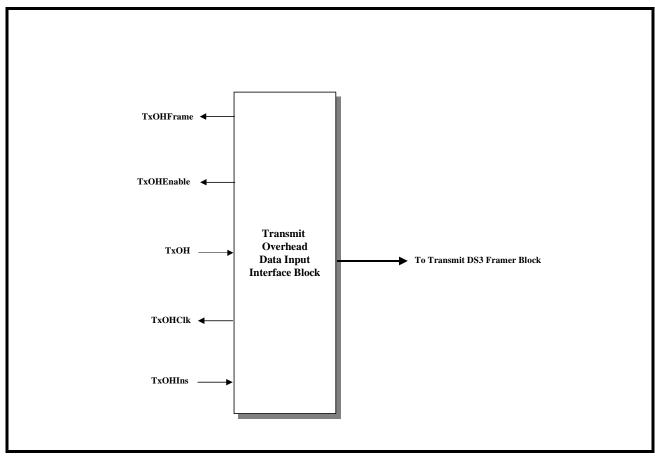

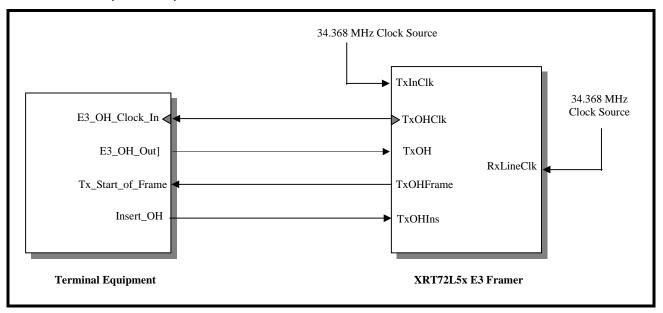

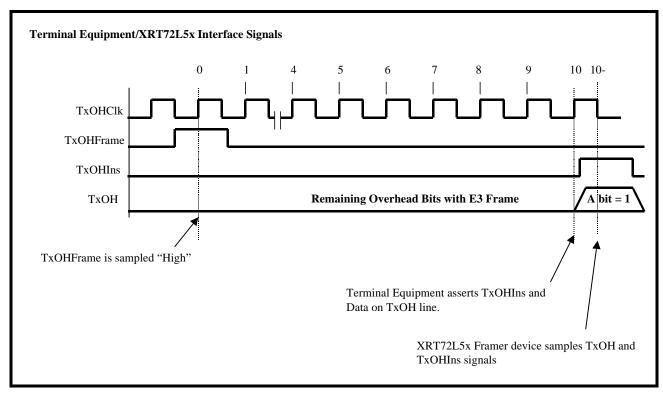

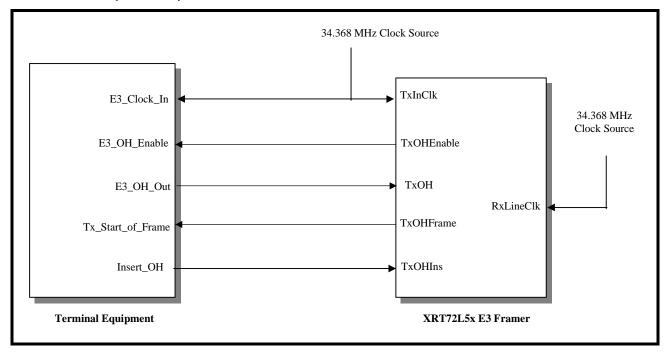

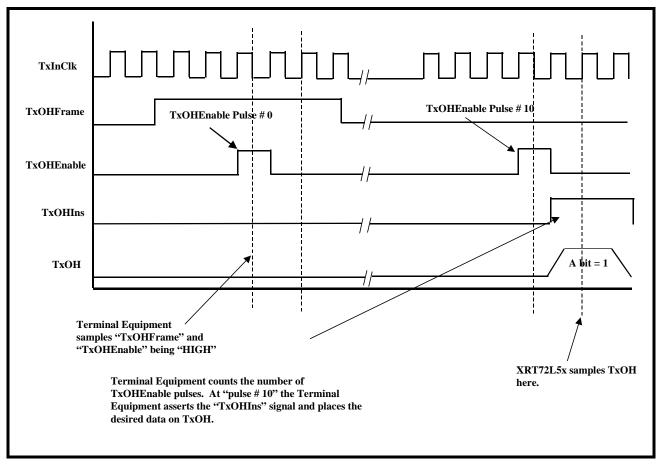

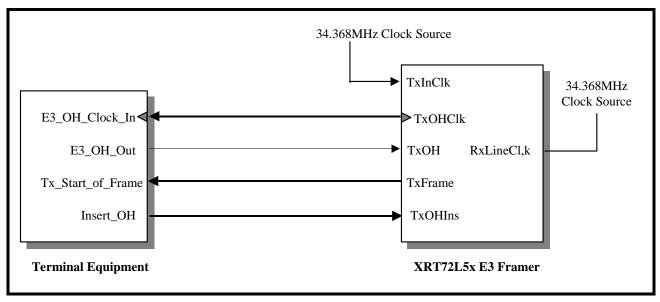

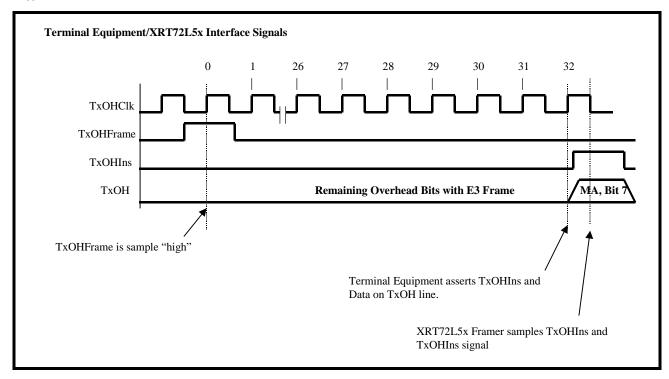

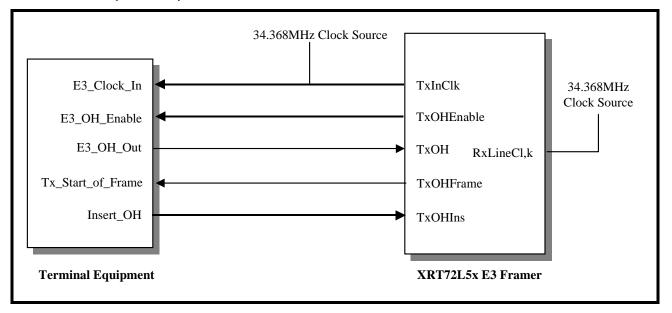

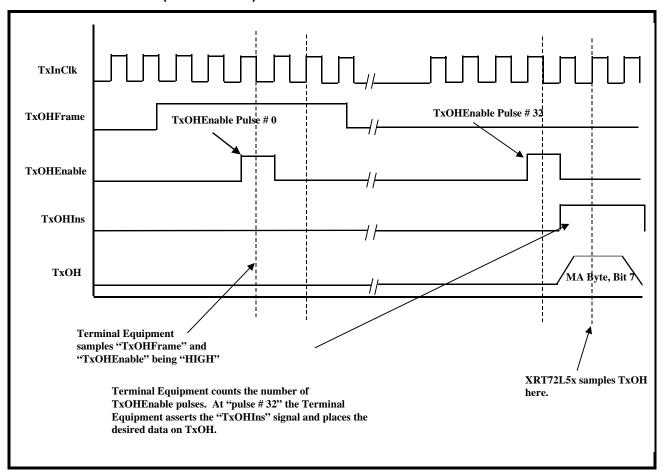

| Figure 7. Timing Diagram for the Transmit Overhead Data Input Interface (Method 1 Access)<br>Figure 8. Timing Diagram for the Transmit Overhead Data Input Interface (Method 2 Access) |         |

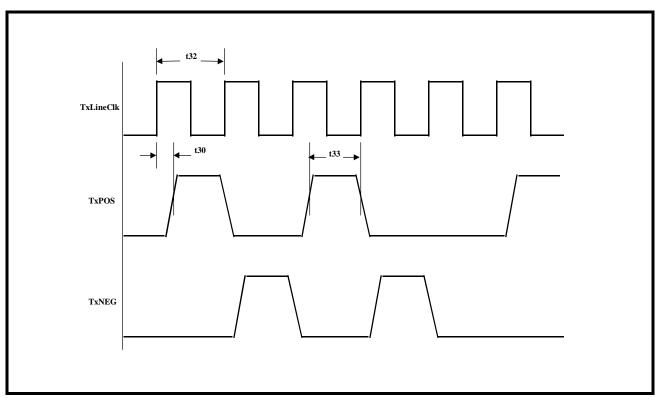

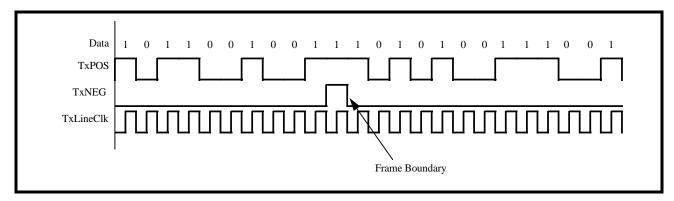

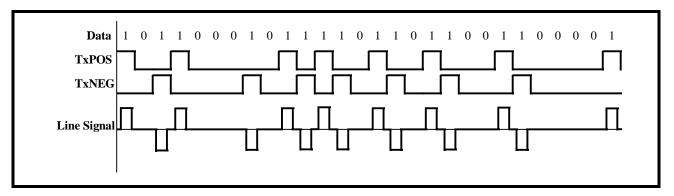

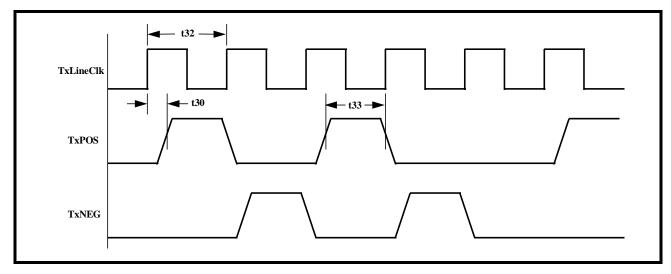

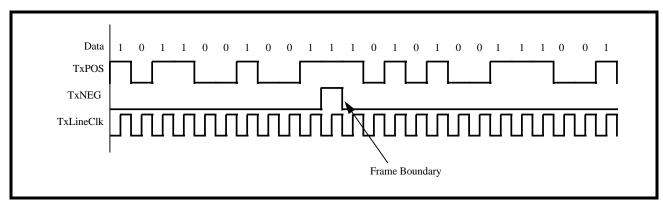

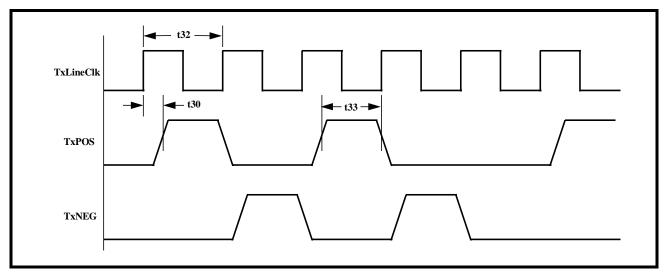

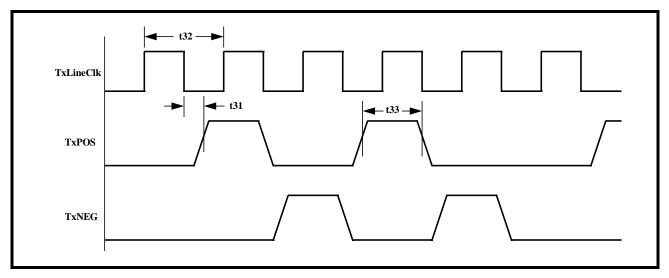

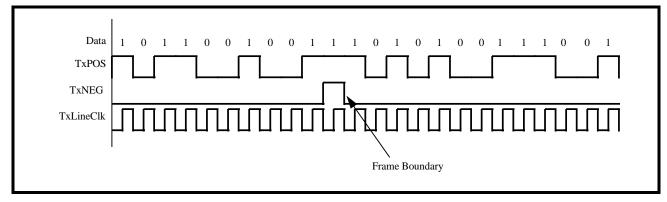

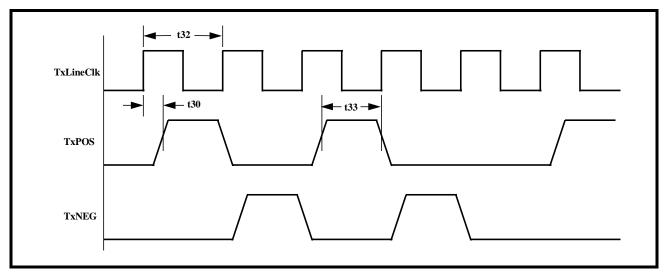

| Figure 9. Transmit LIU Interface Timing - Framer is configured to update "TxPOS" and "TxNEG" o                                                                                         |         |

| rising edge of "TxLineClk"                                                                                                                                                             |         |

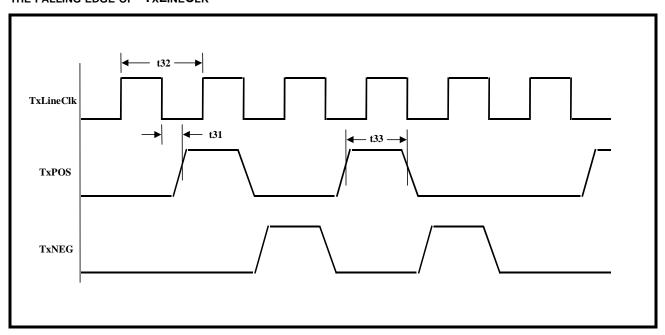

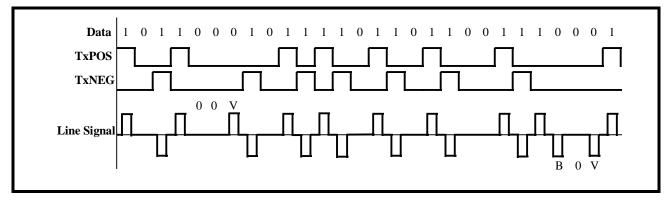

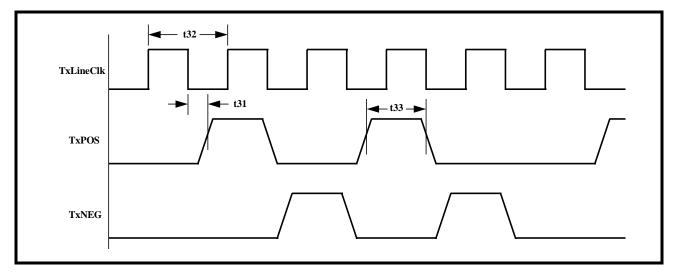

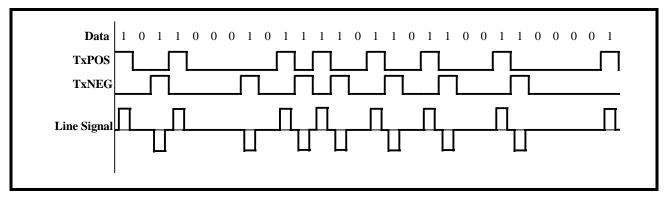

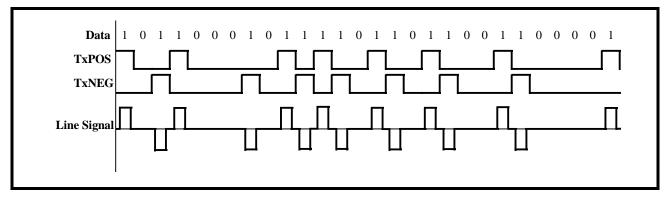

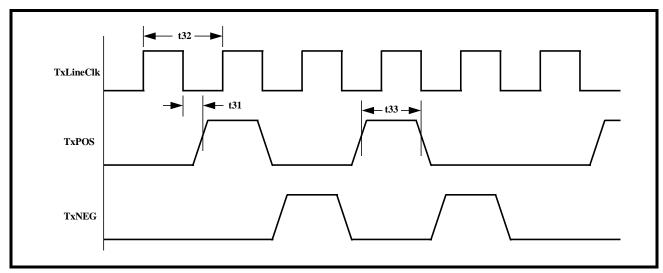

| Figure 10. Transmit LIU Interface Timing - Framer is configured to update "TxPOS" and "TxNEG"                                                                                          |         |

| falling edge of "TxLineClk"                                                                                                                                                            |         |

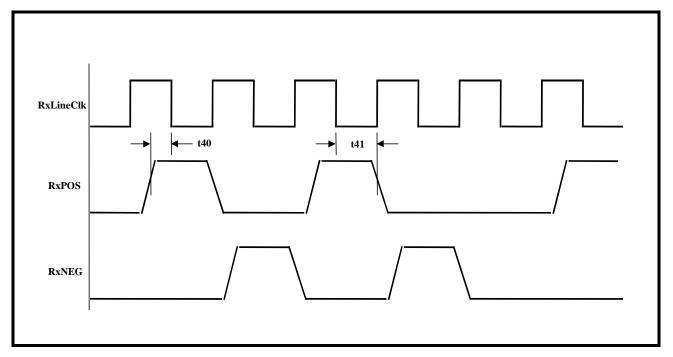

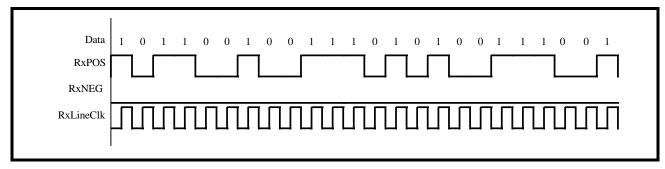

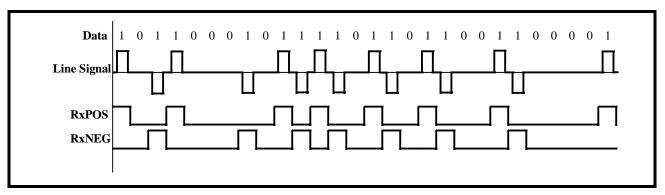

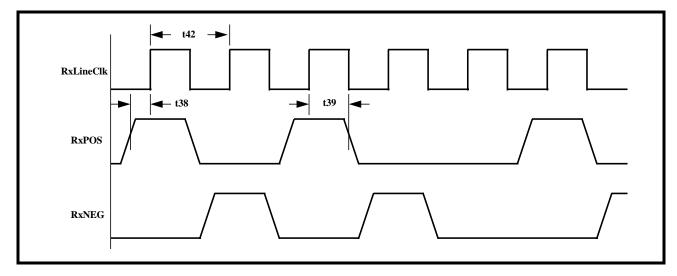

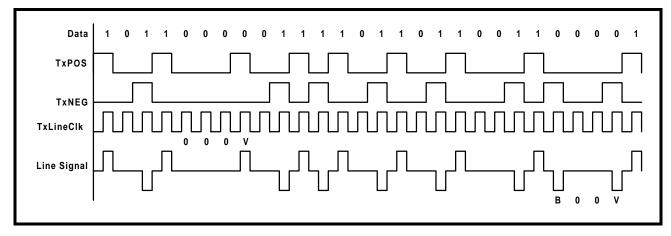

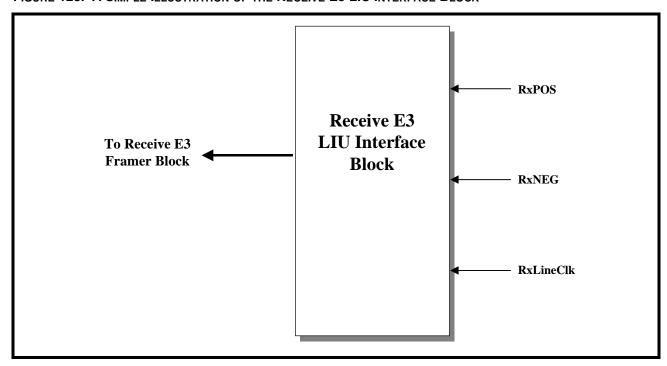

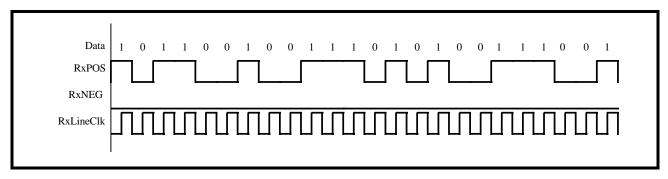

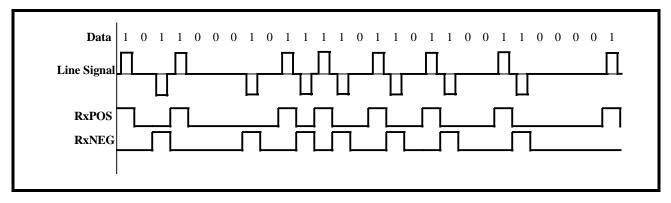

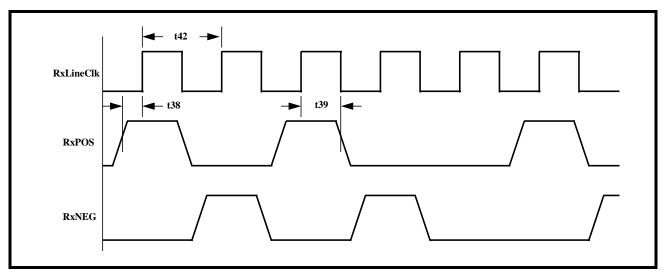

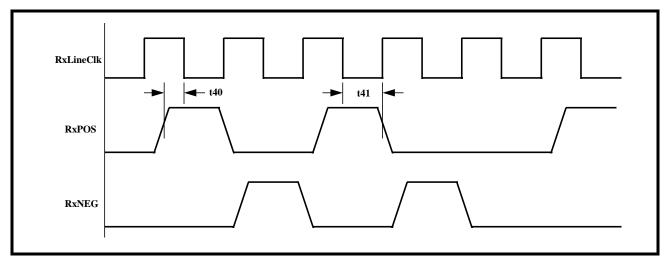

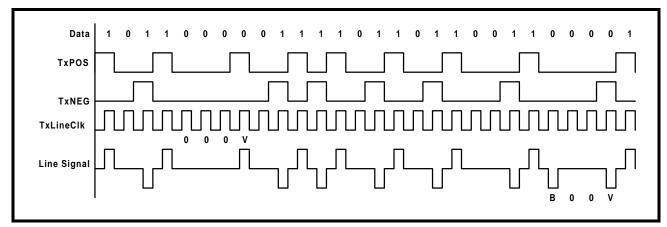

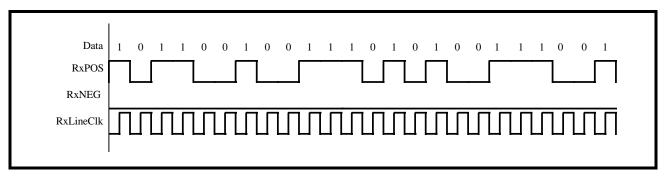

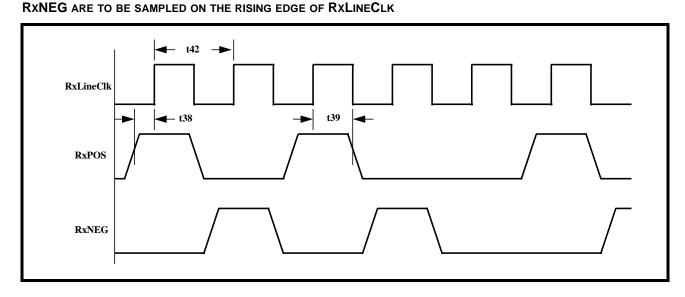

| Figure 11. Receive LIU Interface Timing - Framer is configured to sample "RxPOS" and "RxNEG"                                                                                           | on the  |

| rising edge of "RxLineClk"                                                                                                                                                             |         |

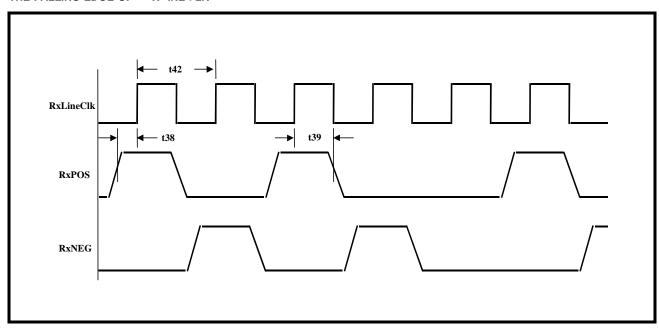

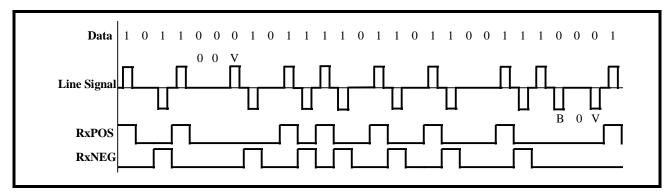

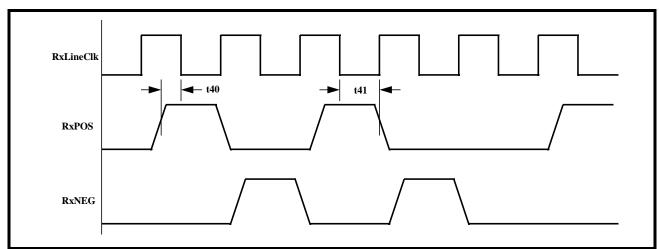

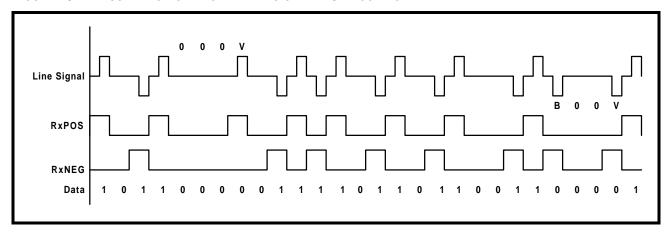

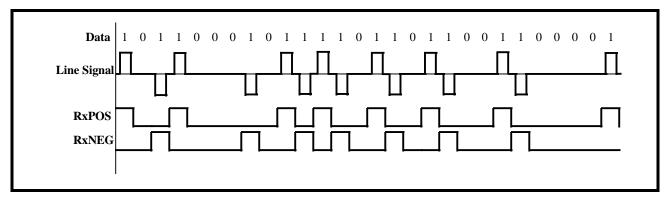

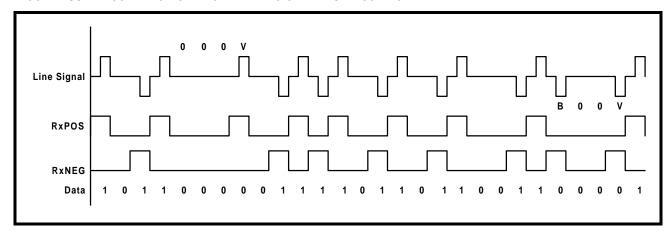

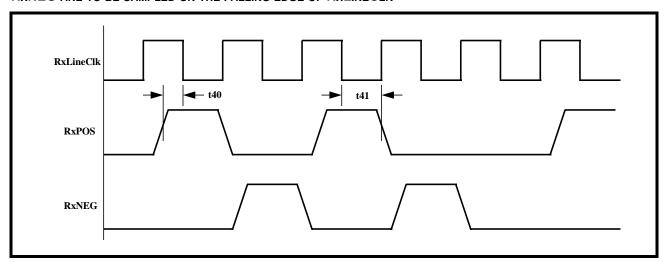

| Figure 12. Receiver LIU Interface Timing - Framer is configured to sample "RxPOS" and "RxNEG"                                                                                          |         |

| falling edge of "RxLineClk"                                                                                                                                                            |         |

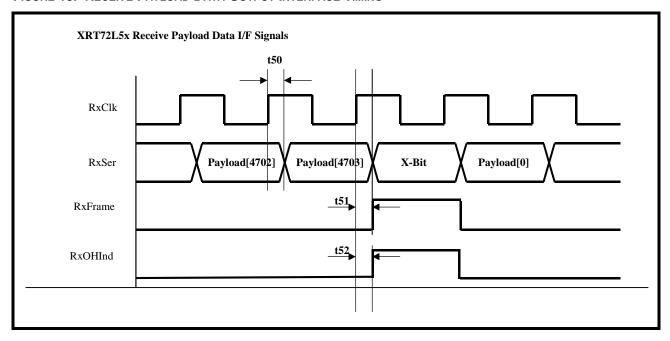

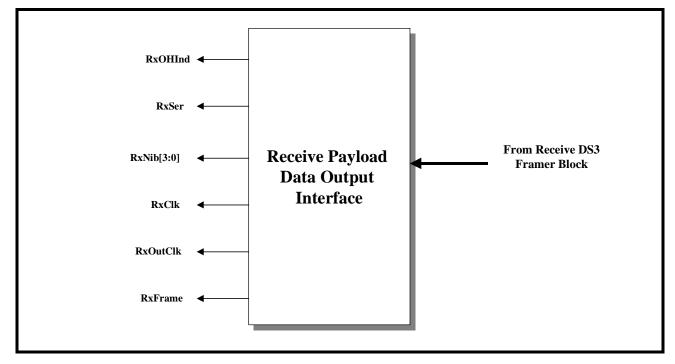

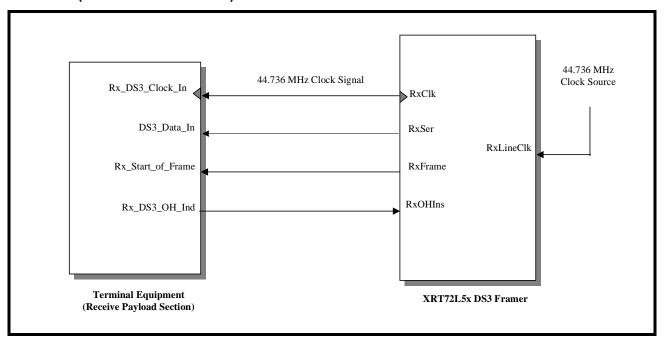

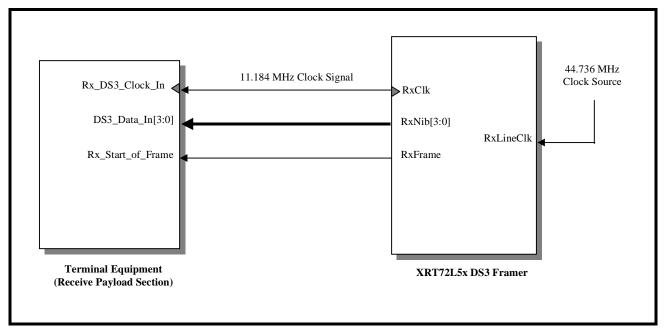

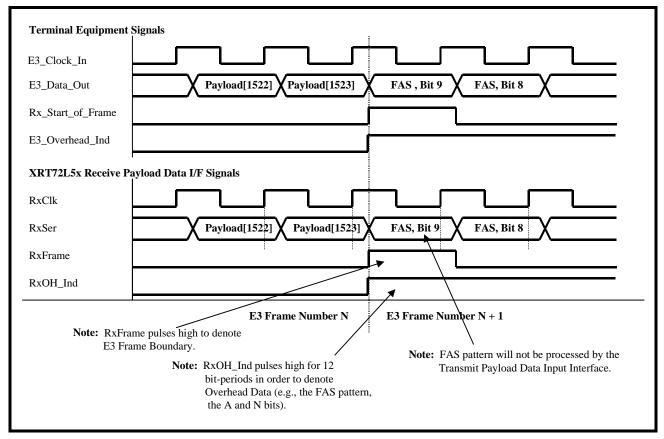

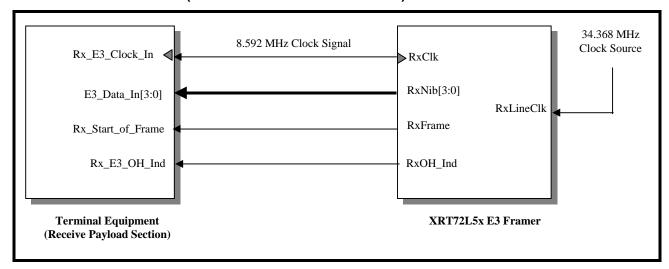

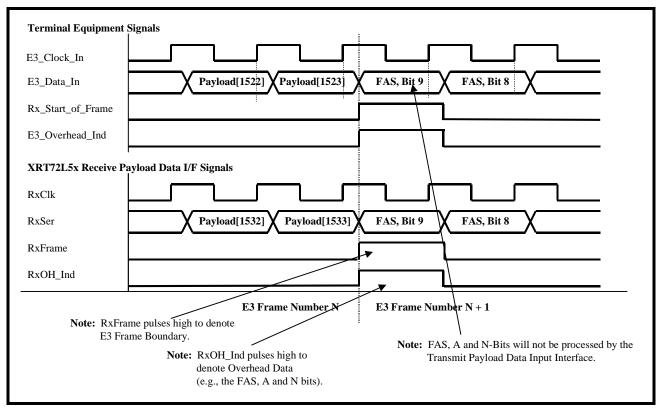

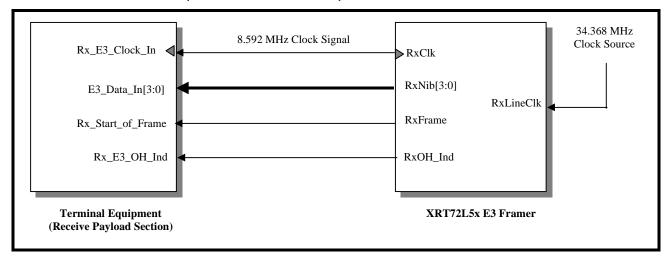

| Figure 13. Receive Payload Data Output Interface Timing                                                                                                                                |         |

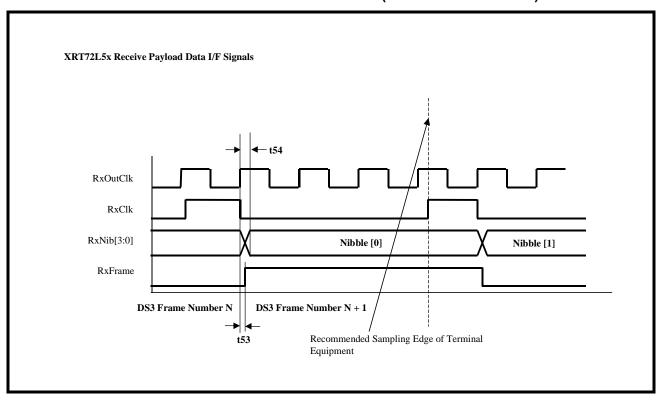

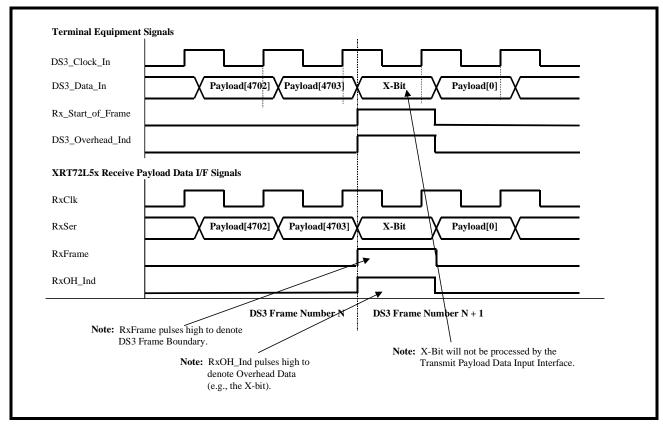

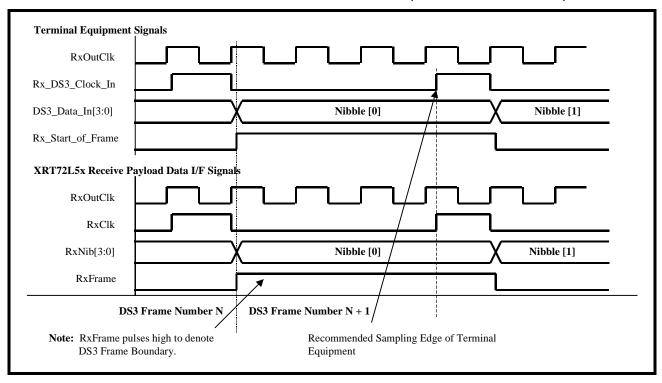

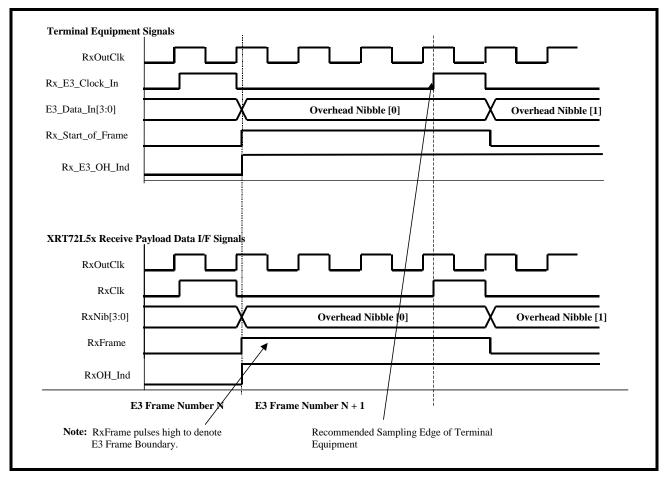

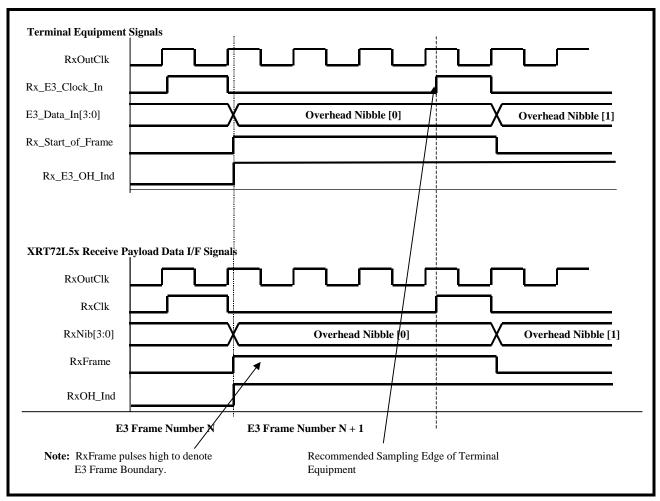

| Figure 14. Receive Payload Data Output Interface Timing (Nibble Mode Operation)                                                                                                        | 39      |

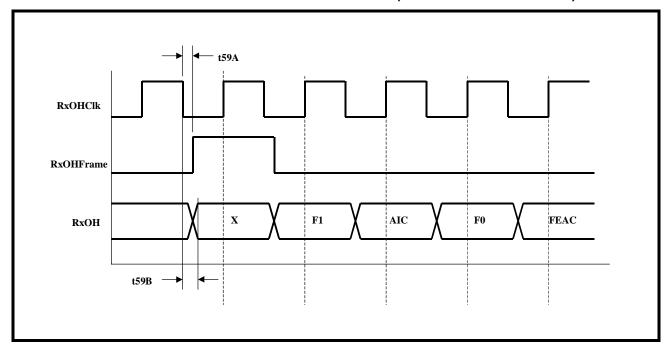

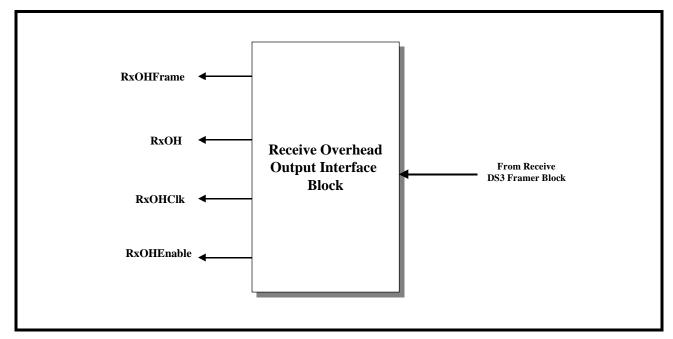

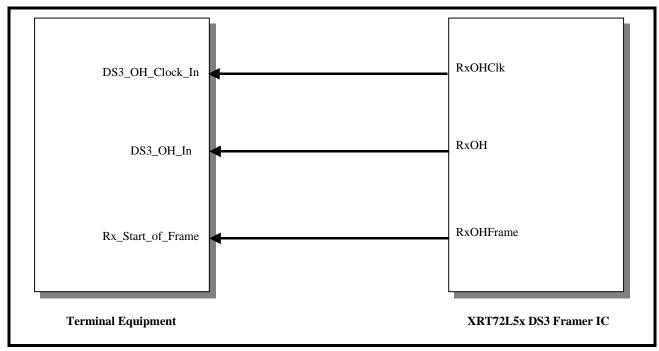

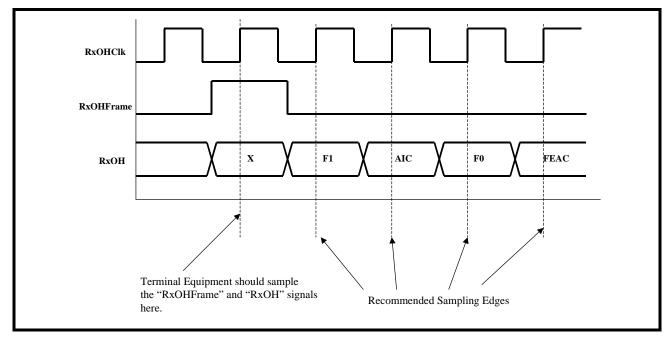

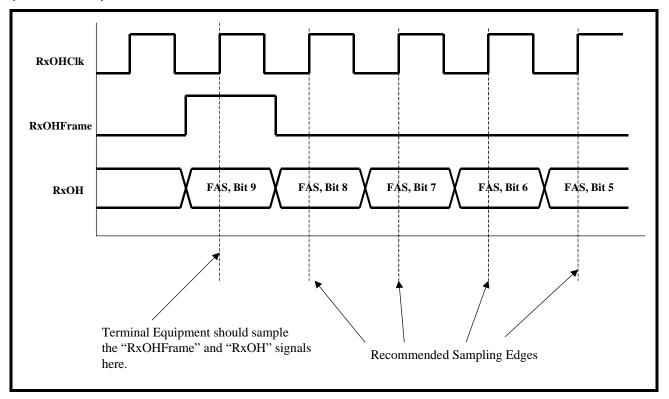

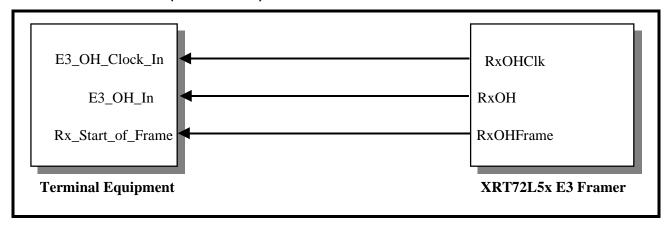

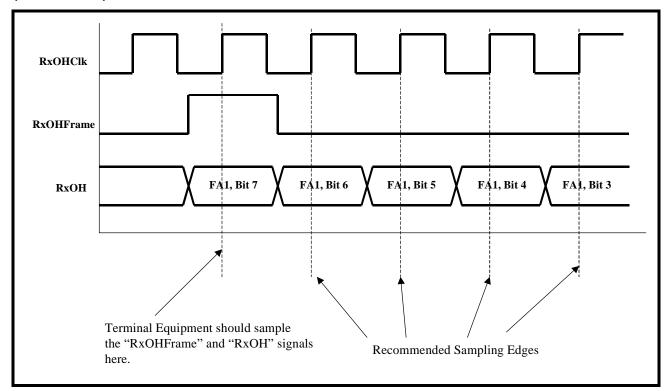

| Figure 15. Receive Overhead Data Output Interface Timing (Method 1 - Using RxOHClk)                                                                                                    | 40      |

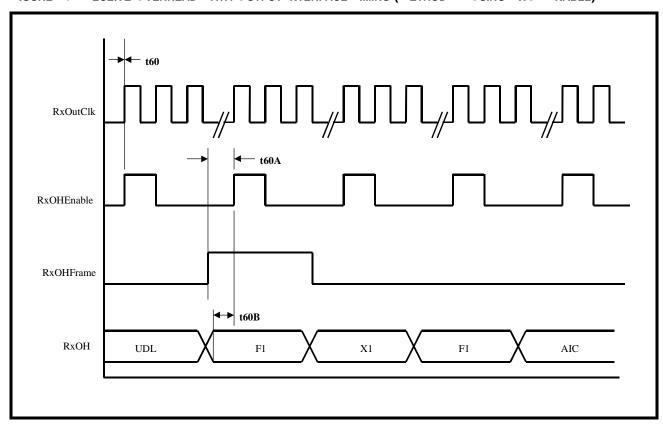

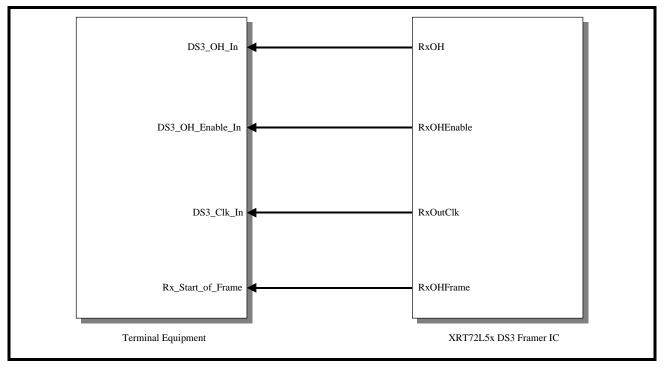

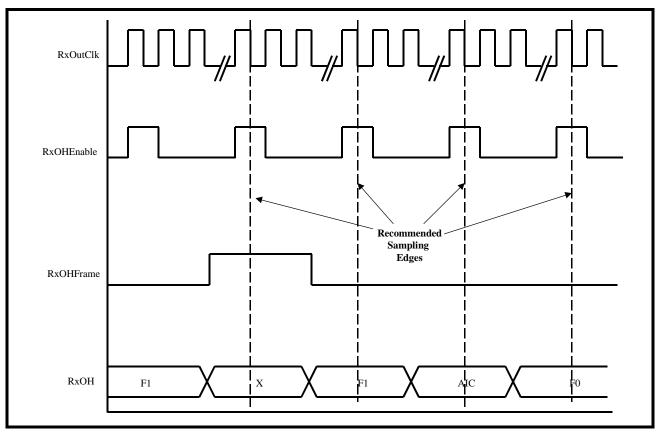

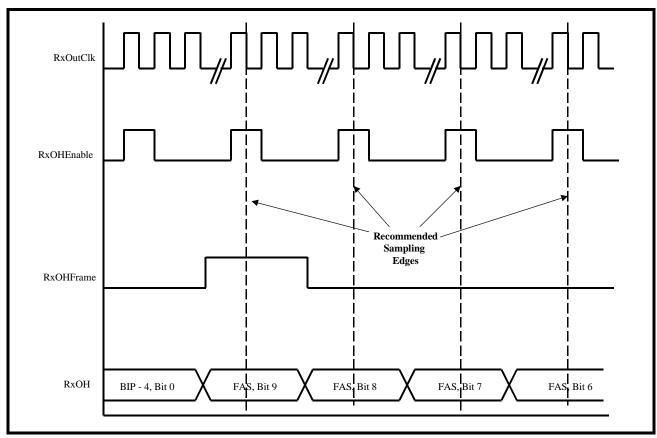

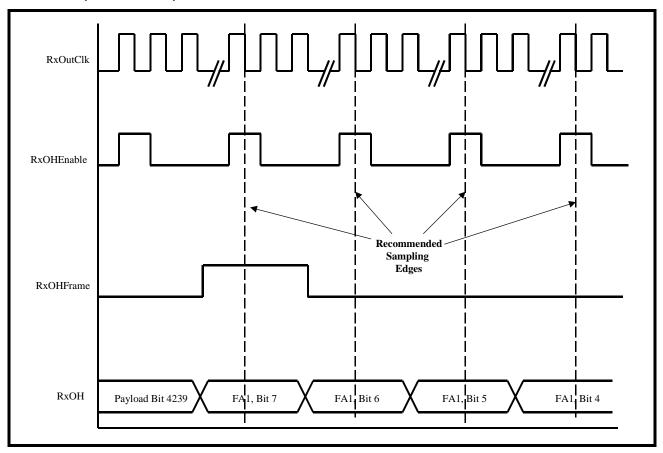

| Figure 16. Receive Overhead Data Output Interface Timing (Method 2 - Using RxOHEnable)                                                                                                 |         |

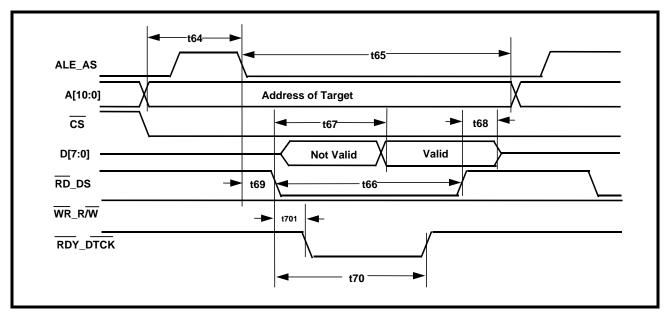

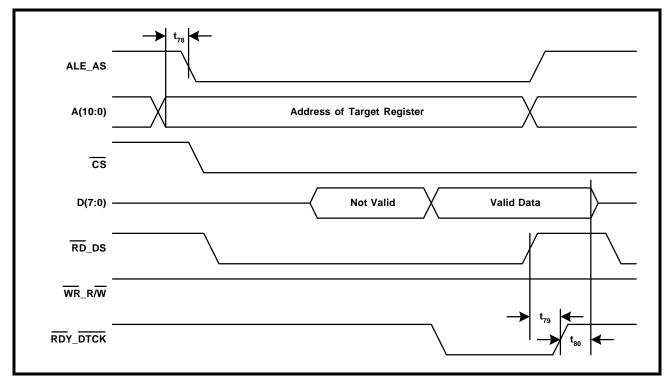

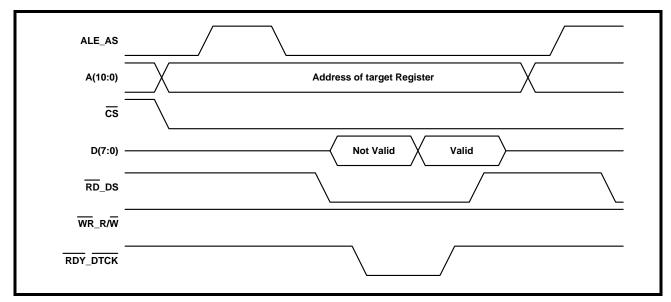

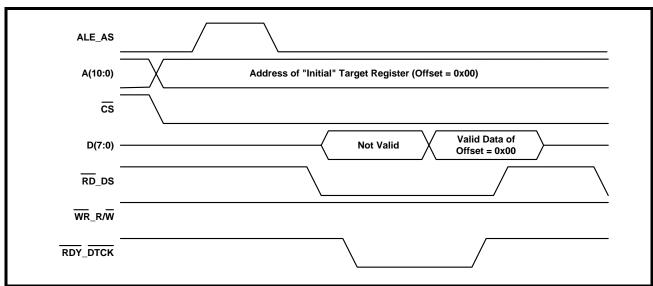

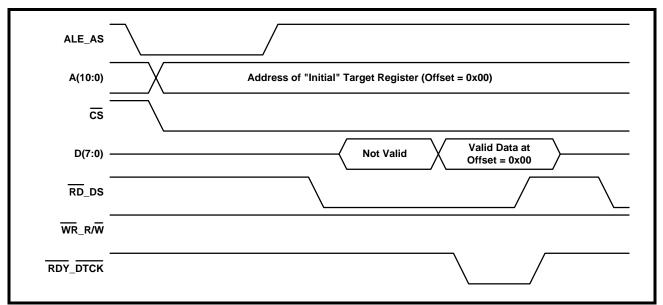

| Figure 17. Microprocessor Interface Timing - Intel Type Programmed I/O Read Operations                                                                                                 | 41      |

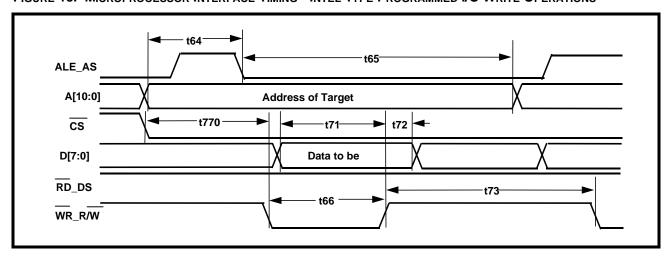

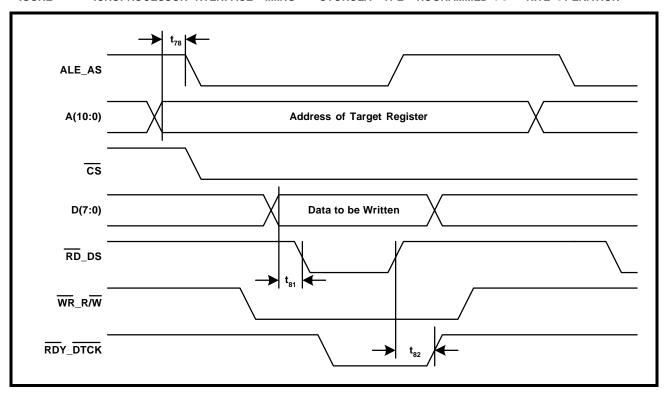

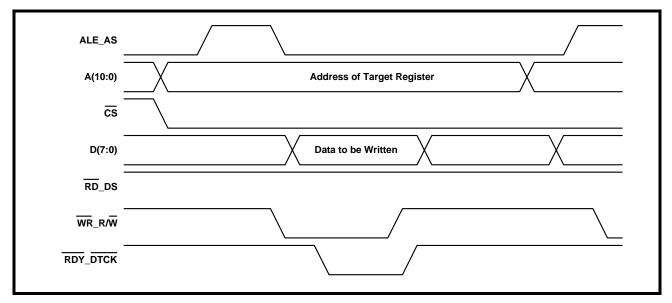

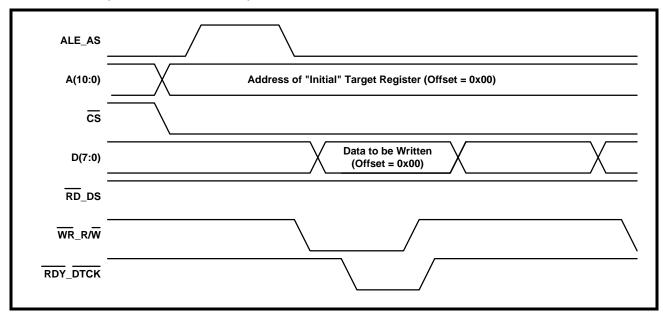

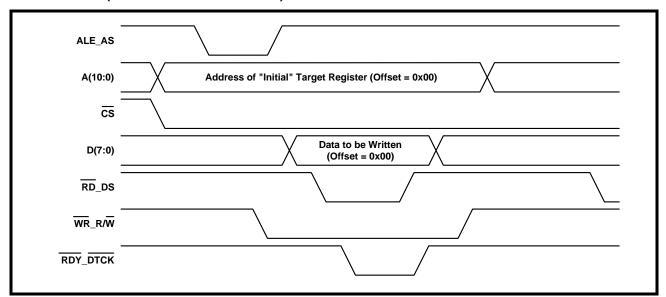

| Figure 18. Microprocessor Interface Timing - Intel Type Programmed I/O Write Operations                                                                                                |         |

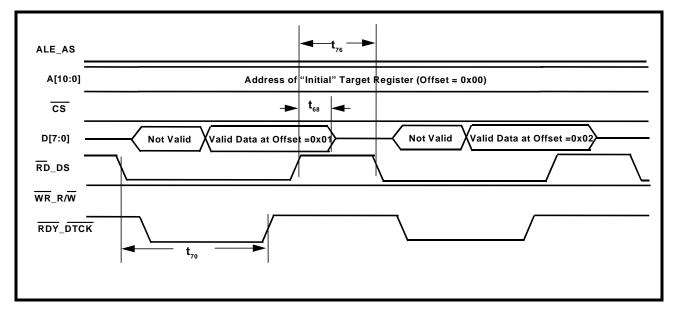

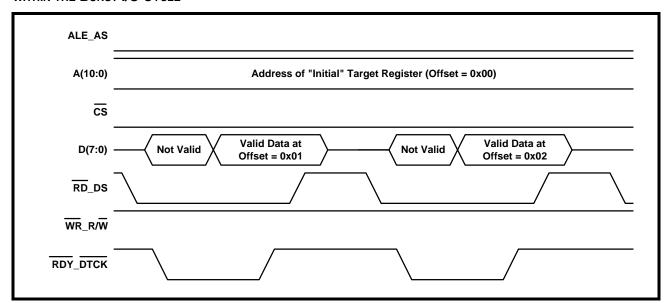

| Figure 19. Microprocessor Interface Timing - Intel Type Read Burst Access Operation                                                                                                    |         |

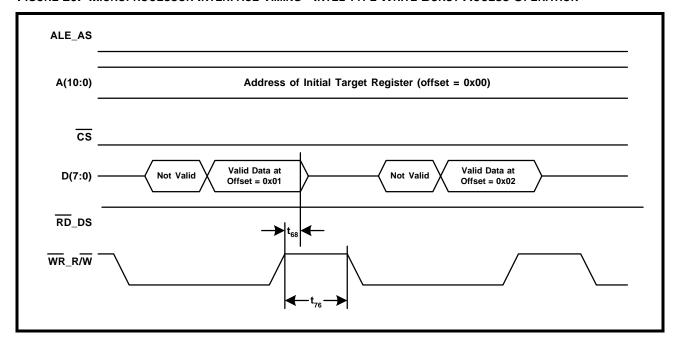

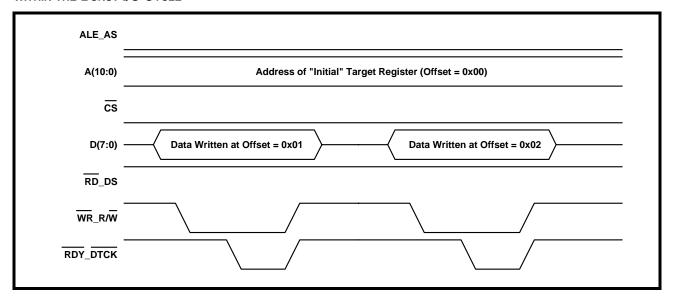

| Figure 20. Microprocessor Interface Timing - Intel type Write Burst Access Operation                                                                                                   |         |

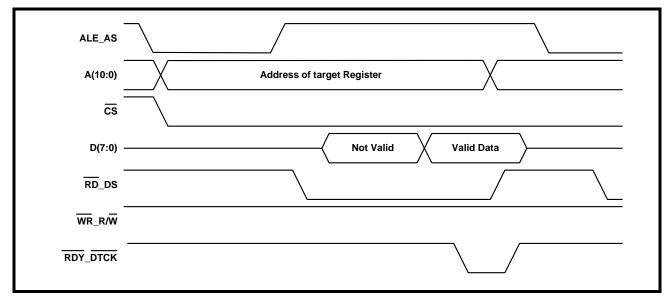

| Figure 21. Microprocessor Interface Timing - Motorola Type Programmed I/O Read Operation                                                                                               |         |

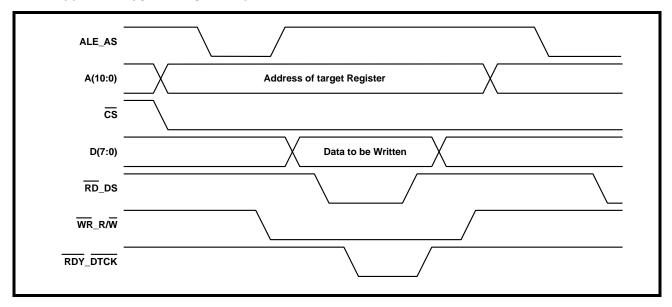

| Figure 22. Microprocessor Interface Timing - Motorola Type Programmed I/O Write Operation                                                                                              |         |

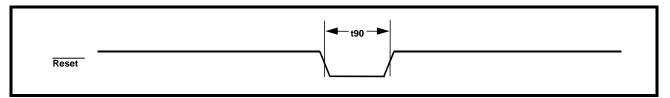

| Figure 23. Microprocessor Interface Timing - Reset Pulse Width                                                                                                                         |         |

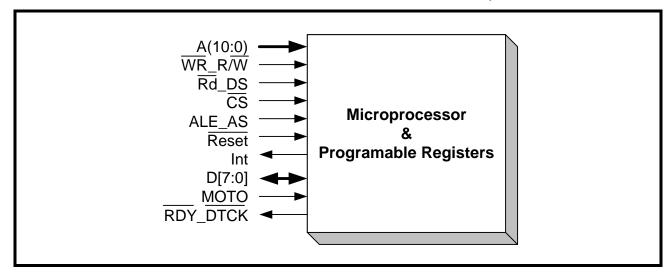

| 2.0 The Microprocessor Interface Block                                                                                                                                                 |         |

| 2.1 CHANNEL SELECTION WITHIN THE XRT72L54 DEVICE                                                                                                                                       | 45      |

| TABLE 1: THE RELATIONSHIP BETWEEN ADDRESS BITS A9, A10 AND THE SELECTED CONFIGURATION RE                                                                                               |         |

| BANK                                                                                                                                                                                   |         |

| Figure 24. Simple Block Diagram of the Microprocessor Interface Block, within the Framer IC                                                                                            |         |

| 2.2 THE MICROPROCESSOR INTERFACE BLOCK SIGNAL                                                                                                                                          |         |

| TABLE 2: DESCRIPTION OF THE MICROPROCESSOR INTERFACE SIGNALS THAT EXHIBIT CONSTANT ROLES IN THE INTEL AND MOTOROLA MODES                                                               |         |

| TABLE 3: PIN DESCRIPTION OF MICROPROCESSOR INTERFACE SIGNALS - WHILE THE MICROPROCESSOR                                                                                                |         |

| FACE IS OPERATING IN THE INTEL MODE                                                                                                                                                    |         |

| TABLE 4: PIN DESCRIPTION OF THE MICROPROCESSOR INTERFACE SIGNALS WHILE THE MICROPROCESS                                                                                                |         |

| TERFACE IS OPERATING IN THE MOTOROLA MODE                                                                       |     |

|-----------------------------------------------------------------------------------------------------------------|-----|

| 2.3.1 Interfacing the XRT72L54 DS3/E3 Framer to the Microprocessor over an 8 bit wide bi-directional Data B 48  |     |

| 2.3.2 Data Access Modes 4                                                                                       |     |

| Figure 25. Behavior of Microprocessor Interface signals during an Intel-type Programmed I/O Read Op ation       |     |

| Figure 26. Behavior of the Microprocessor Interface Signals, during an Intel-type Programmed I/O Writ Operation |     |

| Figure 27. Illustration of the Behavior of Microprocessor Interface signals, during a Motorola-type Pro-        | •   |

| grammed I/O Read Operation                                                                                      |     |

| Figure 28. Illustration of the Behavior of the Microprocessor Interface signal, during a Motorola-type Pr       | ro- |

| grammed I/O Write Operation                                                                                     | 3   |

| Figure 29. Behavior of the Microprocessor Interface Signals, during the Initial Read Operation of a Burs        |     |

| Cycle (Intel Type Processor)5                                                                                   |     |

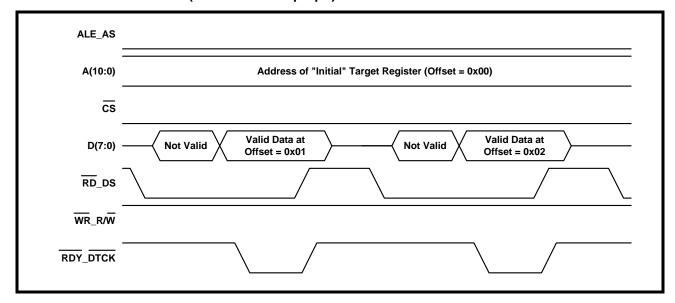

| Figure 30. Behavior of the Microprocessor Interface Signals, during subsequent Read Operations within           |     |

| the Burst I/O Cycle                                                                                             | 55  |

| Figure 31. Behavior of the Microprocessor Interface signals, during the Initial Write Operation of a Burs       | st  |

| Cycle (Intel-type Processor)                                                                                    | 57  |

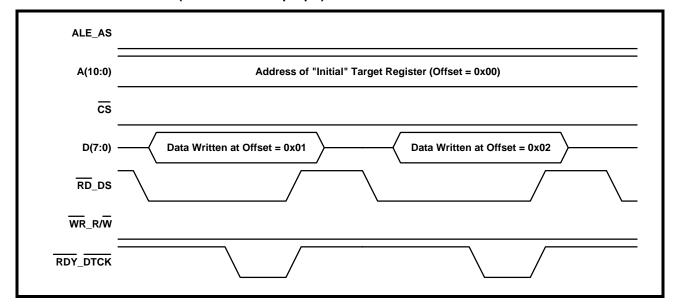

| Figure 32. Behavior of the Microprocessor Interface Signals, during subsequent Write Operations withi           | in  |

| the Burst I/O Cycle                                                                                             | 8   |

| Figure 33. Behavior of the Microprocessor Interface Signals, during the Initial Read Operation of a Burs        | rst |

| Cycle (Motorola Type Processor)                                                                                 | 9   |

| Figure 34. Behavior the Microprocessor Interface Signals, during subsequent Read Operations within t            | the |

| Burst I/O Cycle (Motorola-type μC/μP)6                                                                          |     |

| Figure 35. Behavior of the Microprocessor Interface signals, during the Initial Write Operation of a Burs       |     |

| Cycle (Motorola-type Processor)                                                                                 |     |

| Figure 36. Behavior of the Microprocessor Interface Signals, during subsequent Write Operations with t          |     |

| Burst I/O Cycle (Motorola-type μC/μP)                                                                           |     |

| 2.4 On-Chip Register Organization                                                                               |     |

| 2.4.1 Framer Register Addressing                                                                                | 52  |

| TABLE 5: REGISTER ADDRESSING OF THE FRAMER PROGRAMMER REGISTERS                                                 |     |

| 2.4.2 Framer Register Description                                                                               |     |

| PART NUMBER REGISTER (ADDRESS = 0x02)                                                                           |     |

| VERSION NUMBER REGISTER (ADDRESS = 0x03)                                                                        |     |

| BLOCK INTERRUPT ENABLE REGISTER (ADDRESS = 0x04)                                                                |     |

| BLOCK INTERRUPT STATUS REGISTER (ADDRESS = 0x05)                                                                |     |

| TEST REGISTER (ADDRESS = 0x0C)                                                                                  |     |

| RXDS3 CONFIGURATION & STATUS REGISTER (ADDRESS = 0x10)                                                          |     |

| RXDS3 STATUS REGISTER (ADDRESS = 0x11)                                                                          |     |

| RXDS3 INTERRUPT ENABLE REGISTER (ADDRESS = 0X12)  RXDS3 INTERRUPT STATUS REGISTER (ADDRESS = 0X13)              |     |

| RXDS3 INTERRUPT STATUS REGISTER (ADDRESS = 0x13)                                                                |     |

| RXDS3 STNC DETECT ENABLE REGISTER (ADDRESS = 0X14)                                                              |     |

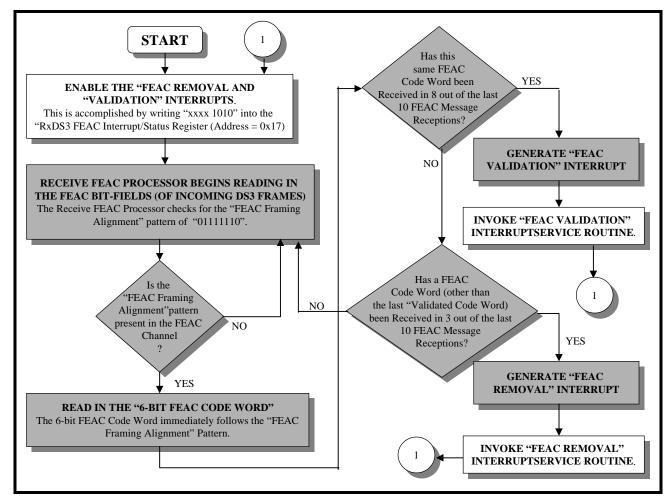

| RXDS3 FEAC INTERROPT ENABLE/STATUS REGISTER (ADDRESS = 0x17)                                                    |     |

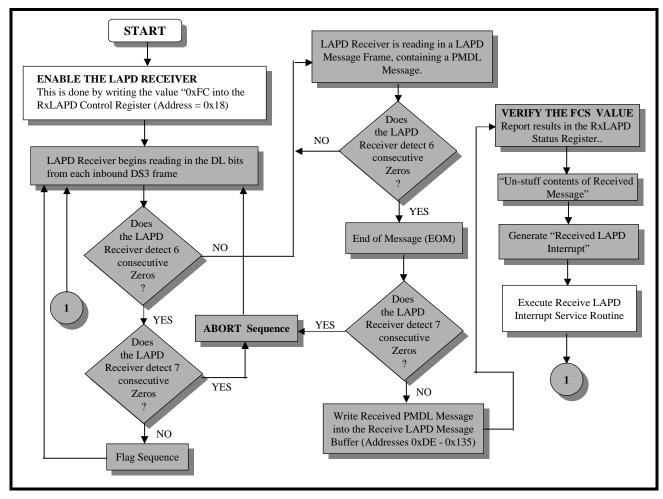

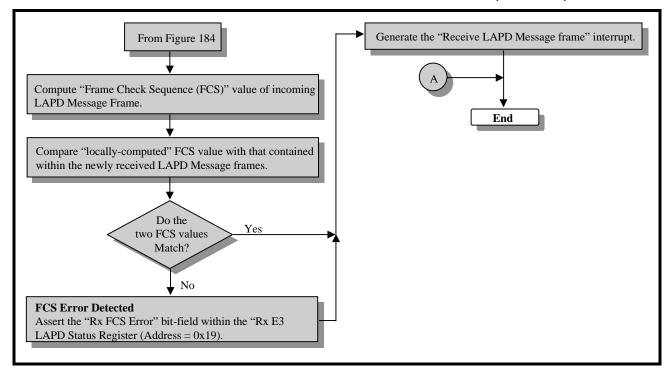

| RXDS3 LAPD STATUS REGISTER (ADDRESS = 0x19)                                                                     |     |

| 2.4.3 Receive E3 Framer Configuration Registers (ITU-T G.832)                                                   |     |

| RXE3 CONFIGURATION & STATUS REGISTER 1 (ADDRESS = 0x10)                                                         |     |

| RXE3 CONFIGURATION & STATUS REGISTER 2 (ADDRESS = 0x11)                                                         |     |

| RXE3 INTERRUPT ENABLE REGISTER - 1 (ADDRESS = 0X12)                                                             | 32  |

| RXE3 INTERRUPT ENABLE REGISTER - 2 (ADDRESS = 0x13)                                                             |     |

| RXE3 INTERRUPT STATUS REGISTER - 1 (ADDRESS = 0x14)                                                             |     |

| RXE3 INTERRUPT STATUS REGISTER - 2 (ADDRESS = 0x15)                                                             |     |

| RXE3 LAPD CONTROL REGISTER (ADDRESS = 0x18)                                                                     |     |

### ADVANCED CONFIDENTIAL

| REV. I | P1.1.2 |

|--------|--------|

|--------|--------|

| RxE3 LAPD Status Register (Address = 0x19)                                 | 96  |

|----------------------------------------------------------------------------|-----|

| RXE3 NR BYTE REGISTER (ADDRESS = 0X19)                                     |     |

| RXE3 GC BYTE REGISTER (ADDRESS = 0X1B)                                     |     |

|                                                                            |     |

| RxE3 TTB-0 Register (Address = 0x1C)                                       |     |

| RXE3 TTB-1 REGISTER (ADDRESS = 0X1D)  RXE3 TTB-2 REGISTER (ADDRESS = 0X1E) |     |

| ,                                                                          |     |

| RXE3 TTB-3 REGISTER (ADDRESS = 0X1F)                                       |     |

| RXE3 TTB-4 REGISTER (ADDRESS = 0X20)                                       |     |

| RXE3 TTB-5 REGISTER (ADDRESS = 0x21)                                       |     |

| RXE3 TTB-6 REGISTER (ADDRESS = 0X22)                                       |     |

| RXE3 TTB-7 REGISTER (ADDRESS = 0X23)                                       |     |

| RXE3 TTB-8 REGISTER (ADDRESS = 0X24)                                       |     |

| RXE3 TTB-9 REGISTER (ADDRESS = 0x25)                                       |     |

| RXE3 TTB-10 REGISTER (ADDRESS = 0x26)                                      |     |

| RXE3 TTB-11 REGISTER (ADDRESS = 0x27)                                      |     |

| RXE3 TTB-12 REGISTER (ADDRESS = 0X28)                                      |     |

| RXE3 TTB-13 REGISTER (ADDRESS = 0X29                                       |     |

| RXE3 TTB-14 REGISTER (ADDRESS = 0x2A)                                      |     |

| RXE3 TTB-15 REGISTER (ADDRESS = 0X2B)                                      |     |

| RXE3 SSM REGISTER (ADDRESS = 0X2B)                                         |     |

| 2.4.4 Receive E3 Framer Configuration Registers (ITU-T G.751)              |     |

| RXE3 CONFIGURATION & STATUS REGISTER - 1 G.751 (ADDRESS = 0x10)            |     |

| RXE3 CONFIGURATION & STATUS REGISTER - 2 (ADDRESS = 0x11)                  |     |

| RXE3 INTERRUPT ENABLE REGISTER - 1 (ADDRESS = 0x12)                        |     |

| RXE3 INTERRUPT ENABLE REGISTER - 2 (ADDRESS = 0x13)                        |     |

| RXE3 INTERRUPT STATUS REGISTER - 1 (ADDRESS = 0x14)                        |     |

| RXE3 INTERRUPT STATUS REGISTER - 2 (ADDRESS = 0x15)                        |     |

| RXE3 LAPD CONTROL REGISTER (ADDRESS = 0x18)                                |     |

| RXE3 LAPD STATUS REGISTER (ADDRESS = 0x19)                                 |     |

| RXE3 SERVICE BIT REGISTER (ADDRESS = 0x1A)                                 |     |

| 2.4.5 Transmit DS3 Configuration Registers                                 |     |

| TRANSMIT DS3 CONFIGURATION REGISTER (ADDRESS = 0x30)                       |     |

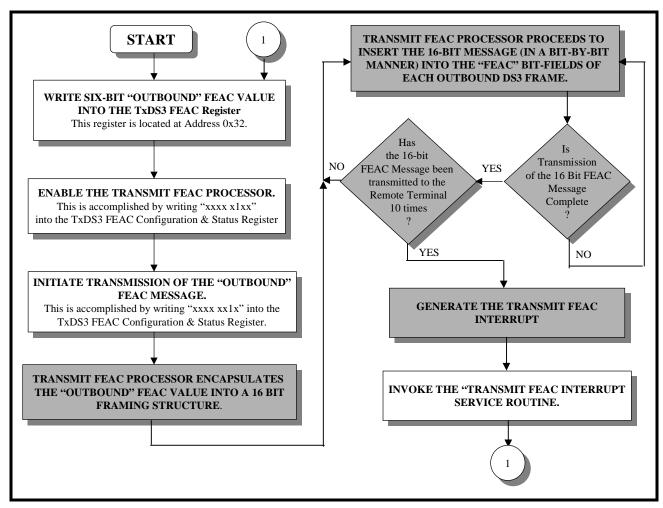

| TRANSMIT DS3 FEAC CONFIGURATION & STATUS REGISTER (ADDRESS = 0x31)         |     |

| TXDS3 FEAC REGISTER (ADDRESS = 0x32)                                       |     |

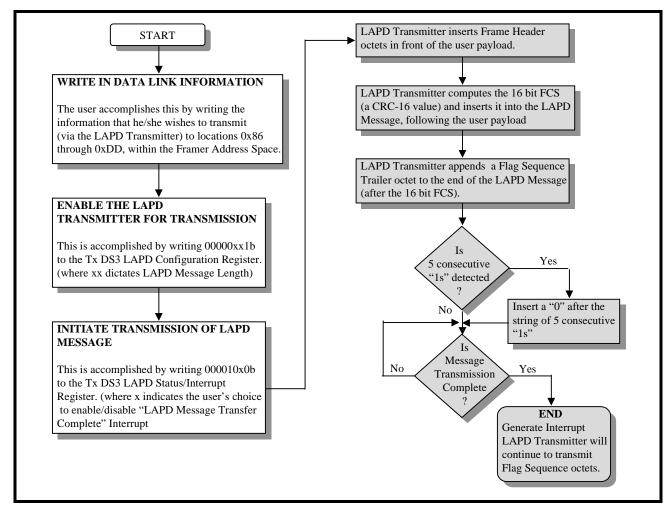

| TXDS3 LAPD CONFIGURATION REGISTER (ADDRESS = 0x33)                         |     |

| TXDS3 LAPD STATUS AND INTERRUPT REGISTER (ADDRESS = 0X34)                  |     |

| TXDS3 M-BIT MASK REGISTER (ADDRESS = 0X35)                                 |     |

| TxDS3 F-Bit Mask Register - 1 (Address = 0x36)                             |     |

| TXDS3 F-Bit Mask Register - 2 (Address = 0x37)                             |     |

| TXDS3 F-Bit Mask Register - 3 (Address = 0x38)                             |     |

| TxDS3 F-Bit Mask Register - 4 (Address = 0x39)                             |     |

| 2.4.6 Transmit E3 (ITU-T G.832) Configuration Registers                    |     |

| TXE3 CONFIGURATION REGISTER (ADDRESS = 0x30)                               |     |

| TXE3 LAPD CONFIGURATION REGISTER (ADDRESS = 0x33)                          |     |

| TXE3 LAPD STATUS AND INTERRUPT REGISTER (ADDRESS = 0x34)                   |     |

| TXE3 GC BYTE REGISTER (ADDRESS = 0X35)                                     |     |

| TXE3 MA BYTE REGISTER (ADDRESS = 0X36)                                     |     |

| TXE3 MA BYTE REGISTER (ADDRESS = 0X36)                                     |     |

| TXE3 NR BYTE REGISTER (ADDRESS = 0X37)                                     |     |

| TXE3 TTB-0 REGISTER (ADDRESS = 0x38)                                       |     |

| TXE3 TTB-1 REGISTER (ADDRESS = 0x39)                                       |     |

| TXE3 TTB-2 REGISTER (ADDRESS = 0x3A)                                       |     |

| TXE3 TTB-3 REGISTER (ADDRESS = 0X3B)                                       |     |

| TXE3 TTB-4 REGISTER (ADDRESS = 0x3C)                                       |     |

| TxE3 TTB-5 Register (Address = 0x3D)                                       | 111 |

|  | IM |  |  |

|--|----|--|--|

| 444        |

|------------|

| 111        |

| 111        |

| 112        |

| 112        |

| 113        |

| 113        |

| 113        |

| 114        |

| 114        |

| 114        |

| 115        |

| 115        |

| 115        |

| 116        |

| 116        |

| 117        |

| 118        |

| 119        |

| 119        |

| 119        |

| 120        |

| 120        |

| . 120      |

| 121        |

| 121        |

| 121        |

| 121        |

| 122        |

| 122        |

| 122        |

| 123        |

| 123        |

| 123        |

| 123<br>124 |

|            |

| . 124      |

| 124        |

| 125        |

| 125        |

| 125        |

| 126        |

| 128        |

| 129        |

| 129        |

| 130        |

| 130        |

| 130        |

| HANNEL     |

| 131        |

| LICA-      |

| 131        |

| G.832      |

| 131        |

| G.751      |

| 132        |

| 132        |

|            |

| ADV | MCED | CONFID | ENTIAL |

|-----|------|--------|--------|

**EXAR**

|    | IAMI | CED ( | ONE       | IDENT | ΊΔΙ |

|----|------|-------|-----------|-------|-----|

| AU |      |       | , CJIVI I |       |     |

|     | BLOCK INTERRUPT ENABLE REGISTER (ADDRESS = 0x04)                                                      | 133      |

|-----|-------------------------------------------------------------------------------------------------------|----------|

|     | TABLE 10: INTERRUPT SERVICE ROUTINE GUIDE (FOR DS3 APPLICATIONS)                                      | 133      |

|     | TABLE 11: INTERRUPT SERVICE ROUTINE GUIDE (FOR E3, ITU-T G.832 APPLICATIONS)                          | 134      |

|     | TABLE 12: INTERRUPT SERVICE ROUTINE GUIDE (FOR E3, ITU-T G.751 APPLICATIONS)                          | 134      |

|     | 2.7.1 Automatic Reset of Interrupt Enable Bits                                                        |          |

|     | FRAMER OPERATING MODE REGISTER (ADDRESS = 0x00)                                                       | 135      |

|     | 2.7.2 One-Second Interrupts                                                                           | 135      |

|     | 2.8 INTERFACING THE FRAMER TO AN INTEL-TYPE MICROPROCESSOR                                            | 135      |

|     | Table 13: Alternate Functions of Port 3 Pins                                                          |          |

|     | TABLE 14: INTERRUPT SERVICE ROUTINE LOCATION (IN CODE MEMORY) FOR THE INTO* AND INT1* INTERINPUT PINS |          |

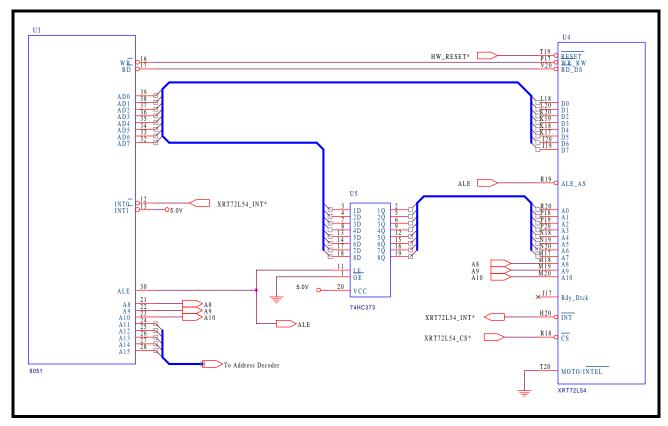

|     | Figure 37. Schematic depicting how to interface the XRT72L54 DS3/E3 Framer IC to the 8051 Micro       |          |

|     | troller                                                                                               |          |

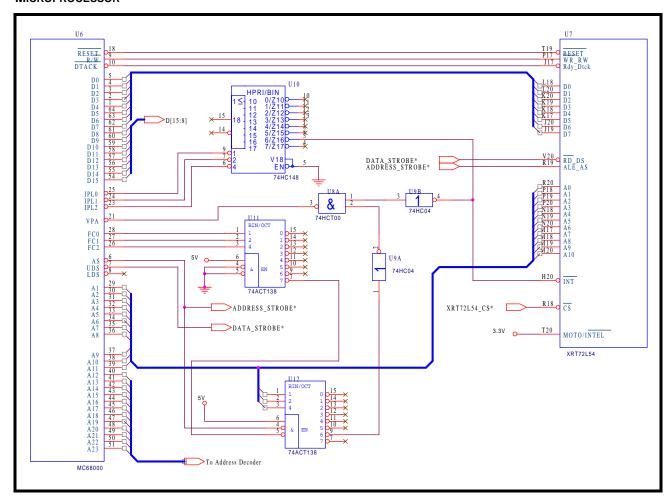

|     | 2.9 INTERFACING THE FRAMER IC TO A MOTOROLA-TYPE MICROPROCESSOR                                       |          |

|     | Figure 38. Schematic Depicting how to interface the XRT72L54 DS3/E3 Framer IC to the MC68000          |          |

|     | processor                                                                                             |          |

|     | TABLE 15: AUTO-VECTOR TABLE FOR THE MC68000 MICROPROCESSOR                                            |          |

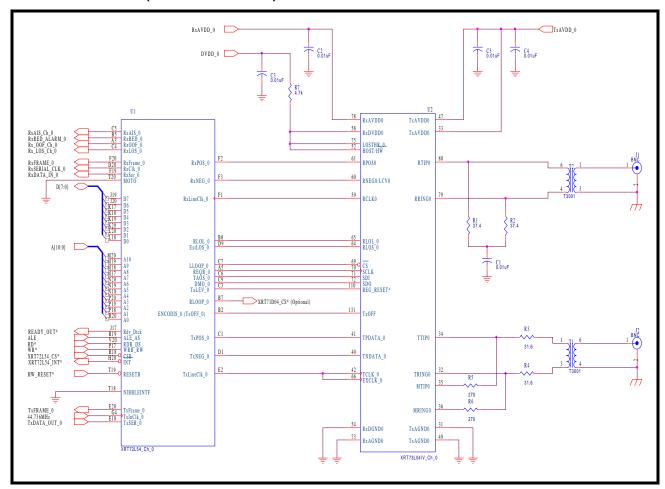

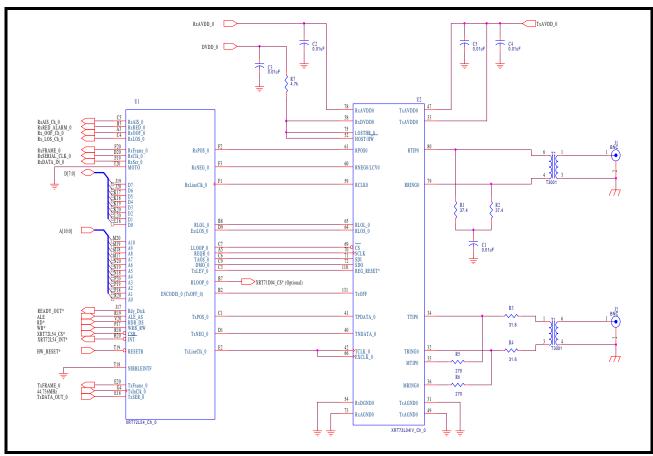

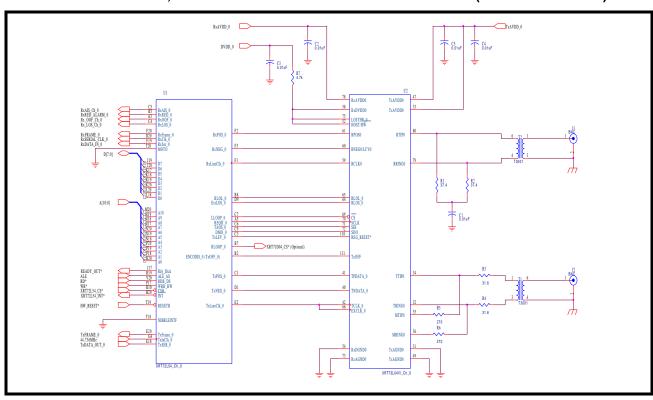

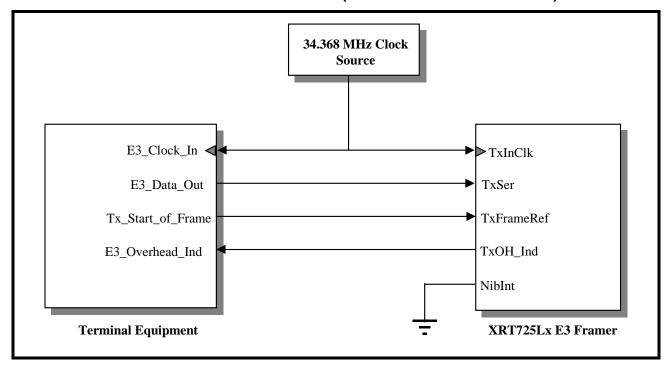

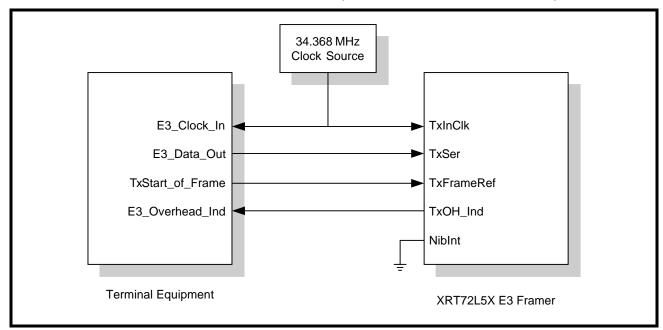

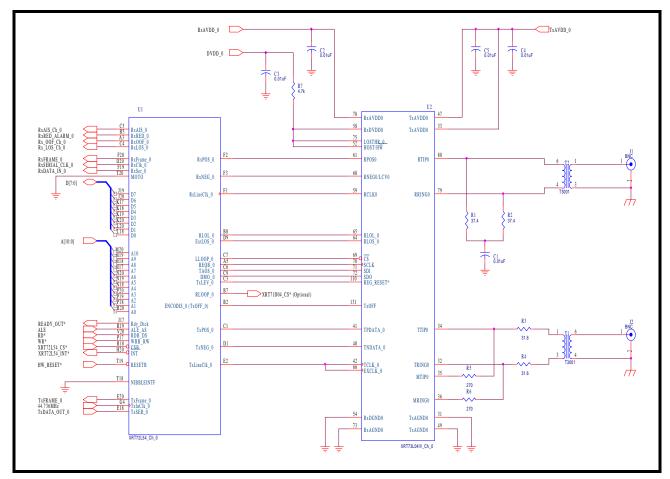

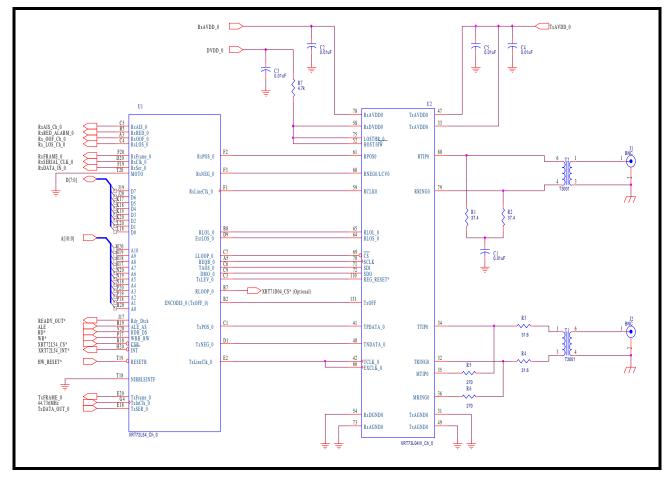

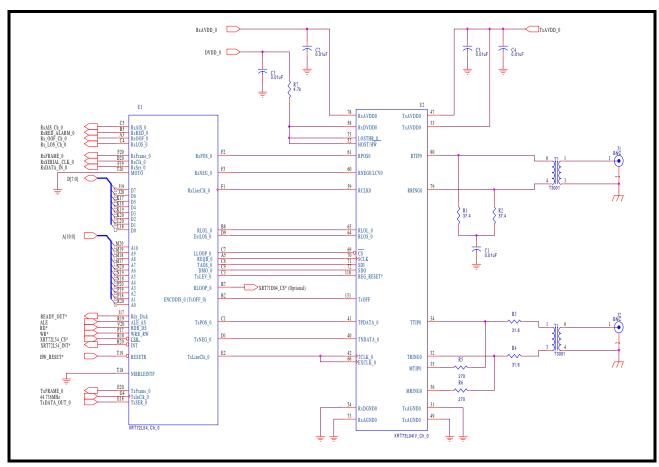

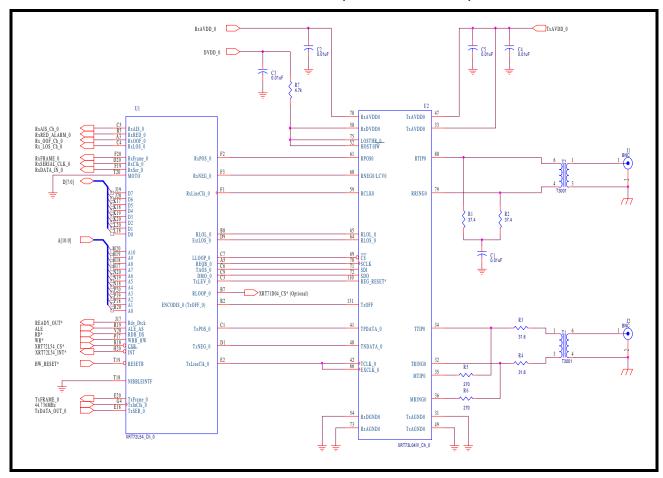

| 3.0 | The Line Interface and scan section                                                                   |          |

|     | Figure 39. Schematic Depicting how to interface the XRT72L54 DS3/E3 Framer IC to the XRT73L04         |          |

|     | E3/STS-1 LIU IC (one channel shown)                                                                   |          |

|     | 3.1 BIT-FIELDS WITHIN THE LINE INTERFACE DRIVE REGISTER                                               |          |

|     | LINE INTERFACE DRIVE REGISTER (ADDRESS = 0x80)                                                        |          |

|     | TABLE 16: THE RELATIONSHIP BETWEEN THE STATES OF RLOOP, LLOOP AND THE RESULTING LOOP-BACK             |          |

|     | WITH THE XRT7300 DEVICE                                                                               |          |

|     | 3.2 BIT-FIELDS WITHIN THE LINE INTERFACE SCAN REGISTER                                                |          |

|     | LINE INTERFACE sCAN REGISTER (ADDRESS = 0x81)                                                         | 143      |

| XF  | T72L54 CONFIGURATION                                                                                  |          |

|     | DS3 Operation of the XRT72L54                                                                         |          |

|     | FRAMER OPERATING MODE REGISTER (ADDRESS = 0x00)                                                       |          |

|     | 4.1 DESCRIPTION OF THE DS3 FRAMES AND ASSOCIATED OVERHEAD BITS                                        |          |

|     | Figure 40. DS3 Frame Format for C-bit Parity                                                          |          |

|     | Figure 41. DS3 Frame Format for M13                                                                   |          |

|     | FRAMER OPERATING MODE REGISTER (ADDRESS = 0x00)                                                       |          |

|     | TABLE 17: THE RELATIONSHIP BETWEEN THE CONTENT OF BIT 2, (C-BIT PARITY*/M13) WITHIN THE FRAME         |          |

|     | ERATING MODE REGISTER AND THE RESULTING DS3 FRAMING FORMAT                                            |          |

|     | TABLE 18: C-BIT FUNCTIONS FOR THE C-BIT PARITY DS3 FRAME FORMAT                                       |          |

|     | 4.1.1 Frame Synchronization Bits (Applies to both M13 and C-bit Parity Framing Formats)               | _        |

|     | 4.1.2 Performance Monitoring/Error Detection Bits (Parity)                                            |          |

|     | 4.1.3 Alarm and Signaling-Related Overhead Bits                                                       | 147      |

|     | Valid M-bits, F-bits, and P-bits                                                                      | 147      |

|     | 4.1.4 The Data Link Related Overhead Bits                                                             | 148      |

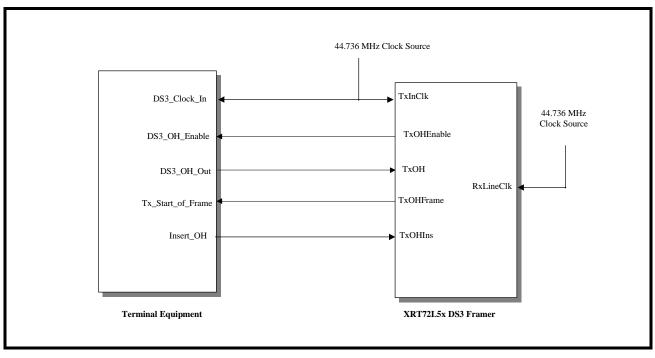

|     | 4.2 THE TRANSMIT SECTION OF THE XRT72L54 (DS3 MODE OPERATION)                                         | 148      |

|     | Figure 42. A Simple Illustration of the Transmit Section, within the XRT72L54, when it has been confi | gured    |

|     | to operate in the DS3 Mode                                                                            |          |

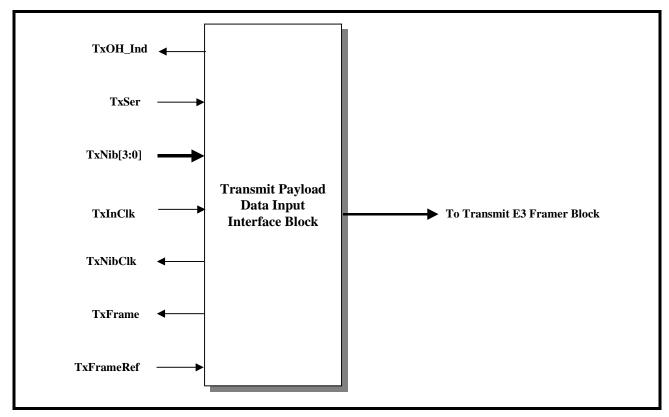

|     | 4.2.1 The Transmit Payload Data Input Interface Block                                                 |          |

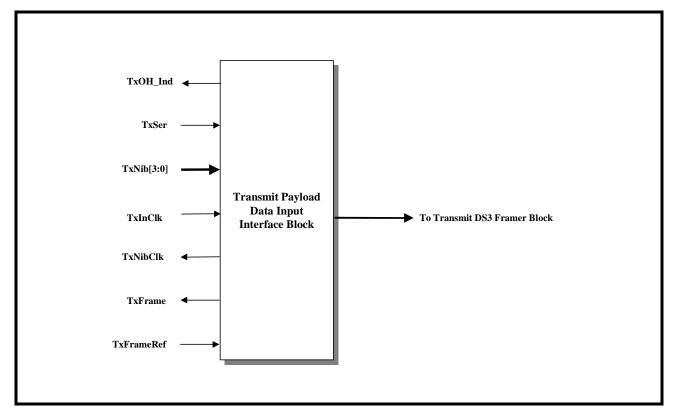

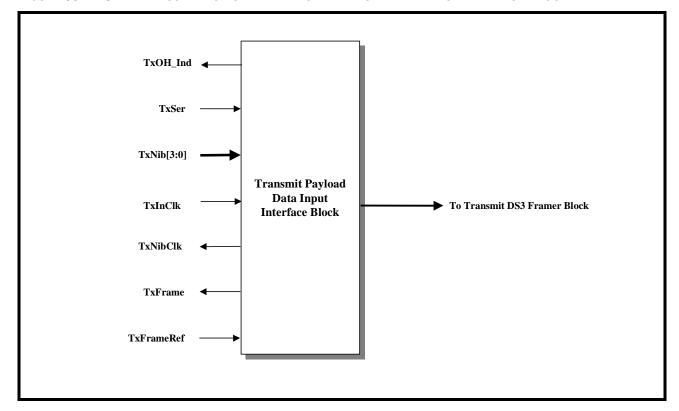

|     | Figure 43. A Simple Illustration of the Transmit Payload Data Input Interface Block                   | 150      |

|     | TABLE 19: LISTING AND DESCRIPTION OF THE PINS ASSOCIATED WITH THE TRANSMIT PAYLOAD DATA INPI          | JT IN-   |

|     | TERFACE                                                                                               | 151      |

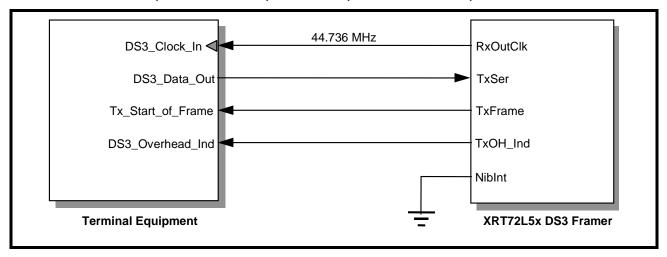

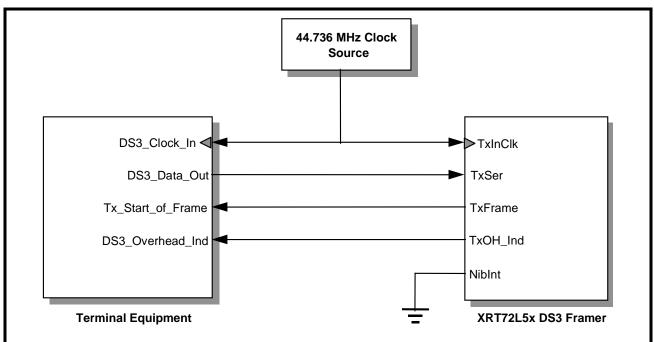

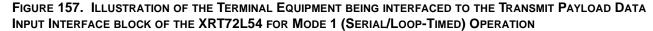

|     | Figure 44. Illustration of the Terminal Equipment being interfaced to the Transmit Payload Data Input | t Inter- |

|     | face block (of the XRT72L54) for Mode 1(Serial/Loop-Timing) Operation                                 | 153      |

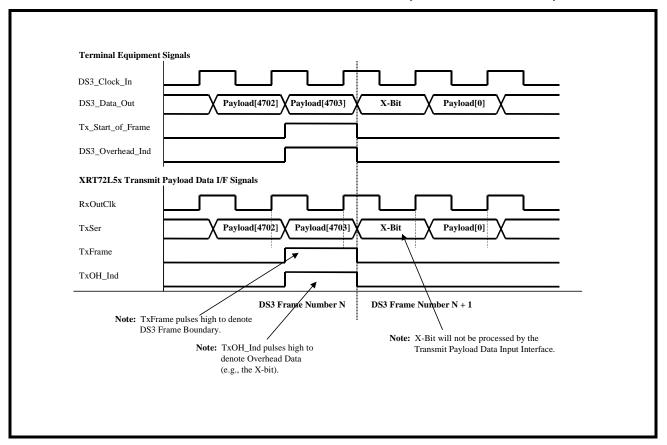

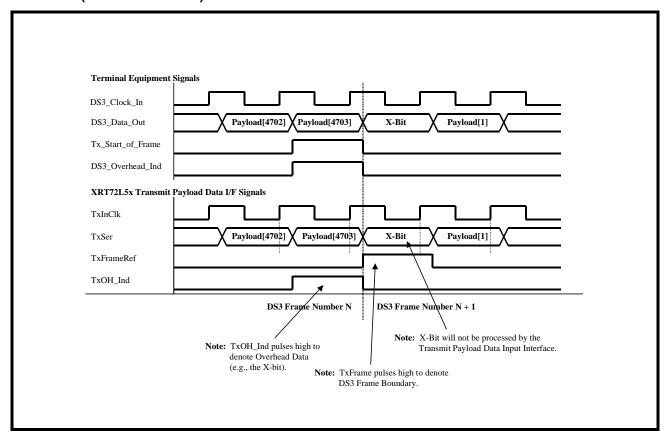

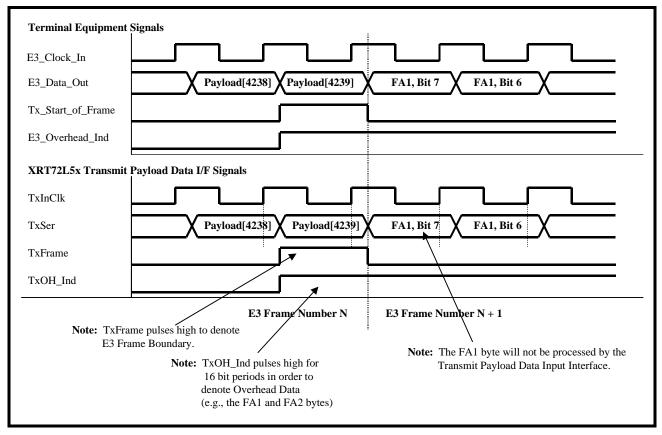

|     | Figure 45. Behavior of the Terminal Interface signals between the Transmit Payload Data Input Inte    | rface    |

|     | block of the XRT72L54 and the Terminal Equipment (for Mode 1 Operation)                               | 154      |

|     | FRAMER OPERATING MODE REGISTER (ADDRESS = 0x00)                                                       | 154      |

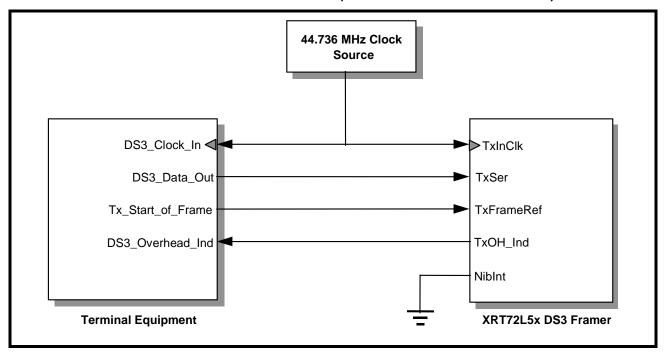

|     | Figure 46. Illustration of the Terminal Equipment being interfaced to the Transmit Payload Data Input | t Inter- |

|     | face block of the XRT72L54 for Mode 2 (Serial/Local-Timed/Frame-Slave) Operation                      | 155      |

|     |                                                                                                       |          |

| Figure 47. Behavior of the Terminal Interface signals between the XRT72L54 and the Terminal Equipment 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| (Mode 2 Operation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| Framer Operating Mode Register (Address = 0x00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| Figure 48. Illustration of the Terminal Equipment being interfaced to the Transmit Payload Data Inpu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | t Inter- |

| face block of the XRT72L54 for Mode 3 (Serial/Local-Timed/Frame-Master) Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 157      |

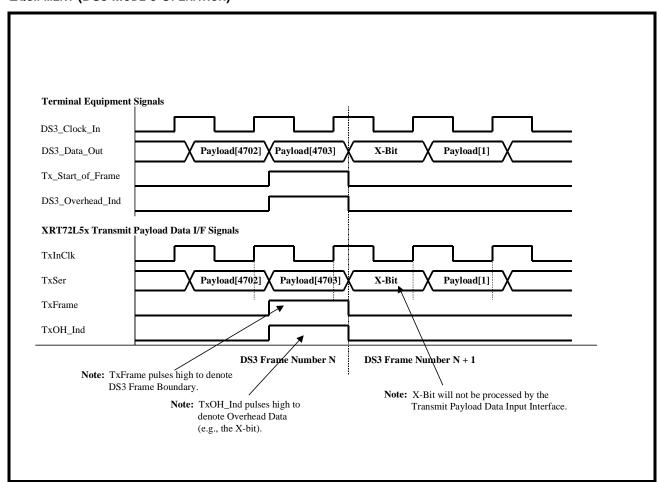

| Figure 49. Behavior of the Terminal Interface signals between the XRT72L54 and the Terminal Equipment 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

| (DS3 Mode 3 Operation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 158      |

| FRAMER OPERATING MODE REGISTER (ADDRESS = 0x00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 159      |

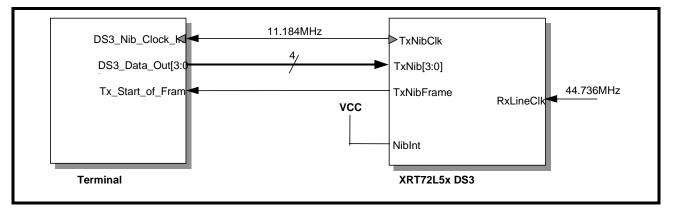

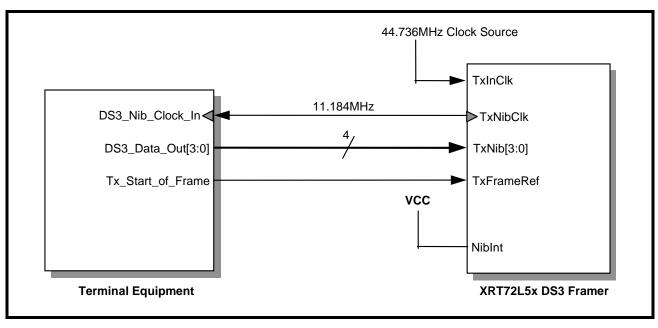

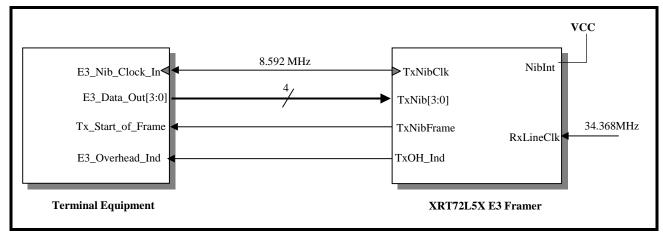

| Figure 50. Illustration of the Terminal Equipment being interfaced to the Transmit Payload Data Inpu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

| face block of the XRT72L54 for Mode 4 (Nibble-Parallel/Loop-Timed) Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 160      |

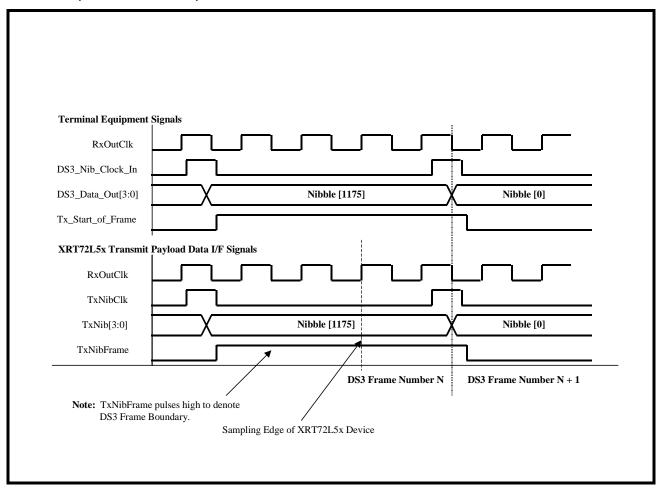

| Figure 51. Behavior of the Terminal Interface signals between the XRT72L54 and the Terminal Equipment of the Terminal Equipment (Interface signals between the Interface signals signals between the Interface signals between the Interface signals signa | oment    |

| (Mode 4 Operation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 161      |

| Framer Operating Mode Register (Address = 0x00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 161      |

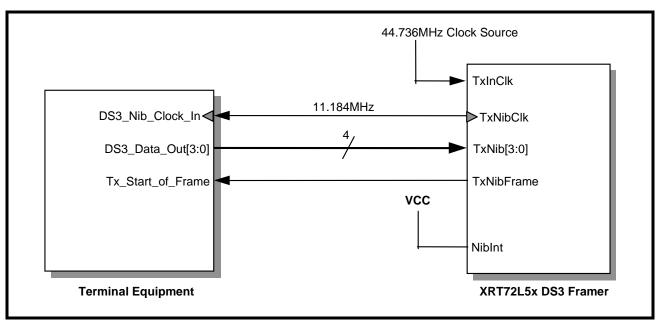

| Figure 52. Illustration of the Terminal Equipment being interfaced to the Transmit Payload Data Inpu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | t Inter- |

| face block of the XRT72L54 for Mode 5 (Nibble-Parallel/Local-Timed/Frame-Slave) Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 163      |

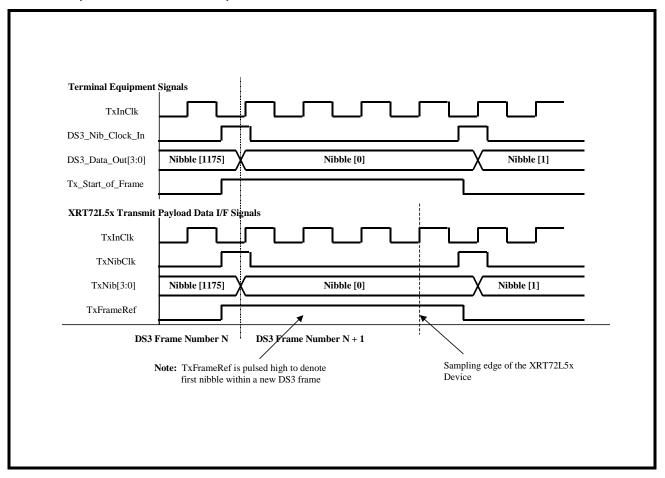

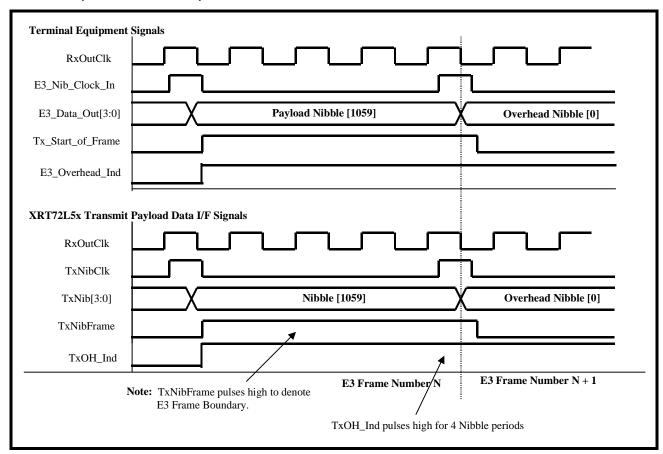

| Figure 53. Behavior of the Terminal Interface signals between the XRT72L54 and the Terminal Equip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | oment    |

| (DS3 Mode 5 Operation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

| Framer Operating Mode Register (Address = 0x00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 164      |

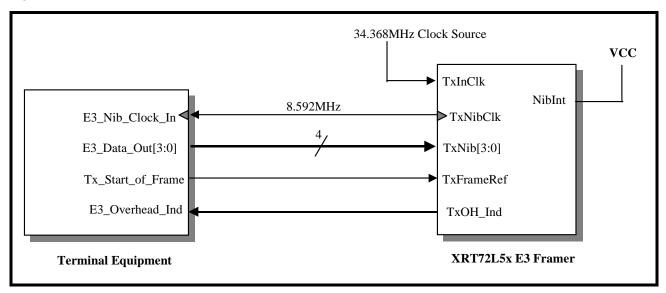

| Figure 54. Illustration of the Terminal Equipment being interfaced to the Transmit Payload Data Inpu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | t Inter- |

| face block of the XRT72L54 for Mode 6 (Nibble-Parallel/Local-Timed/Frame-Master) Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 165      |

| Figure 55. Behavior of the Terminal Interface signals between the XRT72L54 and the Terminal Equip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | oment    |

| (DS3 Mode 6 Operation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 166      |