# ENHANCED T1/E1/OC3 WAN PLL WITH DUAL REFERENCE INPUTS

82V3155

# FEATURES

- Supports AT&T TR62411 and Telcordia GR-1244-CORE Stratum 3, Stratum 4 Enhanced and Stratum 4 clock, OC-3 port and 155.52 Mbit/s application

- Supports ITU-T G.813 Option 1 clocks

- Supports ITU-T G.812 Type IV clocks

- Supports ETSI ETS 300 011, TBR 4, TBR 12 and TBR 13 timing for E1 interface

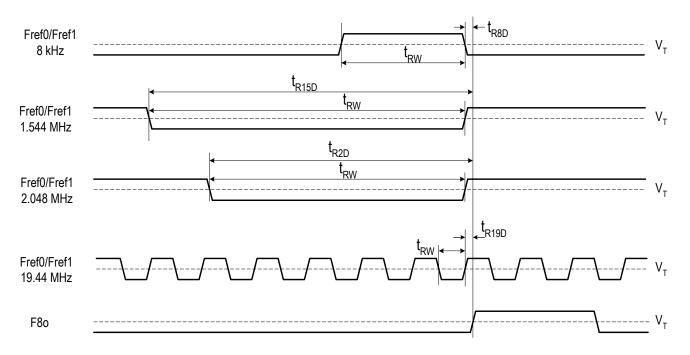

- Selectable reference inputs: 8 kHz, 1.544 MHz, 2.048 MHz or 19.44 MHz

- Accepts two independent reference inputs which may have same or different nominal frequencies applied to them

- Provides C1.50, C30, C20, C40, C60, C80, C160, C190, C320 and C155 output clock signals

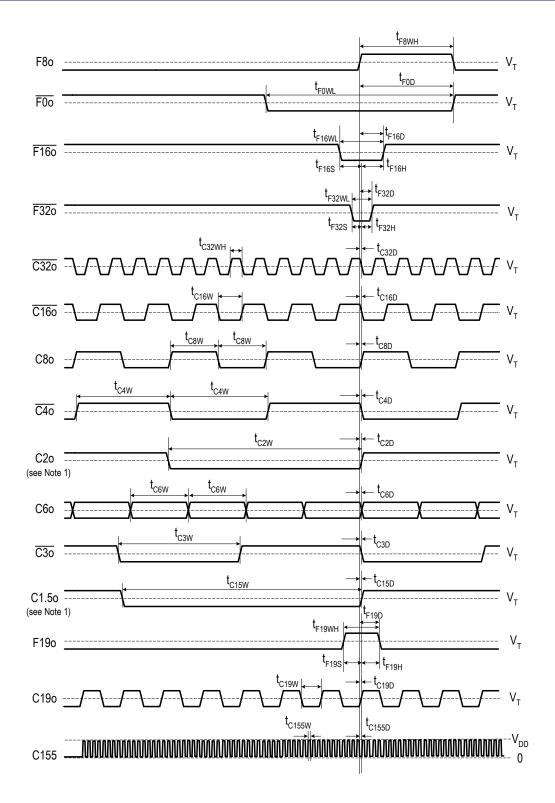

- Provides 7 types of 8 kHz framing pulses: F0o, F8o, F16o, F19o,F32o, RSP and TSP

- Provides a C2/C1.5 output clock signal with the frequency controlled by the selected reference input Fref0 or Fref1

- Holdover frequency accuracy of 0.025 ppm

- Phase slope of 5 ns per 125 µs

- Attenuates wander from 2.1 Hz

- Fast lock mode

- Provides Time Interval Error (TIE) correction

- MTIE of 600 ns

- JTAG boundary scan

- · Holdover status indication

- Freerun status indication

- Normal status indication

- Lock status indication

- Input reference quality indication

- 3.3 V operation with 5 V tolerant I/O

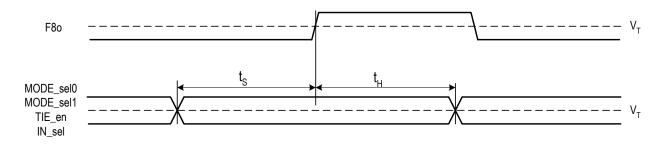

- Package available: 56-pin SSOP (Green option available)

- For functional replacement use 82P33714ANLG

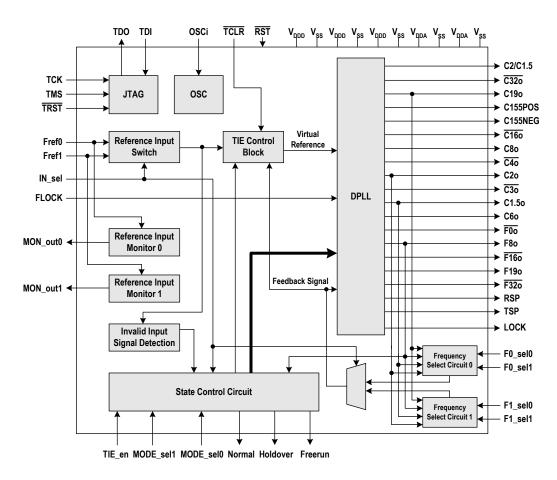

# FUNCTIONAL BLOCK DIAGRAM

IDT and the IDT logo are trademarks of Integrated Device Technology, Inc.

DSC-6244/3

#### ENHANCED T1/E1/OC3 WAN PLL WITH DUAL REFERENCE INPUTS

### IDT82V3155

# DESCRIPTION

The 82V3155 is an enhanced T1/E1/OC3 WAN PLL with dual reference inputs. It contains a Digital Phase-Locked Loop (DPLL), which generates low jitter ST-BUS, 19.44 MHz and 155.52 MHz clock and framing signals that are phase locked to an 8 kHz, 1.544 MHz, 2.048 MHz or 19.44 MHz input reference.

The 82V3155 provides 10 types of clock signals (C1.5o,  $\overline{C30}$ , C6o, C2o,  $\overline{C4o}$ , C8o,  $\overline{C16o}$ , C19o,  $\overline{C32o}$ , C155) and 7 types of framing signals (F0o, F8o, F16o, F19o, F32o, RSP, TSP) for multitrunk T1/E1 and STS3/OC3 links.

The IDT82V3155 is compliant with AT&T TR62411, Telcordia GR-

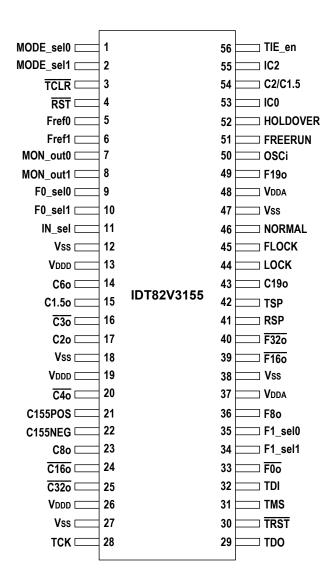

**PIN CONFIGURATION**

1244-CORE Stratum 3, Stratum 4 Enhanced, Stratum 4, OC-3 port, 155.52 Mbit/s application and ETSI ETS 300 011, ITU-T G.813 Option 1, and ITU-T G.812 Type IV clocks. It meets the jitter/wander tolerance, jitter/wander transfer, intrinsic jitter/wander, frequency accuracy, capture range, phase change slope, holdover frequency accuracy and MTIE (Maximum Time Interval Error) requirements for these specifications.

The 82V3155 can be used in synchronization and timing control for T1, E1 and OC3 systems, or used as ST-BUS clock and frame pulse source. It also can be used in access switch, access routers, ATM edge switches, wireless base station controllers, or IADs (Integrated Access Devices), PBXs, line cards and SONET/SDH equipments.

# **Table of Contents**

| 1 | Pin [       | Description                            | 7  |

|---|-------------|----------------------------------------|----|

| 2 | Fund        | ctional Description                    | 10 |

| - | 2.1         | State Control Circuit                  |    |

|   |             | 2.1.1 Normal Mode                      |    |

|   |             | 2.1.2 Fast Lock Mode                   |    |

|   |             | 2.1.3 Holdover Mode                    |    |

|   |             | 2.1.4 Freerun Mode                     |    |

|   | 2.2         | Frequency Select Circuit               |    |

|   | 2.2         |                                        |    |

|   |             | Reference Input Switch                 |    |

|   | 2.4         | Reference Input Monitor                |    |

|   | 2.5         | Invalid Input Signal Detection         |    |

|   | 2.6         | TIE Control Block                      |    |

|   | 2.7         |                                        |    |

|   |             | 2.7.1 Phase Detector (PHD)             |    |

|   |             | 2.7.2 Limiter                          |    |

|   |             | 2.7.3 Loop Filter                      |    |

|   |             | 2.7.4 Fraction Block                   |    |

|   |             | 2.7.5 Digital Control Oscillator (DCO) |    |

|   |             | 2.7.6 Lock Indicator                   |    |

|   |             | 2.7.7 Output Interface                 | 15 |

|   | 2.8         | OSC                                    | 16 |

|   |             | 2.8.1 Clock Oscillator                 | 16 |

|   | 2.9         | JTAG                                   | 16 |

|   | 2.10        | Reset Circuit                          | 16 |

|   | 2.11        | Power Supply Filtering Techniques      | 17 |

| 3 | Meas        | sures of Performance                   | 18 |

| • | 3.1         | Intrinsic Jitter                       |    |

|   | 3.2         | Jitter Tolerance                       |    |

|   | 3.3         | Jitter Transfer                        |    |

|   | 3.4         | Frequency Accuracy                     |    |

|   | 3.5         | Holdover Accuracy                      |    |

|   | 3.6         | Capture Range                          |    |

|   | 3.7         | Lock Range                             |    |

|   | 3.8         | Phase Slope                            |    |

|   | 3.9         | Time Interval Error (TIE)              |    |

|   | 3.9<br>3.10 |                                        | 10 |

|   | ••          |                                        |    |

|   |             | Phase Continuity<br>Phase Lock Time    |    |

|   |             |                                        |    |

| 4 | Abso        | olute Maximum Ratings                  | 20 |

| 5 | Reco        | ommended DC Operating Conditions       | 20 |

| 6 | DC E        | Electrical Characteristics             | 20 |

| ~ | 6.1         | Single End Input/Output Port           |    |

|   | 6.2         | Differential Output Port (LVDS)        |    |

| 7 |             | Electrical Characteristics             |    |

| 1 |             | LICUI ICAI VIIAI AUCI ISUUS            |    |

|   | 7.1   | Performance<br>Intrinsic Jitter Unfiltered<br>C1.5o (1.544 MHz) Intrinsic Jitter Filtered<br>C2o (2.048 MHz) Intrinsic Jitter Filtered<br>C19o (19.44 MHz) Intrinsic Jitter Filtered<br>C155 (155.52 MHz) Intrinsic Jitter Filtered<br>8 kHz Input to 8 kHz Output Jitter Transfer | .22 |  |  |  |  |

|---|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|--|

|   | 7.2   | Intrinsic Jitter Unfiltered                                                                                                                                                                                                                                                        | .22 |  |  |  |  |

|   | 7.3   | C1.50 (1.544 MHz) Intrinsic Jitter Filtered                                                                                                                                                                                                                                        | .23 |  |  |  |  |

|   | 7.4   | C2o (2.048 MHz) Intrinsic Jitter Filtered                                                                                                                                                                                                                                          | .23 |  |  |  |  |

|   | 7.5   | C19o (19.44 MHz) Intrinsic Jitter Filtered                                                                                                                                                                                                                                         | .23 |  |  |  |  |

|   | 7.6   | C155 (155.52 MHz) Intrinsic Jitter Filtered                                                                                                                                                                                                                                        | .23 |  |  |  |  |

|   | 7.7   | 8 kHz Input to 8 kHz Output Jitter Transfer                                                                                                                                                                                                                                        | .24 |  |  |  |  |

|   | 7.8   | 1.544 MHz Input to 1.544 MHz Output Jitter Transfer                                                                                                                                                                                                                                | .24 |  |  |  |  |

|   | 7.9   | 2.048 MHz Input to 2.048 MHz Output Jitter Transfer                                                                                                                                                                                                                                | .25 |  |  |  |  |

|   | 7.10  | 2.048 MHz Input to 2.048 MHz Output Jitter Transfer                                                                                                                                                                                                                                | .25 |  |  |  |  |

|   | 7.11  | 8 kHz Input Jitter Tolerance                                                                                                                                                                                                                                                       | .25 |  |  |  |  |

|   | 7.12  | 1.544 MHz Input Jitter Tolerance                                                                                                                                                                                                                                                   | .27 |  |  |  |  |

|   | 7.13  | 2.048 MHz Input Jitter Tolerance                                                                                                                                                                                                                                                   | .27 |  |  |  |  |

|   | 7.14  | 8 kHz Input Jitter Tolerance                                                                                                                                                                                                                                                       | .28 |  |  |  |  |

|   |       |                                                                                                                                                                                                                                                                                    |     |  |  |  |  |

|   | limin | g Characteristics                                                                                                                                                                                                                                                                  | .29 |  |  |  |  |

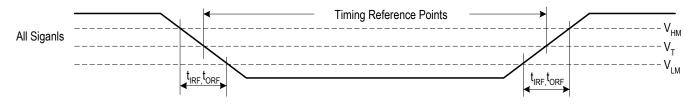

|   | 8.1   | Timing Parameter Measurement Voltage Levels                                                                                                                                                                                                                                        | .29 |  |  |  |  |

|   | 8.2   | Input/Output Timing                                                                                                                                                                                                                                                                | .29 |  |  |  |  |

| 9 | Order | Ordering Information                                                                                                                                                                                                                                                               |     |  |  |  |  |

4

# **List of Tables**

| Table - 1 | Operating Modes Selection        | 10 |

|-----------|----------------------------------|----|

|           | Fref0 Frequency Selection        | 11 |

|           | Fref1 Frequency Selection        | 11 |

|           | Input Reference Selection        | 12 |

|           | C2/C1.5 Output Frequency Control | 15 |

© 2019 Renesas Electronics Corporation

5

# **List of Figures**

| Figure - 1  | 82V3155 56-pin SSOP Package Pin Assignment 2     |      |

|-------------|--------------------------------------------------|------|

| Figure - 2  | State Control Circuit                            | . 10 |

| Figure - 3  | State Control Diagram                            | . 10 |

| Figure - 4  | TIE Control Block Diagram                        | . 12 |

| Figure - 5  | Reference Switch with TIE Control Block Enabled  | . 13 |

| Figure - 6  | Reference Switch with TIE Control Block Disabled | . 13 |

| Figure - 7  | DPLL Block Diagram<br>Clock Oscillator Circuit   | . 14 |

| Figure - 8  | Clock Oscillator Circuit                         | . 16 |

| Figure - 9  | Power-Up Reset Circuit                           | . 16 |

| Figure - 10 | 82V3155 Power Decoupling Scheme                  |      |

| Figure - 11 | Timing Parameter Measurement Voltage Levels      | . 29 |

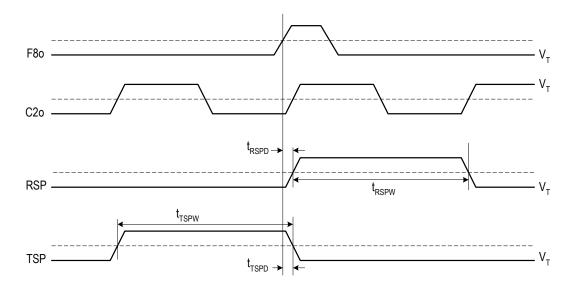

| Figure - 12 | Input to Output Timing (Normal Mode)             | . 31 |

| Figure - 13 | Output Timing 1                                  | . 32 |

| Figure - 14 | Output Timing 2                                  |      |

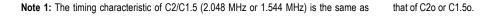

| Figure - 15 | Input Control Setup and Hold Timing              | . 33 |

© 2019 Renesas Electronics Corporation

# **1 PIN DESCRIPTION**

| Name                   | Туре     | Pin Number           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|------------------------|----------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

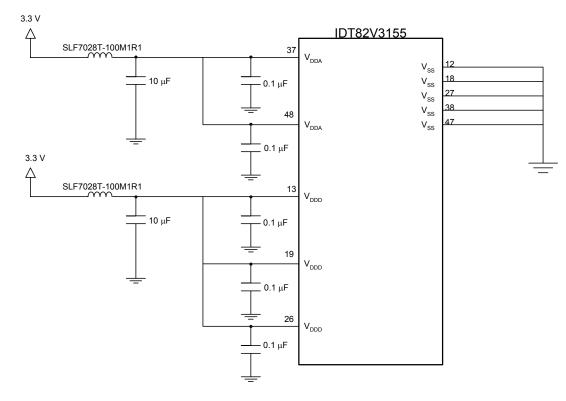

| V <sub>SS</sub>        | Power    | 12, 18, 27<br>38, 47 | Ground.<br>0 V. All V <sub>SS</sub> pins should be connected to the ground.                                                                                                                                                                                                                                                                                                                                                                                       |  |

| V <sub>DDA</sub>       | Power    | 37, 48               | 3.3 V Analog Power Supply.<br>Refer to Chapter 2.11 Power Supply Filtering Techniques.                                                                                                                                                                                                                                                                                                                                                                            |  |

| V <sub>DDD</sub>       | Power    | 13, 19, 26           | 3.3 V Digital Power Supply.<br>Refer to Chapter 2.11 Power Supply Filtering Techniques.                                                                                                                                                                                                                                                                                                                                                                           |  |

| OSCi                   | (CMOS) I | 50                   | Oscillator Master Clock Input.<br>This pin is connected to a clock source.                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Fref0<br>Fref1         | I        | 5<br>6               | Reference Input 0 and Reference Input 1.         These are two input reference sources (falling edge of 8 kHz, 1.544 MHz and 2.048 MHz or rising edge of 19.44 MHz) used for synchronization. The IN_sel pin determines which one of the two reference inputs to be used. See Table - 4 for details.         The frequency of the reference inputs can be 8 kHz, 1.544 MHz, 2.048 MHz or 19.44 MHz. These two pins are internally pulled up to V <sub>DDD</sub> . |  |

| IN_sel                 | Ι        | 11                   | Input Reference Selection.<br>A logic low at this pin selects Reference Input 0 (Fref0) and a logic high at this pin selects Reference Input 1 (Fref1).<br>The logic level on this input is gated in by the rising edges of F8o. This Pin is internally pulled down to V <sub>SS</sub> .                                                                                                                                                                          |  |

| F0_sel0<br>F0_sel1     | I        | 9<br>10              | Frequency Selection Inputs for Fref0.<br>These two inputs select one of the four possible frequencies (8 kHz, 1.544 MHz, 2.048 MHz or 19.44 MHz) for the Reference Input 0 (Fref0). See Table - 2 for details.                                                                                                                                                                                                                                                    |  |

| F1_sel0<br>F1_sel1     | Ι        | 35<br>34             | Frequency Selection Inputs for Fref1.<br>These two inputs select one of the four possible frequencies (8 kHz, 1.544 MHz, 2.048 MHz or 19.44 MHz) for the<br>Reference Input 1 (Fref1). These two pins are internally pulled down to V <sub>ss</sub> . See Table - 3 for details.                                                                                                                                                                                  |  |

| MODE_sel0<br>MODE_sel1 | I        | 1<br>2               | Mode Selection Inputs.<br>These two inputs determine the operating mode of the IDT82V3155 (Normal, Holdover or Freerun). See Table - 4<br>details.<br>The logic levels on these two pins are gated in by the rising edges of F8o. These two pins are internally pulled do<br>to V <sub>SS</sub> .                                                                                                                                                                 |  |

| RST                    | I        | 4                    | <b>Reset Input.</b><br>Pulling this pin to logic low for at least 300 ns will reset the IDT82V3155. While the RST pin is low, all framing and clock outputs are at logic high.<br>To ensure proper operation, the device must be reset after it is powered up.                                                                                                                                                                                                    |  |

| TCLR                   | Ι        | 3                    | <b>TIE Control Block Reset.</b><br>Pulling this pin to logic low for at least 300 ns will reset the TIE (Maximum Time Interval Error) control block and result in a realignment of the output phase with the input phase. This pin is internally pulled up to V <sub>DDD</sub> .                                                                                                                                                                                  |  |

| TIE_en                 | Ι        | 56                   | TIE Control Block Enable.<br>A logic high at this pin enables the TIE control block while a logic low disables it. The logic level on this input is gated in by the rising edges of F8o. This pin is internally pulled down to $V_{ss}$ .                                                                                                                                                                                                                         |  |

| FLOCK                  | ļ        | 45                   | Fast Lock Mode Enable.<br>When this pin is set to logic high, the DPLL will quickly lock to the input reference within 500 ms.                                                                                                                                                                                                                                                                                                                                    |  |

| LOCK                   | (CMOS) O | 44                   | Lock Indicator.<br>This output pin will go high when the DPLL is frequency locked to the input reference.                                                                                                                                                                                                                                                                                                                                                         |  |

| HOLDOVER               | (CMOS) O | 52                   | Holdover Indicator.<br>This output pin will go high whenever the DPLL enters Holdover mode.                                                                                                                                                                                                                                                                                                                                                                       |  |

| NORMAL                 | (CMOS) O | 46                   | Normal Indicator.<br>This output pin will go high whenever the DPLL enters Normal mode.                                                                                                                                                                                                                                                                                                                                                                           |  |

| FREERUN                | (CMOS) O | 51                   | Freerun Indicator.<br>This output pin will go high whenever the DPLL enters Freerun mode.                                                                                                                                                                                                                                                                                                                                                                         |  |

| MON_out0               | 0        | 7                    | Frequency Out-of-range Indicator for Fref0.<br>A logic high at this pin indicates that Fref0 is off the nominal frequency by more than $\pm 12$ ppm.                                                                                                                                                                                                                                                                                                              |  |

| Name               | Туре     | Pin Number | Description                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|--------------------|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MON_out1           | 0        | 8          | Frequency Out-of-range Indicator for Fref1.<br>A logic high at this pin indicates that Fref1 is off the nominal frequency by more than ±12 ppm.                                                                                                                                                                                                                                                                      |  |

| C155POS<br>C155NEG | (LVDS) O | 21<br>22   | 155.52 MHz Clock Output (LVDS Level).           This pair of pins output a 155.52 MHz clock, used for OC3/STS3 and SDH/SONET applications.                                                                                                                                                                                                                                                                           |  |

| C19o               | (CMOS) O | 43         | <b>19.44 MHz Clock Output (CMOS Level).</b><br>This output is a 19.44 MHz clock used for OC3/STS3 applications.                                                                                                                                                                                                                                                                                                      |  |

| <u>C320</u>        | (CMOS) O | 25         | 32.768 MHz Clock Output.<br>This output is a 32.768 MHz clock used for ST-BUS operation.                                                                                                                                                                                                                                                                                                                             |  |

| C160               | (CMOS) O | 24         | 16.384 MHz Clock Output.<br>This output is a 16.384 MHz clock used for ST-BUS operation.                                                                                                                                                                                                                                                                                                                             |  |

| C8o                | (CMOS) O | 23         | 8.192 MHz Clock Output.<br>This output is an 8.192 MHz clock used for ST-BUS operation.                                                                                                                                                                                                                                                                                                                              |  |

| <u>C4o</u>         | (CMOS) O | 20         | 4.096 MHz Clock Output.<br>This output is a 4.096 MHz clock used for ST-BUS operation.                                                                                                                                                                                                                                                                                                                               |  |

| C2o                | (CMOS) O | 17         | 2.048 MHz Clock Output.<br>This output is a 2.048 MHz clock used for ST-BUS operation.                                                                                                                                                                                                                                                                                                                               |  |

| <u>C30</u>         | (CMOS) O | 16         | 3.088 MHz Clock Output.<br>This output is a 3.088 MHz clock used for T1 applications.                                                                                                                                                                                                                                                                                                                                |  |

| C1.5o              | (CMOS) O | 15         | 1.544 MHz Clock Output.<br>This output is a 1.544 MHz clock used for T1 applications.                                                                                                                                                                                                                                                                                                                                |  |

| C6o                | (CMOS) O | 14         | 6.312 MHz Clock Output.<br>This output is a 6.312 MHz clock used for DS2 applications.                                                                                                                                                                                                                                                                                                                               |  |

| C2/C1.5            | (CMOS) O | 54         | <b>2.048 MHz or 1.544 MHz Clock Output.</b><br>This output is a 2.048 MHz or 1.544 MHz clock signal. If the selected reference input (Fref0 or Fref1) is 8 kHz, 2.048 MHz, or 19.44 MHz, the C2/C1.5 pin will output a 2.048 MHz clock signal. If the frequency of the selected reference input (Fref0 or Fref1) is 1.544 MHz, the C2/C1.5 pin will output a 1.544 MHz clock signal. Refer to Table - 5 for details. |  |

| F19o               | (CMOS) O | 49         | 8 kHz Frame Signal with 19.44 MHz Pulse Width.<br>This output is used for OC3/STS3 applications.                                                                                                                                                                                                                                                                                                                     |  |

| F320               | (CMOS) O | 40         | Frame Pulse ST-BUS 8.192 Mb/s.<br>This is an 8 kHz 30 ns active low framing pulse, which marks the beginning of an ST-BUS frame. This framing signal<br>is typically used for ST-BUS operation at 8.192 Mb/s.                                                                                                                                                                                                        |  |

| F160               | (CMOS) O | 39         | Frame Pulse ST-BUS 8.192 Mb/s.<br>This is an 8 kHz 61 ns active low framing pulse, which marks the beginning of an ST-BUS frame. This framing sig<br>is typically used for ST-BUS operation at 8.192 Mb/s.                                                                                                                                                                                                           |  |

| F8o                | (CMOS) O | 36         | Frame Pulse.<br>This is an 8 kHz 122 ns active high framing pulse, which marks the beginning of a frame.                                                                                                                                                                                                                                                                                                             |  |

| F0o                | (CMOS) O | 33         | Frame Pulse ST-BUS 2.048 Mb/s.<br>This is an 8 kHz 244 ns active low framing pulse, which marks the beginning of an ST-BUS frame. This framing signal is typically used for ST-BUS operation at 2.048 Mb/s and 4.096 Mb/s.                                                                                                                                                                                           |  |

| RSP                | (CMOS) O | 41         | Receive Sync Pulse.           This is an 8 kHz 488 ns active high framing pulse, which marks the beginning of a ST-BUS frame. This framing signal is typically used to connect to the Siemens MUNICH-32 device.                                                                                                                                                                                                      |  |

| TSP                | (CMOS) O | 42         | Transmit Sync Pulse.<br>This is an 8 kHz 488 ns active high framing pulse, which marks the beginning of an ST-BUS frame. This framing is typically used to connect to the Siemens MUNICH-32 device.                                                                                                                                                                                                                  |  |

| TDO                | (CMOS) O | 29         | Test Serial Data Out.<br>JTAG serial data is output on this pin on the falling edge of TCK. This pin is held in high impedance state when<br>JTAG scan is not enabled.                                                                                                                                                                                                                                               |  |

| TDI                | I        | 32         | <b>Test Serial Data In.</b><br>JTAG serial test instructions and data are shifted in on this pin. This pin is internally pulled up to V <sub>DDD</sub> .                                                                                                                                                                                                                                                             |  |

82V3155

### ENHANCED T1/E1/OC3 WAN PLL WITH DUAL REFERENCE INPUTS

| Name Type Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  | Pin Number                                          | Description                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |                                                     | <b>Test Reset.</b><br>Asynchronously initializes the JTAG TAP controller by putting it in the Test-Logic-Reset state. This pin is internally pulled up to V <sub>DDD</sub> . It is connected to the ground for normal applications. |

| TCK         I         28         Test Clock.           Provides the clock for the JTAG test logic.         Provides the clock for the JTAG test logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  | 28                                                  |                                                                                                                                                                                                                                     |

| TMS         I         31         Test Mode Select.<br>JTAG signal that controls the state transitions of the TAP of the test of tes |  | 31                                                  | Test Mode Select.<br>JTAG signal that controls the state transitions of the TAP controller. This pin is internally pulled up to V <sub>DDD</sub> .                                                                                  |

| IC0, IC2 - 53, 55 These pins should be connected to V <sub>SS</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  | These pins should be connected to V <sub>SS</sub> . |                                                                                                                                                                                                                                     |

# 2 FUNCTIONAL DESCRIPTION

The IDT82V3155 is a enhanced T1/E1/OC3 WAN PLL with dual reference inputs, providing timing (clock) and synchronization (framing) signals to interface circuits for multitrunk T1/E1 and STS3/OC3 links. The details are described in the following sections.

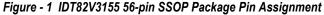

### 2.1 STATE CONTROL CIRCUIT

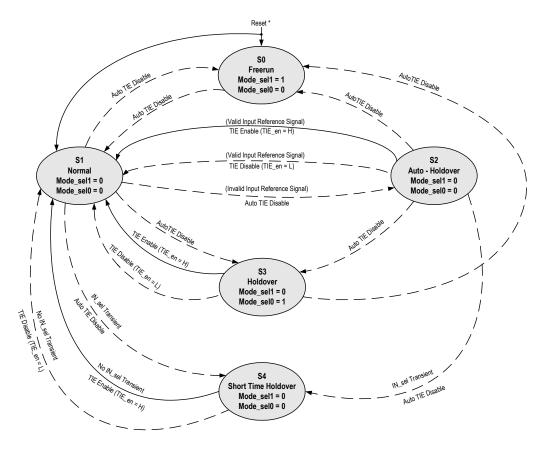

The State Control Circuit is an important part in the IDT82V3155. It is used to control the TIE block and the DPLL block as shown in Figure - 2. The control is based on the result of Invalid Input Signal Detection and the logic levels on the MODE\_sel0, MODE\_sel1, IN\_sel and TIE\_en pins.

The IDT82V3155 can be operated in three different modes: Normal, Holdover and Freerun. The operating mode is selected by the MODE\_sel1 and MODE\_sel0 pins, as shown in Table - 1.

Figure - 3 shows the state control diagram. All state changes occur synchronously on the rising edge of F8o. Three operating modes, Normal (S1), Holdover (S3) and Freerun (S0) can be switched from one to another by changing the logic levels on the MODE\_sel0 and MODE\_sel1 pins.

Figure - 2 State Control Circuit

#### Table - 1 Operating Modes Selection

| Mode S    | election Pins | Operating Mode |  |

|-----------|---------------|----------------|--|

| MODE_sel1 | MODE_sel0     | Operating mode |  |

| 0         | 0             | Normal         |  |

| 0         | 1             | Holdover       |  |

| 1         | 0             | Freerun        |  |

| 1         | 1             | Reserved       |  |

\* Note: After reset, the Mode\_sel1 and Mode\_sel0 should be initially set to '10' or '00'.

Figure - 3 State Control Diagram

The mode changes between Normal (S1) and Auto-Holdover (S2) are triggered by the Invalid Input Reference Detection Circuit and are irrelative to the logic levels on the MODE\_sel0 and MODE\_sel1 pins. At the stage of S1, if the input reference is invalid (out of the capture range), the operating mode will be changed to Auto-Holdover (S2) automatically. At the stage of S2, if no IN\_sel transient occurs and the input reference becomes valid, the operating mode will be changed back to Normal (S1) automatically. If an IN\_sel transient is detected at the stage of S2, the operating mode will be changed to Short Time Holdover (S4) with the TIE Control Block automatically disabled. Refer to "2.5 Invalid Input Signal Detection" for more information.

The mode changes between Normal (S1) and Short Time Holdover (S4) are triggered by the IN\_sel transient. At the stage of S1, if a voltage transient occurs on the IN\_sel pin, the operating mode will be changed to Short Time Holdover (S4) automatically. At the stage of S4, if no voltage transient occurs on the IN\_sel pin, the operating mode will be changed back to S1 automatically. See "2.3 Reference Input Switch" for details.

When the operating mode is changed from one to another, the TIE control block is automatically disabled as shown in Figure - 3, except the changes from Holdover (S3) or Auto-Holdover (S2) to Normal (S1). In the case of changing from S3 or S2 to S1, the TIE control block is enabled or disabled by the TIE\_en pin.

#### 2.1.1 NORMAL MODE

The Normal mode is typically used when a slave clock source synchronized to the network is required.

In this mode, the IDT82V3155 provides timing (C1.5o,  $\overline{C30}$ , C2o,  $\overline{C4o}$ , C8o,  $\overline{C16o}$ , C19o,  $\overline{C32o}$ , C155) and synchronization (F0o, F8o, F16o, F19o, F32o, TSP, RSP) signals. All these signals are synchronous to one of the two input references. The nominal frequency of the input reference can be 8 kHz, 1.544 MHz, 2.048 MHz or 19.44 MHz.

After reset, the IDT82V3155 will take 30 seconds at most to make the output signals synchronous (phase locked) to the input reference.

Whenever the IDT82V3155 works in the Normal mode, the NORMAL pin will be set to logic high.

#### 2.1.2 FAST LOCK MODE

The Fast Lock mode is a submode of the Normal mode. It allows the DPLL to lock to a reference more quickly than the Normal mode allows. Typically, the locking time in the Fast Lock mode is less than 500 ms.

When the FLOCK pin is set to high, the Fast Lock mode will be enabled.

#### 2.1.3 HOLDOVER MODE

The Holdover mode is typically used for short duration (e.g., 2 seconds) while network synchronization is temporarily disrupted.

In the Holdover mode, the IDT82V3155 provides timing and synchronization signals that are not locked to an external reference signal, but are based on storage techniques. In the Normal mode, when the output frequency is locked to the input reference signal, a numerical value corresponding to the output frequency is stored alternately in two memory locations every 30 ms. When the device is changed to the Holdover mode, the stored value from between 30 ms and 60 ms is used

to set the output frequency of the device.

The frequency accuracy in the Holdover mode is  $\pm 0.025$  ppm, which corresponds to a worst case of 18 frame (125 µs per frame) slips in 24 hours. This meets the AT&T TR62411 and Telcordia GR-1244-CORE Stratum 3 requirement of  $\pm 0.37$  ppm (255 frame slips per 24 hours).

Whenever the IDT82V3155 works in the Holdover mode, the HOLDOVER pin will be set to logic high.

#### 2.1.4 FREERUN MODE

The Freerun mode is typically used when a master clock source is required, or used when a system is just powered up and the network synchronization has not been achieved.

In this mode, the IDT82V3155 provides timing and synchronization signals which are based on the master clock frequency (OSCi) only, and are not synchronized to the input reference signal.

The accuracy of the output clock is equal to the accuracy of the master clock (OSCi). So if a  $\pm 32$  ppm output clock is required, the master clock must also be  $\pm 32$  ppm. Refer to "2.8 OSC" for more information.

Whenever the IDT82V3155 works in the Freerun mode, the FREERUN pin will be set to logic high.

### 2.2 FREQUENCY SELECT CIRCUIT

The input reference can be 8 kHz, 1.544 MHz, 2.048 MHz or 19.44 MHz. The F0\_sel1 and F0\_sel0 pins select one of the four frequencies for the reference input 0 (Fref0). The F1\_sel1 and F1\_sel0 pins select one of the four frequencies for the reference input 1 (Fref1). See Table - 2 and Table - 3 for details.

The reference inputs Fref0 and Fref1 may have different frequencies applied to them. Every time the frequency is changed, the device must be reset to make the change effective.

#### Table - 2 Fref0 Frequency Selection

| Frequenc | y Selection Pins | Fref0 Input Frequency |  |

|----------|------------------|-----------------------|--|

| F0_sel1  | F0_sel0          | There input Trequency |  |

| 0        | 0                | 19.44 MHz             |  |

| 0        | 1                | 8 kHz                 |  |

| 1        | 0                | 1.544 MHz             |  |

| 1 1      |                  | 2.048 MHz             |  |

#### Table - 3 Fref1 Frequency Selection

| Frequenc | y Selection Pins | Fref1 Input Frequency |  |

|----------|------------------|-----------------------|--|

| F1_sel1  | F1_sel0          | Fren input Frequency  |  |

| 0 0      |                  | 19.44 MHz             |  |

| 0        | 1                | 8 kHz                 |  |

| 1        | 0                | 1.544 MHz             |  |

| 1        | 1                | 2.048 MHz             |  |

### 2.3 REFERENCE INPUT SWITCH

The IDT82V3155 accepts two simultaneous reference signals Fref0 and Fref1, and operates on the falling edge (8 KHz, 1.544 MHz and 2.048 MHz) or rising edge (19.44 MHz). One of the two reference signals will be input to the device, as determined by the IN\_sel pin. See Table - 4. The selected reference signal is sent to the TIE control block, Reference Input Monitor and Invalid Input Signal Detection block for further processing.

#### Table - 4 Input Reference Selection

| IN_sel | Input Reference |

|--------|-----------------|

| 0      | Fref0           |

| 1      | Fref1           |

When a transient voltage occurs on the IN\_sel pin, the operating mode will be changed to Short Time Holdover (S4) with the TIE Control Block automatically disabled. At the stage of S4, if no IN\_sel transient occurs, the reference signal will be switched from one to the other, and the operating mode will be changed back to Normal (S1) automatically. During the change from S4 to S1, the TIE Control Block can be enabled or disabled, depending on the logic level on the TIE\_en pin. See Figure - 3 for details.

### 2.4 REFERENCE INPUT MONITOR

The Telcordia GR-1244-CORE standard recommends that the DPLL should be able to reject the references that are off the nominal frequency by more than  $\pm 12$  ppm. The IDT82V3155 monitors the Fref0 and Fref1 frequencies and outputs two signals at MON\_out0 pin and MON\_out1 pin to indicate the monitoring results respectively. Whenever the Fref0 frequency is off the nominal frequency by more than  $\pm 12$  ppm, the MON\_out0 pin will go high. The MON\_out1 pin indicates the monitoring

result of Fref1 in the same way. The MON\_out0 and MON\_out1 signals are updated every 2 seconds.

### 2.5 INVALID INPUT SIGNAL DETECTION

This circuit is used to detect if the selected input reference (Fref0 or Fref1) is out of the capture range. Refer to "3.6 Capture Range" for details. This includes a complete loss of the input reference and a large frequency shift in the input reference.

If the input reference is invalid (out of the capture range), the IDT82V3155 will be automatically changed to the Holdover mode (Auto-Holdover). When the input reference becomes valid, the device will be changed back to the Normal mode and the output signals will be locked to the input reference.

In the Holdover mode, the output signals are based on the output reference signal 30 ms to 60 ms prior to entering the Holdover mode. The amount of phase drift while in holdover can be negligible because the Holdover mode is very accurate (e.g., 0.025 ppm). Consequently, the phase delay between the input and output after switching back to the Normal mode is preserved.

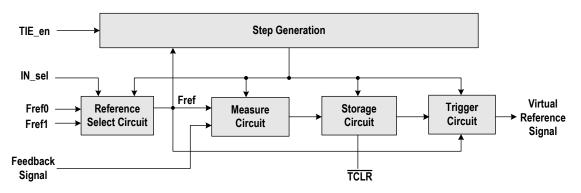

### 2.6 TIE CONTROL BLOCK

If the current reference is badly damaged or lost, it is necessary to use the other reference or the one generated by storage techniques instead. But when switching the reference, a step change in phase on the input reference will occur. A step change in phase in the input to DPLL may lead to an unacceptable phase change on the output signals. The TIE control block, when enabled, prevents a step change in phase on the input reference signals from causing a step change in phase on the output of the DPLL block. Figure - 4 shows the TIE Control Block diagram.

When the TIE Control Block is enabled manually or automatically (by the TIE\_en pin or TIE auto-enable logic generated by the State Control Circuit), it works under the control of the Step Generation circuit.

At the Measure Circuit stage, the selected reference signal (Fref0 or Fref1) is compared with the feedback signal (current output feed back from the Frequency Select Circuit). The phase difference between the input reference and the feedback signal is stored in the Storage Circuit for TIE correction. According to the value stored in the storage circuit,

the Trigger Circuit generates a virtual reference with the same phase as the previous reference. In this way, the reference can be switched without generating a step change in phase.

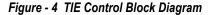

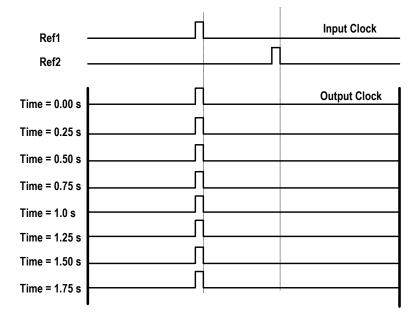

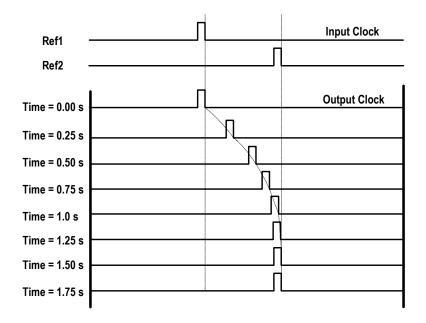

Figure - 5 shows the phase transient that will result if a reference switch is performed with the TIE Control Block enabled.

The value of the phase difference in the Storage Circuit can be cleared by applying a logic low reset signal to the  $\overline{\text{TCLR}}$  pin. The minimum width of the reset pulse should be 300 ns.

#### 82V3155

#### ENHANCED T1/E1/OC3 WAN PLL WITH DUAL REFERENCE INPUTS

When the IDT82V3155 primarily enters the Holdover mode for a short time period and then returns back to the Normal mode, the TIE Control Circuit should not be enabled. This will prevent undesired accumulated phase change between the input and output.

If the TIE Control Block is disabled manually or automatically, a reference switch will result in a phase alignment between the input signal and the output signal as shown in Figure - 6. The slope of the phase adjustment is limited to 5 ns per 125  $\mu$ s.

Figure - 5 Reference Switch with TIE Control Block Enabled

Figure - 6 Reference Switch with TIE Control Block Disabled

© 2019 Renesas Electronics Corporation

### 2.7 DPLL BLOCK

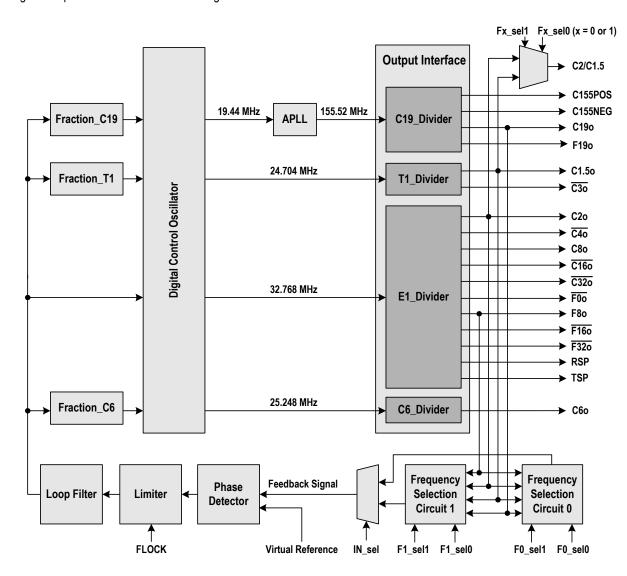

As shown in Figure - 7, the DPLL Block consists of a Phase Detector, a Limiter, a Loop Filter, a Digital Control Oscillator and Divider.

### 2.7.1 PHASE DETECTOR (PHD)

In the Normal mode, the Phase Detector compares the virtual reference signal from the TIE Control Circuit with the feedback signal from the Frequency Select Circuit, and outputs an error signal corresponding to the phase difference. This error signal is sent to the

Limiter circuit for phase slope control.

In the Freerun or Holdover mode, the Frequency Select Circuit, the Phase Detector and the Limiter are inactive, and the input reference signal is not used.

#### 2.7.2 LIMITER

The Limiter is used to limit the phase slope. It ensures that the maximum output phase slope is limited to 5 ns per 125  $\mu s$  for all input transient conditions. This well meets the AT&T TR62411 and Telcordia

Figure - 7 DPLL Block Diagram

In the Normal mode, the Limiter receives the error signal from the Phase Detector, limits the phase slope within 5 ns per 125  $\mu$ s and sends the limited signal to the Loop Filter.

In the Fast Lock mode, the Limiter is disabled, and the DPLL locks to the input reference within 500 ms, which is much shorter than that in the Normal mode.

#### 2.7.3 LOOP FILTER

The Loop Filter ensures that the jitter transfer meets the ETS 300 011 and AT&T TR62411 requirements. It works similarly to a first order low pass filter with 2.1 Hz cutoff frequency for the four valid input frequencies (8 kHz, 1.544 MHz, 2.048 MHz or 19.44 MHz).

The output of the Loop Filter goes to the Digital Control Oscillator directly or through the Fraction blocks, in which E1, T1, C6 and C19 signals are generated.

#### 2.7.4 FRACTION BLOCK

By applying some algorithms to the incoming E1 signal, the Fraction\_C19, Fraction\_C6 and Fraction\_T1 blocks generate C19, C6 and T1 signals respectively.

#### 2.7.5 DIGITAL CONTROL OSCILLATOR (DCO)

In the Normal mode, the DCO receives four limited and filtered signals from Loop Filter or Fraction blocks. Based on the values of the received signals, the DCO generates four digital outputs: 19.44 MHz, 25.248 MHz, 32.768 MHz and 24.704 MHz for C19, C6, E1 and T1 dividers respectively.

In the Holdover mode, the DCO is running at the same frequency as that generated by storage techniques.

In the Freerun mode, the DCO is running at the same frequency as that of the master clock.

#### 2.7.6 LOCK INDICATOR

If the output frequency of the DPLL is identical to the input frequency, and the input phase offset is small enough so that no slope limiting is exhibited, the LOCK pin will be set high.

#### 2.7.7 OUTPUT INTERFACE

The Output Interface uses three output signals from the DCO to generate totally 10 types of clock signals and 7 types of framing signals All these output signals are synchronous to F8o.

The 32.768 MHz signal is used by the E1\_divider to generate 5 types of clock signals (C2o, C4o, C8o, C16o and C32o) with nominal 50% duty cycle and 6 types of framing signals (F0o, F8o, F16o, F32o, RSP and TSP).

The 24.704 MHz signal is used by the T1\_divider to generate two types of T1 signals (C1.5o and  $\overline{C30}$ ) with nominal 50% duty cycle.

The 25.248 MHz signal is used by the C6\_divider to generate a C6o signal with nominal 50% duty cycle.

The 19.44 MHz signal is sent to an APLL, which outputs a 155.52 MHz signal. The 155.52 MHz signal is used by the C19\_divider to generate 19.44 MHz and 155.52 MHz clock signals (C19o, C155POS and C155NEG) with nominal 50% duty cycle and a framing signal F19o.

Additionally, the IDT82V3155 provides an output clock (C2/C1.5) with the frequency controlled by the frequency selection pins Fx\_sel0 and Fx\_sel1 (see Table - 5 for details). If the selected reference input (Fref0 or Fref1) is 8 kHz, 2.048 MHz or 19.44 MHz, the C2/C1.5 pin will output a 2.048 MHz clock signal. If the selected reference input (Fref0 or Fref1) is 1.544 MHz, the C2/C1.5 pin will output a 1.544 MHz clock signal. The electrical and timing characteristics of this output (2.048 MHz or 1.544 MHz) is the same as that of C2o or C1.50.

#### Table - 5 C2/C1.5 Output Frequency Control

| Frequency S | election Pins | Frefx Input | C2/C1.5 Output |

|-------------|---------------|-------------|----------------|

| Fx_sel1     | Fx_sel0       | Frequency   | Frequency      |

| 0           | 0             | 19.44 MHz   | 2.048 MHz      |

| 0           | 1             | 8 kHz       | 2.048 MHz      |

| 1           | 0             | 1.544 MHz   | 1.544 MHz      |

| 1           | 1             | 2.048 MHz   | 2.048 MHz      |

Note: 'x' can be 0 or 1, as selected by IN\_sel pin.

$IN_sel = 0$ : x = 0, Fref0 is the selected reference input. The frequency of Fref0 is determined by F0\_sel0 and F0\_sel1 pins.

$IN_sel = 1: x = 1$ , Fref1 is the selected reference input. The frequency of Fref1 is determined by F1\_sel0 and F1\_sel1 pins.

#### 82V3155

#### 2.8 OSC

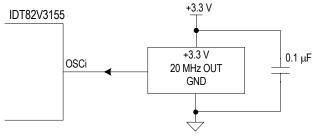

The IDT82V3155 can use a clock as the master timing source. In the Freerun mode, the frequency tolerance of the clock outputs is identical to that of the source at the OSCi pin. For applications not requiring an accurate Freerun mode, the tolerance of the master timing source may be  $\pm 100$  ppm. For applications requiring an accurate Freerun mode, such as AT&T TR62411, the tolerance of the master timing source must be no greater than  $\pm 32$  ppm.

The desired capture range should be taken into consideration when determining the accuracy of the master timing source. The sum of the accuracy of the master timing source and the capture range of the IDT82V3155 will always equal 230 ppm. For example, if the master timing source is 100 ppm, the capture range will be 130 ppm.

#### 2.8.1 CLOCK OSCILLATOR

When selecting a Clock Oscillator, numerous parameters must be considered. This includes absolute frequency, frequency change over temperature, output rise and fall times, output levels and duty cycle.

For applications requiring  $\pm 32$  ppm clock accuracy, the following clock oscillator module may be used.

FOX F7C-2E3-20.0 MHz

Frequency:

20.0 MHz

Tolerance:

25 ppm 0°C to 70°C

Rise & Fall Time:10 ns (0.33 V, 2.97 V, 15 pF)

Duty Cycle:

40% to 60%

For Stratum 3 application, the clock oscillator should meet the following requirements:

| Frequency: | 20.0 MHz                                     |

|------------|----------------------------------------------|

| Tolerance: | ±4.6 ppm over 20 years life time             |

| Drift:     | ±0.04 ppm per day @ constant temperature     |

|            | ±0.3 ppm over temperature range of 0 to 70°C |

The output clock should be connected directly (not AC coupled) to the OSCi input of the IDT82V3155, as shown in Figure - 8.

Figure - 8 Clock Oscillator Circuit

### 2.9 JTAG

The IDT82V3155 supports IEEE 1149.1 JTAG Scan.

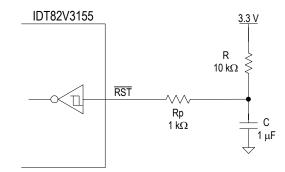

### 2.10 RESET CIRCUIT

A simple power-up reset circuit is shown as Figure - 9. The logic low reset pulse is about 50  $\mu$ s.

The resistor Rp is used for protection only and limits current into the  $\overline{\text{RST}}$  pin during power down conditions. The logic low reset pulse width is not critical but should be greater than 300 ns.

Figure - 9 Power-Up Reset Circuit

#### 82V3155

#### ENHANCED T1/E1/OC3 WAN PLL WITH DUAL REFERENCE INPUTS

### 2.11 POWER SUPPLY FILTERING TECHNIQUES

To achieve optimum jitter performance, power supply filtering is required to minimize supply noise modulation of the output clocks. The common sources of power supply noise are switching power supplies and the high switching noise from the outputs to the internal PLL. The 82V3155 provides separate power pins:  $V_{DDA}$  and  $V_{DDD}$ .  $V_{DDA}$  pins are for the internal analog PLL, and  $V_{DDD}$  pins are for the core logic as well as I/O driver circuits.

To minimize switching power supply noise generated by the switching regulator, the power supply output should be filtered with sufficient bulk capacity to minimize ripple and 0.1 uF (0402 case size, ceramic) capacitors to filter out the switching transients.

For the 82V3155, the decoupling for  $V_{DDA}$  and  $V_{DDD}$  are handled individually.  $V_{DDD}$  and  $V_{DDA}$  should be individually connected to the power supply plane through vias, and bypass capacitors should be used

for each pin. Figure - 10 illustrates how bypass capacitor and ferrite bead should be connected to each power pin.

The analog power supply V<sub>DDA</sub> should have low impedance. This can be achieved by using one 10 uF (1210 case size, ceramic) and at least two 0.1 uF (0402 case size, ceramic) capacitors in parallel. The 0.1 uF (0402 case size, ceramic) capacitors must be placed next to the V<sub>DDA</sub> pins and as close as possible. Note that the 10 uF capacitor must be of 1210 case size, and it must be ceramic for lowest possible ESR (Effective Series Resistance). The 0.1 uF should be of case size 0402, which offers the lowest ESL (Effective Series Inductance) to achieve low impedance towards the high speed range.

For V<sub>DDD</sub>, at least three 0.1 uF (0402 case size, ceramic) and one 10 uF (1210 case size, ceramic) capacitors are recommended. The 0.1 uF capacitors should be placed as close to the V<sub>DDD</sub> pins as possible.

Please refer to evaluation board schematic for details.

Figure - 10 IDT82V3155 Power Decoupling Scheme

# 3 MEASURES OF PERFOR-MANCE

The following are some synchronizer performance indicators and their corresponding definitions.

### 3.1 INTRINSIC JITTER

Intrinsic jitter is the jitter produced by the synchronizing circuit and is measured at its output. It is measured by applying a reference signal with no jitter to the input of the device, and measuring its output jitter. Intrinsic jitter may also be measured when the device is in a non-synchronizing mode, such as free running or holdover, by measuring the output jitter of the device. Intrinsic jitter is usually measured with various band limiting filters depending on the applicable standards. For the IDT82V3155, the intrinsic Jitter is limited to less than 0.02 UI on the 2.048 MHz and 1.544 MHz clocks.

### 3.2 JITTER TOLERANCE

Jitter tolerance is a measure of the ability of a DPLL to operate properly (i.e., remain in lock and or regain lock in the presence of large jitter magnitudes at various jitter frequencies) when jitter is applied to its reference. The applied jitter magnitude and jitter frequency depends on the applicable standards.

### 3.3 JITTER TRANSFER

Jitter transfer or jitter attenuation refers to the magnitude of jitter at the output of a device for a given amount of jitter at the input of the device. Input jitter is applied at various amplitudes and frequencies, and output jitter is measured with various filters depending on the applicable standards.

For the IDT82V3155, two internal elements determine the jitter attenuation. This includes the internal 2.1 Hz low pass loop filter and the phase slope limiter. The phase slope limiter limits the output phase slope to 5 ns per 125  $\mu$ s. Therefore, if the input signal exceeds this rate, such as for very large amplitude, low frequency input jitter, the maximum output phase slope will be limited (i.e., attenuated) to 5 ns per 125  $\mu$ s.

The IDT82V3155 has 17 outputs with 4 possible input frequencies for a total of 68 possible jitter transfer functions. Since all outputs are derived from the same signal, the jitter transfer values for the 4 cases, 8 kHz to 8 kHz, 1.544 MHz to 1.544 MHz, 2.048 MHz to 2.048 MHz and 19.44 MHz to 19.44 MHz can be applied to all outputs.

It should be noted that 1 UI at 1.544 MHz is 644 ns, which is not equal to 1 UI at 2.048 MHz, which is 488 ns. Consequently, a transfer value using different input and output frequencies must be calculated in common units (e.g., seconds).

Using the above method, the jitter attenuation can be calculated for all combinations of inputs and outputs based on the four jitter transfer functions provided. Note that the resulting jitter transfer functions for all combinations of inputs (8 kHz, 1.544 MHz, 2.048 MHz, 19.44 MHz) and outputs (8 kHz, 1.544 MHz, 3.088 MHz, 6.312 MHz, 2.048 MHz, 4.096 MHz, 8.192 MHz, 16.384 MHz, 19.44 MHz, 32.768 MHz, 155.52MHz) for a given input signal (jitter frequency and jitter amplitude) are the

same.

Since intrinsic jitter is always present, jitter attenuation will appear to be lower for small input jitter signals than for large ones. Consequently, accurate jitter transfer function measurements are usually made with large input jitter signals (e.g., 75% of the specified maximum jitter tolerance).

### 3.4 FREQUENCY ACCURACY

Frequency accuracy is defined as the absolute tolerance of an output clock signal when it is not locked to an external reference, but is operating in a free running mode. For the IDT82V3155, the Freerun accuracy is equal to the Master Clock (OSCi) accuracy.

### 3.5 HOLDOVER ACCURACY

Holdover accuracy is defined as the absolute tolerance of an output clock signal, when it is not locked to an external reference signal, but is operating using storage techniques. For the IDT82V3155, the storage value is determined while the device is in Normal mode and locked to an external reference signal.

The absolute Master Clock (OSCi) accuracy of the IDT82V3155 does not affect Holdover accuracy, but the change in OSCi accuracy while in Holdover mode does.

### 3.6 CAPTURE RANGE

Also referred to as pull-in range. This is the input frequency range over which the synchronizer must be able to pull into synchronization. The IDT82V3155 capture range is equal to  $\pm 230$  ppm minus the accuracy of the master clock (OSCi). For example, a 32 ppm master clock results in a capture range of 198 ppm.

The Telcordia GR-1244-CORE standard, recommends that the DPLL should be able to reject references that are off the nominal frequency by more than  $\pm 12$  ppm. The IDT82V3155 provides two pins, MON\_out0 and MON\_out1, to respectively indicate whether the reference inputs Fref0 and Fref1 are within  $\pm 12$  ppm of the nominal frequency.

### 3.7 LOCK RANGE

This is the input frequency range over which the synchronizer must be able to maintain synchronization. The lock range is equal to the capture range for the IDT82V3155.

### 3.8 PHASE SLOPE

Phase slope is measured in seconds per second and is the rate at which a given signal changes phase with respect to an ideal signal. The given signal is typically the output signal. The ideal signal is of constant frequency and is nominally equal to the value of the final output signal or final input signal.

### 3.9 TIME INTERVAL ERROR (TIE)

TIE is the time delay between a given timing signal and an ideal timing signal.

#### 82V3155

### 3.10 MAXIMUM TIME INTERVAL ERROR (MTIE)

MTIE is the maximum peak to peak delay between a given timing signal and an ideal timing signal within a particular observation period.

### 3.11 PHASE CONTINUITY

Phase continuity is the phase difference between a given timing signal and an ideal timing signal at the end of a particular observation period. Usually, the given timing signal and the ideal timing signal are of the same frequency. Phase continuity applies to the output of the synchronizer after a signal disturbance due to a mode change. The observation period is usually the time from the disturbance, to just after the synchronizer has settled to a steady state.

In the case of the IDT82V3155, the output signal phase continuity is maintained to within  $\pm 5$  ns at the instance (over one frame) of all mode changes. The total phase shift, depending on the type of mode change, may accumulate up to 200 ns over many frames. The rate of change of the 200 ns phase shift is limited to a maximum phase slope of approximately 5 ns per 125 µs. This meets the AT&T TR62411 maximum phase slope requirement of 7.6 ns per 125 µs and Telcordia GR-1244-CORE (81 ns per 1.326 ms).

### 3.12 PHASE LOCK TIME

This is the time it takes the synchronizer to phase lock to the input signal. Phase lock occurs when the input signal and output signal are not changing in phase with respect to each other (not including jitter).

Lock time is very difficult to determine because it is affected by many factors including:

- 1. Initial input to output phase difference

- 2. Initial input to output frequency difference

- 3. Synchronizer loop filter

- 4. Synchronizer limiter

Although a short lock time is desirable, it is not always possible to achieve due to other synchronizer requirements. For instance, better jitter transfer performance is achieved with a lower frequency loop filter which increases lock time. And better (smaller) phase slope performance (limiter) results in longer lock times. The IDT82V3155 loop filter and limiter are optimized to meet the AT&T TR62411 jitter transfer and phase slope requirements. Consequently, phase lock time, which is not a standard requirement, may be longer than in other applications. See "7.1 Performance" for details.

The IDT82V3155 provides a FLOCK pin to enable the Fast Lock mode. When this pin is set to high, the DPLL will lock to an input reference within approximately 500 ms.

# 4 ABSOLUTE MAXIMUM RATINGS

| Ratings                                   | Min. | Max. | Unit |

|-------------------------------------------|------|------|------|

| Power supply voltage                      | -0.5 | 5.0  | V    |

| Voltage on any pin with respect to ground | -0.5 | 5.5  | V    |

| Package power dissipation                 |      | 200  | mW   |

| Storage temperature                       | -55  | 125  | °C   |

Note: Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# 5 RECOMMENDED DC OPERATING CONDITIONS

| Parameter             | Min. | Max. | Unit |

|-----------------------|------|------|------|

| Operating temperature | -40  | +85  | °C   |

| Power supply voltage  | 3.0  | 3.6  | V    |

# 6 DC ELECTRICAL CHARACTERISTICS

### 6.1 SINGLE END INPUT/OUTPUT PORT