# **HDMI Intel® FPGA IP User Guide**

Updated for Intel® Quartus® Prime Design Suite: 21.3

IP Version: **19.6.1**

Version: 2021.11.12

ID: 683798

## **Contents**

| 1. HDMI Intel® FPGA IP Quick Reference                                               | 4  |

|--------------------------------------------------------------------------------------|----|

| 2. HDMI Overview                                                                     | 6  |

| 2.1. Release Information                                                             |    |

| 2.2. Device Family Support                                                           |    |

| 2.3. Feature Support                                                                 |    |

| 2.4. Resource Utilization                                                            |    |

| 3. HDMI Intel FPGA IP Getting Started                                                | 17 |

| 3.1. Installing and Licensing Intel FPGA IP Cores                                    |    |

| 3.1.1. Intel FPGA IP Evaluation Mode                                                 |    |

| 3.2. Specifying IP Parameters and Options                                            |    |

| 4. HDMI Hardware Design Examples                                                     | 21 |

| 4.1. HDMI Hardware Design Examples for Intel Arria 10, Intel Cyclone 10 GX, and Inte |    |

| Stratix 10 Devices                                                                   | 21 |

| 4.2. HDCP Over HDMI Design Example for Intel Arria 10 and Intel Stratix 10 Devices   |    |

| 4.3. HDMI Hardware Design Examples for Arria V and Stratix V Devices                 | 22 |

| 4.3.1. HDMI Hardware Design Components                                               |    |

| 4.3.2. HDMI Hardware Design Requirements                                             | 37 |

| 4.3.3. Design Walkthrough                                                            | 38 |

| 5. HDMI Source                                                                       | 42 |

| 5.1. Source Functional Description                                                   | 42 |

| 5.1.1. Source Scrambler, TMDS/TERC4 Encoder                                          |    |

| 5.1.2. Source Video Resampler                                                        |    |

| 5.1.3. Source Window of Opportunity Generator                                        |    |

| 5.1.4. Source Auxiliary Packet Encoder                                               |    |

| 5.1.5. Source Auxiliary Packet Generators                                            |    |

| 5.1.6. Source Auxiliary Data Path Multiplexers                                       |    |

| 5.1.7. Source Auxiliary Control Port                                                 |    |

| 5.1.8. Source Audio Encoder                                                          |    |

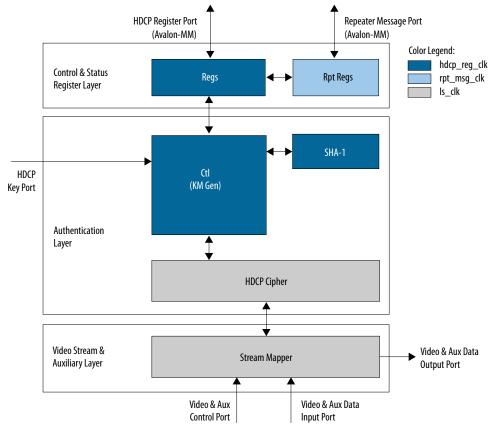

| 5.1.9. HDCP 1.4 TX Architecture                                                      |    |

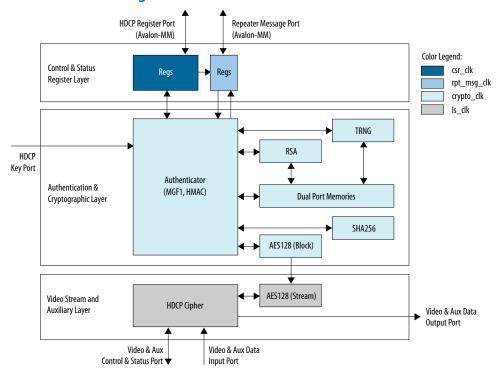

| 5.1.10. HDCP 2.3 TX Architecture                                                     | 63 |

| 5.1.11. FRL Packetizer                                                               |    |

| 5.1.12. FRL Character Block and Super Block Mapping                                  |    |

| 5.1.13. Reed-Solomon (RS) Forward Error Correction (FEC) Generation and              |    |

| Insertion                                                                            | 69 |

| 5.1.14. FRL Scrambler and Encoder                                                    | 69 |

| 5.1.15. Source FRL Resampler                                                         | 69 |

| 5.1.16. TX Oversampler                                                               | 70 |

| 5.1.17. Clock Enable Generator                                                       | 70 |

| 5.1.18. I <sup>2</sup> C Master                                                      | 71 |

| 5.2. Source Interfaces                                                               | 71 |

| 5.3. Source Clock Tree                                                               | 84 |

| 5.4. Link Training Procedure                                                         | 87 |

| 5.5. FRL Clocking Scheme                                                             |    |

| 5.6. Valid Video Data                                                                |    |

| 5.7. Source Deep Color Implementation When Support FRL = 0                           | 91 |

| 5.8. Source Deep Color Implementation When Support FRL = 1          | 93  |

|---------------------------------------------------------------------|-----|

| 5.9. Variable Refresh Rate (VRR) and Auto Low Latency Mode (ALLM)   |     |

| 6. HDMI Sink                                                        | 95  |

| 6.1. Sink Functional Description                                    |     |

| 6.1.1. Sink Word Alignment and Channel Deskew                       |     |

| 6.1.2. Sink Descrambler, TMDS/TERC4 Decoder                         | 99  |

| 6.1.3. Sink Auxiliary Decoder                                       |     |

| 6.1.4. Sink Auxiliary Packet Capture                                | 100 |

| 6.1.5. Sink Video Resampler                                         | 100 |

| 6.1.6. Sink Auxiliary Data Port                                     | 101 |

| 6.1.7. Sink Audio Decoder                                           |     |

| 6.1.8. Status and Control Data Channel (SCDC) Interface             | 108 |

| 6.1.9. HDCP 1.4 RX Architecture                                     |     |

| 6.1.10. HDCP 2.3 RX Architecture                                    | 114 |

| 6.1.11. FRL Depacketizer                                            |     |

| 6.1.12. Sink FRL Character Block and Super Block Demapper           |     |

| 6.1.13. Sink FRL Descrambler and Decoder                            |     |

| 6.1.14. Sink FRL Resampler                                          |     |

| 6.1.15. RX Oversampler                                              |     |

| 6.1.16. I2C Slave                                                   |     |

| 6.1.17. I2C and EDID RAM Blocks                                     |     |

| 6.1.18. Variable Refresh Rate(VRR) and Auto Low Latency Mode (ALLM  | ,   |

| 6.2. Sink Interfaces                                                |     |

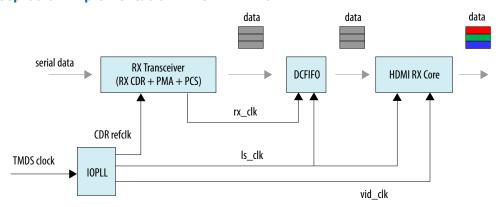

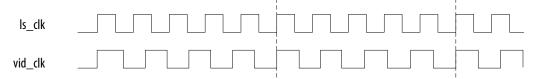

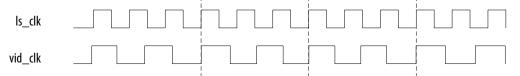

| 6.3. Sink Clock Tree                                                |     |

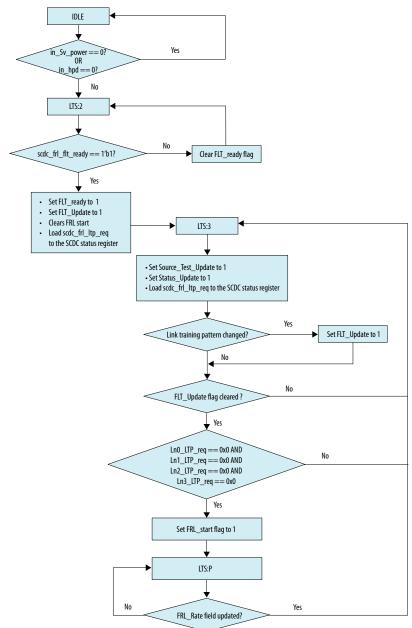

| 6.4. Link Training Procedure                                        |     |

| 6.5. Sink Deep Color Implementation When Support FRL = 0            |     |

| 6.6. Sink Deep Color Implementation When Support FRL = 1            | 138 |

| 7. HDMI Parameters                                                  | 140 |

| 7.1. HDMI Source Parameters                                         | 140 |

| 7.2. HDMI Sink Parameters                                           | 142 |

| 8. HDMI Simulation Example                                          | 146 |

| 8.1. Simulation Walkthrough                                         | 147 |

| 9. HDMI Intel FPGA IP User Guide Archives                           | 150 |

| 10. Document Revision History for the HDMI Intel FPGA IP User Guide | 151 |

|                                                                     |     |

## 1. HDMI Intel® FPGA IP Quick Reference

The Intel® FPGA High-Definition Multimedia Interface (HDMI) IP provides support for next-generation video display interface technology. The HDMI Intel FPGA IP is part of the Intel FPGA IP Library, which is distributed with the Intel Quartus® Prime software.

Note:

All information in this document refers to the Intel Quartus Prime Pro Edition software, unless stated otherwise.

| Inforr         | nation              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IP Information | Core Features       | <ul> <li>Conforms to the High-Definition Multimedia Interface (HDMI) Specification versions 1.4, 2.0b, and 2.1</li> <li>Supports transmitter and receiver on a single device transceiver quad</li> <li>Supports pixel frequency up to 600 MHz for HDMI 2.0 and 1,200 MHz for HDMI 2.1</li> <li>Supports fixed rate link (FRL) for HDMI 2.1</li> <li>Supports RGB and YCbCr 444, 422, and 420 color modes</li> <li>Accepts standard H-SYNC, V-SYNC, data enable, RGB video format, and YCbCr video format</li> <li>Supports up to 32 audio channels in 2-channel and 8-channel layouts.</li> <li>Supports 8, 10, 12, or 16 bits per component (bpc)</li> <li>Supports single link Digital Visual Interface (DVI)</li> <li>Supports High Dynamic Range (HDR) InfoFrame insertion and filter through the provided design examples</li> <li>Supports the High-bandwidth Digital Content Protection (HDCP) feature for Intel Arria® 10 and Intel Stratix® 10 devices</li> <li>Supports Variable Refresh Rate (VRR) and Auto Low Latency Mode (ALLM) for HDMI 2.1</li> </ul> |

|                | Typical Application | Interfaces within a PC and monitor     External display connections, including interfaces between a PC and monitor or projector, between a PC and TV, or between a device such as a DVD player and TV display                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | Device Family       | Supports Intel Stratix 10 (H-tile and L-tile), Intel Arria 10, Intel Cyclone® 10 GX, Arria V, and Stratix V FPGA devices  Note: HDMI 2.1 with FRL enabled supports only Intel Stratix 10 and Intel Arria 10 devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                | Design Tools        | Intel Quartus Prime software for IP design instantiation and compilation  Timing Analyzer in the Intel Quartus Prime software for timing analysis  ModelSim* - Intel FPGA Edition or ModelSim - Intel FPGA Starter Edition, NCSim, Riviera-PRO*, VCS*, VCS MX, and Xcelium* Parallel software for design simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

\*Other names and brands may be claimed as the property of others.

ISO 9001:2015 Registered

intel

Note:

The High-bandwidth Digital Content Protection (HDCP) feature is not included in the Intel Quartus Prime Pro Edition software. To access the HDCP feature, contact Intel at https://www.intel.com/content/www/us/en/broadcast/products/programmable/applications/connectivity-solutions.html.

### **Related Information**

- HDMI Intel Arria 10 FPGA IP Design Example User Guide

For more information about the Intel Arria 10 design examples.

- HDMI Intel Cyclone 10 GX FPGA IP Design Example User Guide

For more information about the Intel Cyclone 10 GX design examples.

- HDMI Intel Stratix 10 FPGA IP Design Example User Guide For more information about the Intel Stratix 10 design examples.

- Intel Arria 10 HDMI 2.1 System Design Guidelines

For more information about the Intel Arria 10 HDMI 2.1 system design guidelines.

- HDMI Intel FPGA IP User Guide Archives on page 150

Provides a list of user guides for previous versions of the HDMI Intel FPGA IP.

## 2. HDMI Overview

The HDMI Intel FPGA IP provides support for next generation video display interface technology.

The HDMI standard specifies a digital communications interface for use in both internal and external connections:

- Internal connections—interface within a PC and monitor

- External display connections—interface between a PC and monitor or projector, between a PC and TV, or between a device such a DVD player and TV display.

The HDMI system architecture consists of sinks and sources. A device may have one or more HDMI inputs and outputs.

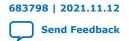

The HDMI cable and connectors carry four differential pairs that make up the Transition Minimized Differential Signaling (TMDS) data and clock channels for HDMI 1.4 and HDMI 2.0. For HDMI 2.1, HDMI cable and connectors carry four fixed rate link (FRL) lanes of data. You can use these channels to carry video, audio, and auxiliary data.

The HDMI also carries a Video Electronics Standards Association (VESA) Display Data Channel (DDC) and Status and Control Data Channel (SCDC). The DDC configures and exchanges status between a single source and a single sink. The source uses the DDC to read the sink's Enhanced Extended Display Identification Data (E-EDID) to discover the sink's configuration and capabilities.

The optional Consumer Electronics Control (CEC) protocol provides high-level control functions between various audio visual products in your environment.

The optional HDMI Ethernet and Audio Return Channel (HEAC) provides Ethernet compatible data networking between connected devices and an audio return channel in the opposite direction of TMDS. The HEAC also uses Hot-Plug Detect (HPD) line for link detection.

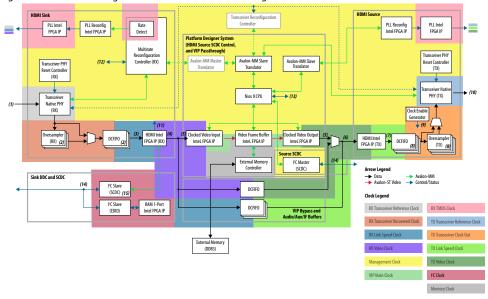

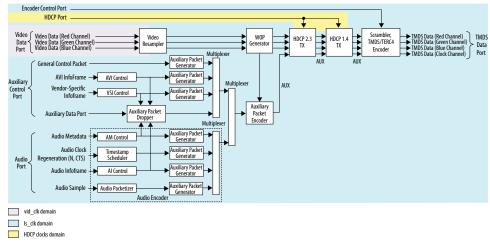

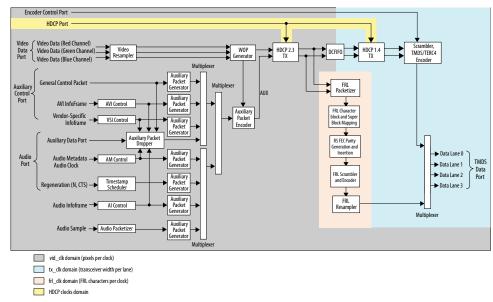

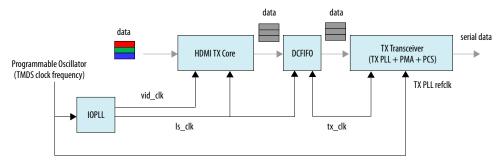

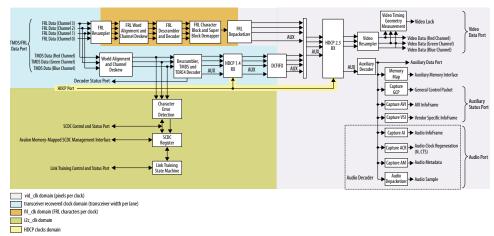

Figure 1. HDMI Intel FPGA IP Block Diagram for TMDS Mode

The figure below illustrates the blocks in the HDMI Intel FPGA IP for TMDS Mode.

Based on TMDS encoding, the HDMI protocol allows the transmission of both audio and video data between source and sink devices.

An HDMI interface consists of three color channels accompanied by a single clock channel. You can use each color line to transfer both individual RGB colors and auxiliary data.

Note: Refer to AN 837: Design Guidelines for Intel FPGA HDMI to know more about the channel mapping to the RGB colors for HDMI 1.4 and HDMI 2.0.

The receiver uses the TMDS clock as a frequency reference for data recovery on the three TMDS data channels. This clock typically runs at the video pixel rate.

TMDS encoding is based on an 8-bit to 10-bit algorithm. This protocol attempts to minimize data channel transition, and yet maintain sufficient transition so that a sink device can lock reliably to the data stream.

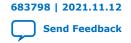

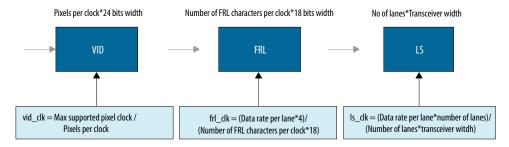

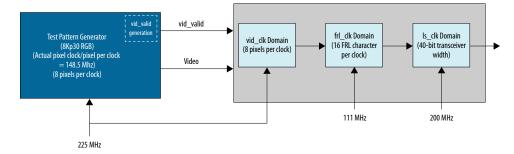

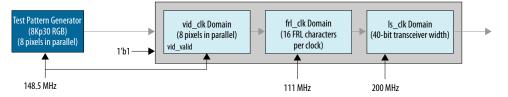

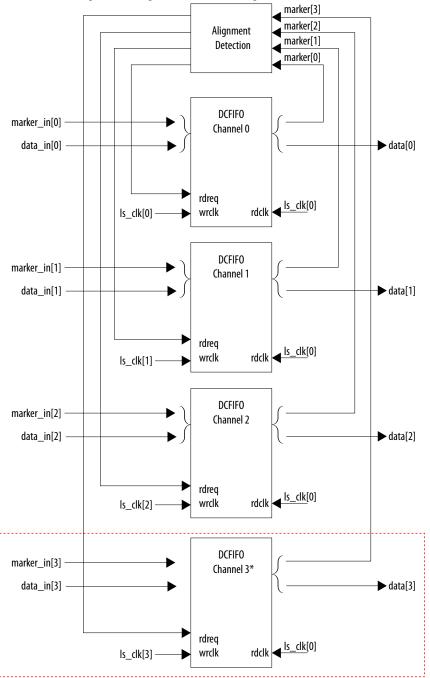

Figure 2. Fixed Rate Link (FRL)

In HDMI 1.4 and HDMI 2.0, 3 lanes carry data and 1 lane carries TMDS clock. When operating in FRL mode, the clock channel carries data as well. As the HDMI 2.1 specification requires backward compatibility with HDMI 1.4 and HDMI 2.0, you need to configure the 4th lane to carry data or clock during run time.

You can configure the FRL mode to 3 lanes and 4 lanes. In 3-lane FRL mode, each lane can operate at 3 Gbps or 6 Gbps. In 4-lane FRL mode, each lane can operate at 6 Gbps, 8 Gbps, 10 Gbps, or 12 Gbps.

Use category 3 (Cat 3) cable for FRL mode to ensure good signal integrity.

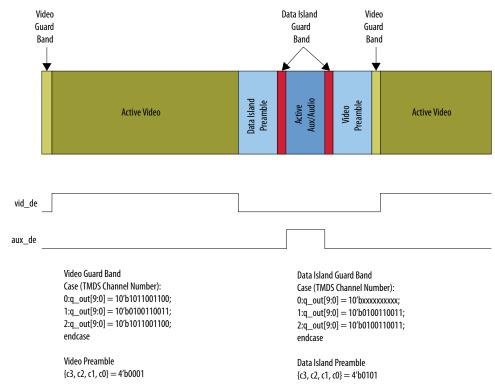

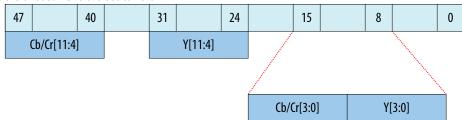

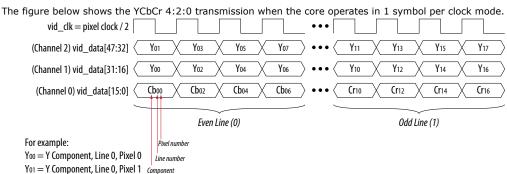

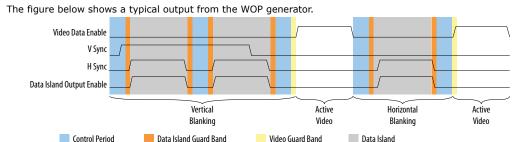

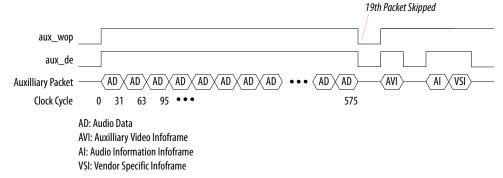

Figure 3. HDMI Intel FPGA IP Video Stream Data

The figure above illustrates two data streams:

- Data stream in green—transports color data

- Data stream in dark blue—transports auxiliary data

## Table 1. Video Data and Auxiliary Data

The table below describes the function of the video data and auxiliary data.

| Data           | Description                                                                                                                                                                                                                                                                         |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Video data     | <ul> <li>Packed representation of the video pixels clocked at the source pixel clock.</li> <li>Encoded using the TMDS 8-bit to 10-bit algorithm.</li> </ul>                                                                                                                         |

| Auxiliary data | <ul> <li>Transfers audio data together with a range of auxiliary data packets.</li> <li>Sink devices use auxiliary data packets to correctly reconstruct video and audio data.</li> <li>Encoded using the TMDS Error Reduction Coding-4 bits (TERC4) encoding algorithm.</li> </ul> |

Each data stream section is preceded with guard bands and pre-ambles. The guard bands and pre-ambles allow for accurate synchronization with received data streams.

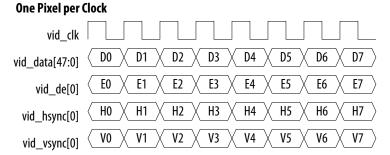

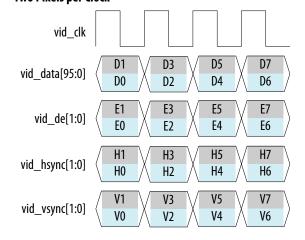

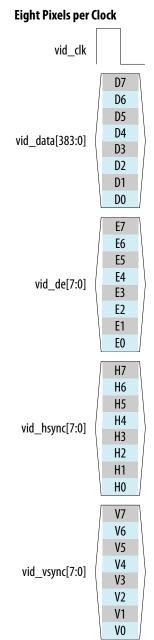

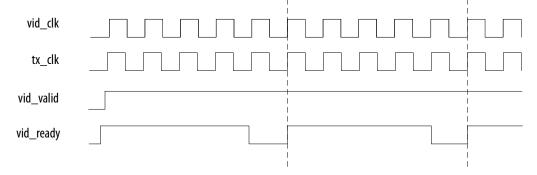

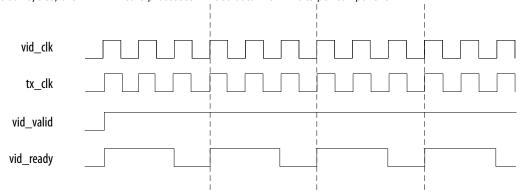

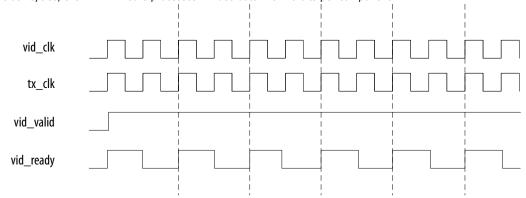

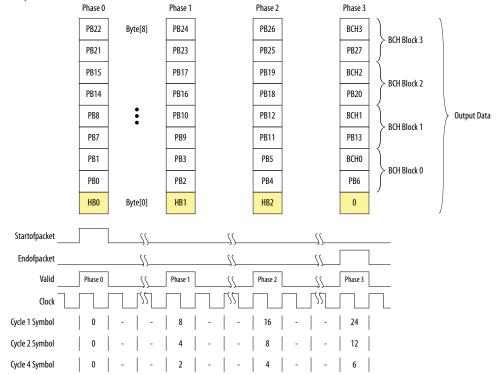

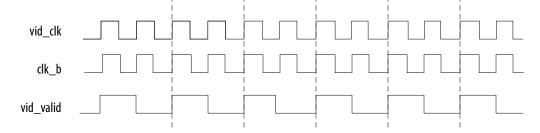

The following figures show the arrangement of the video data, video data enable, video H-SYNC, and video V-SYNC in 1, 2, 4, and 8 pixels per clock.

Figure 4. Video Data, Video Data Valid, H-SYNC, and V-SYNC—1 Pixel per Clock

Figure 5. Video Data, Video Data Valid, H-SYNC, and V-SYNC—2 Pixels per Clock

Two Pixels per Clock

Figure 6. Video Data, Video Data Valid, H-SYNC, and V-SYNC—4 Pixels per Clock

#### **Four Pixels per Clock** vid\_clk D3 D7 D2 D6 vid\_data[191:0] D1 D5 D0 D4 E3 **E**7 E2 **E6** vid\_de[3:0] E1 **E**5 E0 **E**4 Н3 H7 H2 Н6 vid\_hsync[3:0] H1 H5 H0 H4 ٧3 ۷7 ٧2 ۷6 vid\_vsync[3:0] ۷1 ۷5 V0 ٧4

Figure 7. Video Data, Video Data Valid, H-SYNC, and V-SYNC—8 Pixels per Clock

## **Related Information**

AN 837: Design Guidelines for Intel FPGA HDMI

## 2.1. Release Information

Intel FPGA IP versions match the Intel Quartus Prime Design Suite software versions until v19.1. Starting in Intel Quartus Prime Design Suite software version 19.2, Intel FPGA IP has a new versioning scheme.

The Intel FPGA IP version (X.Y.Z) number can change with each Intel Quartus Prime software version. A change in:

- X indicates a major revision of the IP. If you update the Intel Quartus Prime software, you must regenerate the IP.

- Y indicates the IP includes new features. Regenerate your IP to include these new features.

- Z indicates the IP includes minor changes. Regenerate your IP to include these changes.

## Table 2. HDMI Intel FPGA IP Release Information

| Item                        | Description                            |

|-----------------------------|----------------------------------------|

| IP Version                  | 19.6.1                                 |

| Intel Quartus Prime Version | 21.3 (Intel Quartus Prime Pro Edition) |

| Release Date                | 2021.10.04                             |

| Ordering Code               | IP-HDMI                                |

### **Related Information**

HDMI Intel FPGA IP Release Notes

Describes changes to the IP in a particular release.

## 2.2. Device Family Support

**Table 3.** Intel Device Family Support

| Device Family                                                          | Support Level |

|------------------------------------------------------------------------|---------------|

| Intel Stratix 10 (H-tile and L-tile) (Intel Quartus Prime Pro Edition) | Final         |

| Intel Arria 10 (Intel Quartus Prime Pro Edition)                       | Final         |

| Intel Cyclone 10 GX (Intel Quartus Prime Pro Edition)                  | Final         |

| Arria V (Intel Quartus Prime Standard Edition)                         | Final         |

| Stratix V (Intel Quartus Prime Standard Edition)                       | Final         |

The following terms define device support levels for Intel FPGA IP cores:

- Advance support—the IP core is available for simulation and compilation for this

device family. Timing models include initial engineering estimates of delays based

on early post-layout information. The timing models are subject to change as

silicon testing improves the correlation between the actual silicon and the timing

models. You can use this IP core for system architecture and resource utilization

studies, simulation, pinout, system latency assessments, basic timing assessments

(pipeline budgeting), and I/O transfer strategy (data-path width, burst depth, I/O

standards tradeoffs).

- Preliminary support—the IP core is verified with preliminary timing models for this

device family. The IP core meets all functional requirements, but might still be

undergoing timing analysis for the device family. It can be used in production

designs with caution.

- Final support—the IP core is verified with final timing models for this device family. The IP core meets all functional and timing requirements for the device family and can be used in production designs.

## 2.3. Feature Support

Table 4. HDMI Intel FPGA IP FRL Feature Support in Intel Stratix 10 and Intel Arria 10 Devices

| Feature         | Support Level    |             |  |

|-----------------|------------------|-------------|--|

| Support FRL = 1 | Intel Arria 10   | Final       |  |

|                 | Intel Stratix 10 | Preliminary |  |

| Support FRL = 0 | Final            |             |  |

The following terms define IP feature support levels for HDMI Intel FPGA IP:

- Preliminary support—The IP meets the functional requirement for the feature set as listed in this user guide. Additional features, characterization, and system level design guidelines shall be covered in future releases. The IP can be used in production designs for the supported device family with caution.

- Final support—The IP is compliant to the protocol CTS requirement for the supported device family and can be used in production design. Characterization report and system level design guidelines are available to facilitate meeting PHY CTS requirements.

## 2.4. Resource Utilization

The resource utilization data indicates typical expected performance for the HDMI Intel FPGA IP in the Intel Quartus Prime Pro Edition software.

### Table 5. HDMI Data Rate

The table lists the maximum data rates for HDMI Intel FPGA IP configurations.

|                     | Maximum Data Rate (Mbps)                |                                         |  |  |  |

|---------------------|-----------------------------------------|-----------------------------------------|--|--|--|

| Devices             | 2 Pixels per Clock<br>(Support FRL = 0) | 8 Pixels per Clock<br>(Support FRL = 1) |  |  |  |

| Intel Stratix 10    | 5,940<br>(Example: 4Kp60 8 bpc)         | 12,000<br>(Example: 8Kp30 12 bpc)       |  |  |  |

| Intel Arria 10      | 5,940<br>(Example: 4Kp60 8 bpc)         | 12,000<br>(Example: 8Kp30 12 bpc)       |  |  |  |

| Intel Cyclone 10 GX | 5,940<br>(Example: 4Kp60 8 bpc)         | Not Supported                           |  |  |  |

## Table 6. HDMI Intel FPGA IP Resource Utilization

The table lists the performance data for the different Intel FPGA devices.

| Device                     | Pixels per | Direction | ALMs   | Logic Registers |           | Memory  |                 |  |

|----------------------------|------------|-----------|--------|-----------------|-----------|---------|-----------------|--|

|                            | Clock      |           |        | Primary         | Secondary | Bits    | M10K or<br>M20K |  |

| Intel Stratix 10 H-        | 2          | RX        | 5.041  | 6,633           | 902       | 38,400  | 14              |  |

| tile (Support FRL = 0) (1) | 2          | TX        | 4,975  | 7,559           | 1,368     | 37,568  | 13              |  |

| Intel Stratix 10 L-        | 2          | RX        | 5,025  | 6,584           | 967       | 38,400  | 14              |  |

| tile<br>(Support FRL = 0)  | 2          | TX        | 4,966  | 7,539           | 1,425     | 37,568  | 13              |  |

| Intel Arria 10             | 2          | RX        | 3,768  | 5,716           | 1,049     | 36,352  | 14              |  |

| (Support FRL = 0)          | 2          | TX        | 4,445  | 7,016           | 1,701     | 36,968  | 13              |  |

| Intel Arria 10             | 8          | RX        | 48,865 | 55,417          | 13,067    | 376,832 | 87              |  |

| (Support FRL = 1)          | 8          | TX        | 30,092 | 35,533          | 6,839     | 276,288 | 60              |  |

| Intel Cyclene 10 CV        | 2          | RX        | 4,000  | 5,768           | 965       | 38,400  | 14              |  |

| Intel Cyclone 10 GX        | 2          | TX        | 4,484  | 7,167           | 1,629     | 36,968  | 13              |  |

Table 7. Recommended Speed Grades for Intel Stratix 10 and Intel Arria 10 Devices (Support FRL = 1)

| Device           | Lane Rate (Mbps) | Transceiver Interface<br>Width (bits) | Speed Grade           |

|------------------|------------------|---------------------------------------|-----------------------|

| Intel Stratix 10 | 12,000           | 40                                    | -1, -2 <sup>(3)</sup> |

| Intel Arria 10   | 12,000           | 40                                    | -1, -2                |

<sup>(3)</sup> Contact Intel Sales if you need to use -2 speed grade.

<sup>(1)</sup> Resource data for Support FRL = 1 design is not finalized.

<sup>(2)</sup> Contact Intel Sales for further optimization for specific device variants.

Table 8. Recommended Speed Grades for Intel Stratix 10, Intel Arria 10, and Intel Cyclone 10 GX Devices (Support FRL = 0)

| Device              | Lane Rate (Mbps) | Interface Width (bits) | Speed Grades |

|---------------------|------------------|------------------------|--------------|

| Intel Stratix 10    | 6,000            | 20                     | -1, -2       |

| Intel Arria 10      | 6,000            | 20                     | -1, -2       |

| Intel Cyclone 10 GX | 6,000            | 20                     | -5           |

## **Table 9. HDCP Resource Utilization**

The table lists the HDCP resource data for Intel Arria 10 and Intel Stratix 10 devices.

| Device        | HDCP IP  | Support<br>HDCP<br>Key<br>Managem<br>ent | Support<br>FRL | Pixels/<br>TMDS<br>Symbols<br>Per Clock | ALMs   | Combination al ALUTs | Registers | M20K   | DSP |   |

|---------------|----------|------------------------------------------|----------------|-----------------------------------------|--------|----------------------|-----------|--------|-----|---|

| Intel         | HDCP 2.3 | 0                                        | 0              | 2                                       | 6,479  | 10,548               | 12,015    | 10     | 3   |   |

| Arria 10      | TX       |                                          | 1              | 8                                       | 16,629 | 28,783               | 23,606    | 10     | 3   |   |

|               |          | 1                                        | 0              | 2                                       | 6,875  | 11,338               | 12,793    | 12     | 3   |   |

|               |          |                                          | 1              | 8                                       | 17,048 | 29,534               | 24,367    | 12     | 3   |   |

|               | HDCP 2.3 | 0                                        | 0              | 2                                       | 7,119  | 11,685               | 12,673    | 11     | 3   |   |

|               | RX       |                                          | 1              | 8                                       | 17,083 | 30,148               | 24,068    | 11     | 3   |   |

|               |          | 1                                        | 0              | 2                                       | 7,543  | 12,420               | 13,406    | 13     | 3   |   |

|               |          |                                          | 1              | 8                                       | 17,552 | 30,861               | 24,806    | 13     | 3   |   |

|               | HDCP 1.4 | 0                                        | 0, 1           | 2                                       | 1,665  | 2,626                | 4,411     | 2      | 0   |   |

|               | TX       | 1                                        | 0, 1           | 2                                       | 2,142  | 3,411                | 5,167     | 4      | 0   |   |

|               | HDCP 1.4 | 0                                        | 0, 1           | 2                                       | 1,170  | 1,850                | 3,407     | 3      | 0   |   |

|               | RX       | 1                                        | 0, 1           | 2                                       | 1,616  | 2,558                | 4,207     | 5      | 0   |   |

| Intel         |          | 0                                        | 0              | 2                                       | 7,213  | 11,582               | 12,810    | 10     | 3   |   |

| Stratix<br>10 |          |                                          | 1              | 8                                       | 17,755 | 29,784               | 24,428    | 10     | 3   |   |

|               |          | 1                                        | 0              | 2                                       | 7,888  | 12,473               | 13,188    | 12     | 3   |   |

|               |          |                                          | 1              | 8                                       | 18,477 | 30,540               | 25,191    | 12     | 3   |   |

|               | HDCP 2.3 | 0                                        | 0              | 2                                       | 8,145  | 12,691               | 13,438    | 11     | 3   |   |

|               | RX       |                                          | 1              | 8                                       | 18,482 | 30,881               | 25,422    | 11     | 3   |   |

|               |          |                                          | 1              | 0                                       | 2      | 8,644                | 13,382    | 13,640 | 13  | 3 |

|               |          |                                          | 1              | 8                                       | 19,096 | 31,460               | 26,138    | 13     | 3   |   |

|               | HDCP 1.4 | 0                                        | 0, 1           | 2                                       | 2,320  | 2,937                | 4,544     | 2      | 0   |   |

|               | TX       | 1                                        | 0, 1           | 2                                       | 2,881  | 3,797                | 5,170     | 4      | 0   |   |

|               | HDCP 1.4 | 0                                        | 0, 1           | 2                                       | 1,784  | 2,135                | 3,605     | 3      | 0   |   |

|               | RX       | 1                                        | 0, 1           | 2                                       | 2,293  | 2,897                | 4,219     | 5      | 0   |   |

## 3. HDMI Intel FPGA IP Getting Started

This chapter provides a general overview of the Intel IP core design flow to help you quickly get started with the HDMI Intel FPGA IP. The Intel FPGA IP Library is installed as part of the Intel Quartus Prime installation process. You can select and parameterize any Intel FPGA IP from the library. Intel provides an integrated parameter editor that allows you to customize the HDMI Intel FPGA IP to support a wide variety of applications. The parameter editor guides you through the setting of parameter values and selection of optional ports.

### **Related Information**

- Introduction to Intel FPGA IP Cores

- Provides general information about all Intel FPGA IP cores, including parameterizing, generating, upgrading, and simulating IP cores.

- Creating Version-Independent IP and Platform Designer Simulation Scripts Create simulation scripts that do not require manual updates for software or IP version upgrades.

- **Project Management Best Practices** Guidelines for efficient management and portability of your project and IP files.

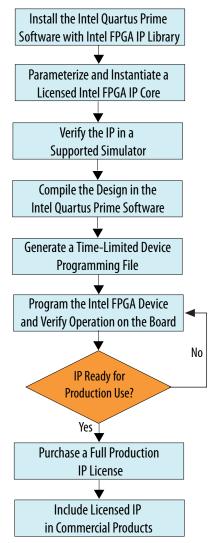

## 3.1. Installing and Licensing Intel FPGA IP Cores

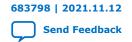

The Intel Quartus Prime software installation includes the Intel FPGA IP library. This library provides many useful IP cores for your production use without the need for an additional license. Some Intel FPGA IP cores require purchase of a separate license for production use. The Intel FPGA IP Evaluation Mode allows you to evaluate these licensed Intel FPGA IP cores in simulation and hardware, before deciding to purchase a full production IP core license. You only need to purchase a full production license for licensed Intel IP cores after you complete hardware testing and are ready to use the IP in production.

The Intel Quartus Prime software installs IP cores in the following locations by default:

#### Figure 8. **IP Core Installation Path**

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

9001:2015 Registered

**Table 10. IP Core Installation Locations**

| Location                                                               | Software                                | Platform |

|------------------------------------------------------------------------|-----------------------------------------|----------|

| <pre><drive>:\intelFPGA_pro\quartus\ip\altera</drive></pre>            | Intel Quartus Prime Pro Edition         | Windows* |

| <pre><drive>:\intelFPGA\quartus\ip\altera</drive></pre>                | Intel Quartus Prime Standard<br>Edition | Windows  |

| <pre><home directory="">:/intelFPGA_pro/quartus/ip/altera</home></pre> | Intel Quartus Prime Pro Edition         | Linux*   |

| <pre><home directory="">:/intelFPGA/quartus/ip/altera</home></pre>     | Intel Quartus Prime Standard<br>Edition | Linux    |

Note: The Intel Quartus Prime software does not support spaces in the installation path.

### 3.1.1. Intel FPGA IP Evaluation Mode

The free Intel FPGA IP Evaluation Mode allows you to evaluate licensed Intel FPGA IP cores in simulation and hardware before purchase. Intel FPGA IP Evaluation Mode supports the following evaluations without additional license:

- Simulate the behavior of a licensed Intel FPGA IP core in your system.

- Verify the functionality, size, and speed of the IP core quickly and easily.

- Generate time-limited device programming files for designs that include IP cores.

- Program a device with your IP core and verify your design in hardware.

Intel FPGA IP Evaluation Mode supports the following operation modes:

- **Tethered**—Allows running the design containing the licensed Intel FPGA IP indefinitely with a connection between your board and the host computer. Tethered mode requires a serial joint test action group (JTAG) cable connected between the JTAG port on your board and the host computer, which is running the Intel Quartus Prime Programmer for the duration of the hardware evaluation period. The Programmer only requires a minimum installation of the Intel Quartus Prime software, and requires no Intel Quartus Prime license. The host computer controls the evaluation time by sending a periodic signal to the device via the JTAG port. If all licensed IP cores in the design support tethered mode, the evaluation time runs until any IP core evaluation expires. If all of the IP cores support unlimited evaluation time, the device does not time-out.

- **Untethered**—Allows running the design containing the licensed IP for a limited time. The IP core reverts to untethered mode if the device disconnects from the host computer running the Intel Quartus Prime software. The IP core also reverts to untethered mode if any other licensed IP core in the design does not support tethered mode.

When the evaluation time expires for any licensed Intel FPGA IP in the design, the design stops functioning. All IP cores that use the Intel FPGA IP Evaluation Mode time out simultaneously when any IP core in the design times out. When the evaluation time expires, you must reprogram the FPGA device before continuing hardware verification. To extend use of the IP core for production, purchase a full production license for the IP core.

You must purchase the license and generate a full production license key before you can generate an unrestricted device programming file. During Intel FPGA IP Evaluation Mode, the Compiler only generates a time-limited device programming file (ct name>\_time\_limited.sof) that expires at the time limit.

Figure 9. Intel FPGA IP Evaluation Mode Flow

Note: Refer to each IP core's user guide for parameterization steps and implementation details.

Intel licenses IP cores on a per-seat, perpetual basis. The license fee includes first-year maintenance and support. You must renew the maintenance contract to receive updates, bug fixes, and technical support beyond the first year. You must purchase a full production license for Intel FPGA IP cores that require a production license, before generating programming files that you may use for an unlimited time. During Intel FPGA IP Evaluation Mode, the Compiler only generates a time-limited device programming file (project name>\_time\_limited.sof) that expires at the time limit. To obtain your production license keys, visit the Self-Service Licensing Center.

The Intel FPGA Software License Agreements govern the installation and use of licensed IP cores, the Intel Quartus Prime design software, and all unlicensed IP cores.

### **Related Information**

- Intel FPGA Licensing Support Center

- Introduction to Intel FPGA Software Installation and Licensing

## 3.2. Specifying IP Parameters and Options

Follow these steps to specify the HDMI Intel FPGA IP parameters and options.

- 1. Create a Intel Quartus Prime project using the **New Project Wizard** available from the File menu.

- 2. On the **Tools** menu, click **IP Catalog**.

- Under Installed IP, double-click Library ➤ Interface ➤ Protocols ➤ Audio&Video ➤ HDMI Intel FPGA IP.

The parameter editor appears.

- 4. Specify a top-level name for your custom IP variation. This name identifies the IP variation files in your project. If prompted, also specify the targeted FPGA device family and output file HDL preference. Click **OK**.

- 5. Specify parameters and options in the HDMI parameter editor:

- Optionally select preset parameter values. Presets specify all initial parameter values for specific applications (where provided).

- Specify parameters defining the IP functionality, port configurations, and device-specific features.

- Specify options for generation of a timing netlist, simulation model, testbench, or example design (where applicable).

- Specify options for processing the IP files in other EDA tools.

- Click **Generate** to generate the IP and supporting files, including simulation models.

- 7. Click **Close** when file generation completes.

- 8. Click Finish.

- 9. If you generate the HDMI Intel FPGA IP instance in a Intel Quartus Prime project, you are prompted to add Intel Quartus Prime IP File (.qip) and Intel Quartus Prime Simulation IP File (.sip) to the current Intel Quartus Prime project.

## 4. HDMI Hardware Design Examples

Intel offers design examples that you can simulate, compile, and test in hardware.

The implementation of the HDMI Intel FPGA IP on hardware requires additional components specific to the targeted device.

# 4.1. HDMI Hardware Design Examples for Intel Arria 10, Intel Cyclone 10 GX, and Intel Stratix 10 Devices

The HDMI Intel FPGA IP offers design examples that you can generate through the IP catalog in the Intel Quartus Prime Pro Edition software.

### **Related Information**

- HDMI Intel Arria 10 FPGA IP Design Example User Guide

For more information about the Intel Arria 10 design examples.

- HDMI Intel Cyclone 10 GX FPGA IP Design Example User Guide

For more information about the Intel Cyclone 10 GX design examples.

- HDMI Intel Stratix 10 FPGA IP Design Example User Guide

For more information about the Intel Stratix 10 design examples.

- Intel Arria 10 HDMI 2.1 System Design Guidelines

For more information about the Intel Arria 10 HDMI 2.1 system design quidelines.

# 4.2. HDCP Over HDMI Design Example for Intel Arria 10 and Intel Stratix 10 Devices

The High-bandwidth Digital Content Protection (HDCP) over HDMI hardware design example helps you to evaluate the functionality of the HDCP feature and enables you to use the feature in your Intel Arria 10 and Intel Stratix 10 designs.

For detailed information about the HDCP over HDMI design examples, refer to the Intel Arria 10 and Intel Stratix 10 design example user guides.

Note:

The HDCP feature is not included in the Intel Quartus Prime Pro Edition software. To access the HDCP feature, contact Intel at https://www.intel.com/content/www/us/en/broadcast/products/programmable/applications/connectivity-solutions.html.

#### **Related Information**

HDMI Intel Arria 10 FPGA IP Design Example User Guide

For more information about the HDCP over HDMI design example for Intel Arria 10 devices and the security considerations when using the HDCP features.

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2015 Registered

HDMI Intel Stratix 10 FPGA IP Design Example User Guide

For more information about the HDCP over HDMI design example for Intel Stratix 10 devices and the security considerations when using the HDCP features.

# 4.3. HDMI Hardware Design Examples for Arria V and Stratix V Devices

The HDMI hardware design example helps you evaluate the functionality of the HDMI Intel FPGA IP and provides a starting point for you to create your own design for Arria V and Stratix V devices in the Intel Quartus Prime Standard Edition software.

The design example runs on the following device kits:

- Arria V GX starter kit

- Stratix V GX development kit

- Bitec HDMI HSMC 2.0 Daughter Card Revision 8

### **Related Information**

AN 837: Design Guidelines for Intel FPGA HDMI

## 4.3.1. HDMI Hardware Design Components

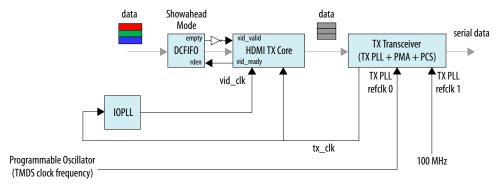

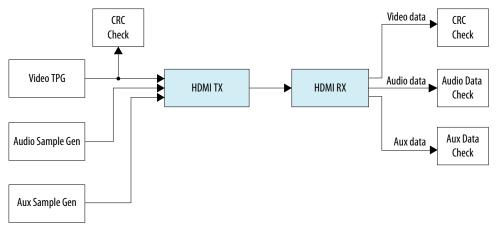

The demonstration designs instantiate the Video and Image Processing (VIP) Suite IP cores or FIFO buffers to perform a direct HDMI video stream passthrough between the HDMI sink and source.

The hardware demonstration design comprises the following components:

- HDMI sink

- Transceiver Native PHY (RX)

- Transceiver PHY Reset Controller (RX)

- PLL

- PLL Reconfiguration

- Multirate Reconfiguration Controller (RX)

- Oversampler (RX)

- DCFIFO

- Sink Display Data Channel (DDC) and Status and Control Data Channel (SCDC)

- Transceiver Reconfiguration Controller

- VIP bypass and Audio, Auxiliary and InfoFrame buffers

- Platform Designer system

- VIP passthrough for HDMI video stream

- Source SCDC controller

- HDMI source reconfiguration controller

- HDMI source

- Transceiver Native PHY (TX)

- Transceiver fPLL

- Transceiver PHY Reset Controller (TX)

- PLL

- PLL Reconfiguration

- Oversampler (TX)

- DCFIFO

- Clock Enable Generator

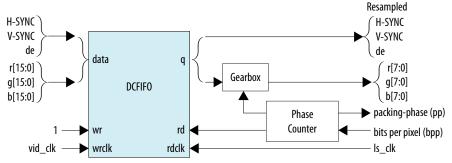

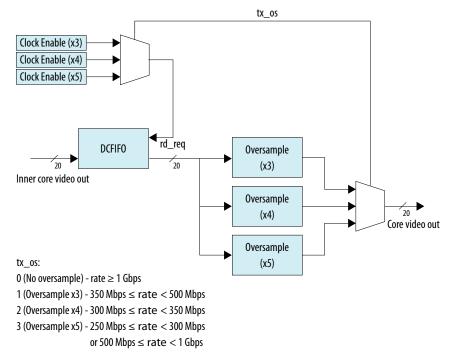

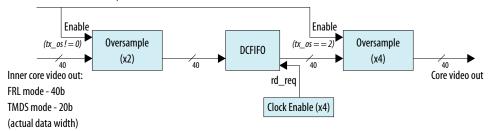

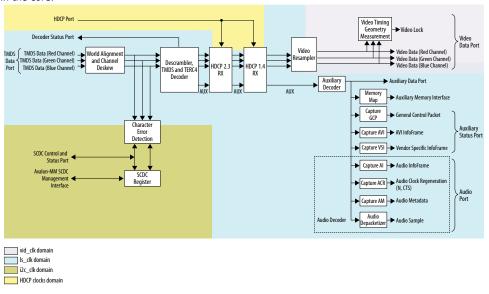

Figure 10. HDMI Hardware Design Example Block Diagram

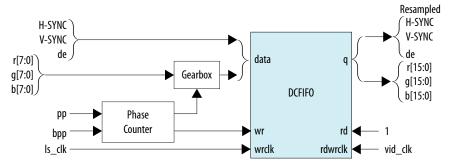

The figure below shows a high level architecture of the design.

The following details of the design example architecture correspond to the numbers in the block diagram.

- 1. The sink TMDS data has three channels: data channel 0 (blue), data channel 1 (green), and data channel 2 (red).

- 2. The Oversampler (RX) and dual-clock FIFO (DCFIFO) instances are duplicated for each TMDS data channel (0,1,2).

- 3. The video data input width for each color channel of the HDMI RX core is equivalent to RX transceiver PCS-PLD parallel data width per channel.

- 4. Each color channel is fixed at 16 bpc. The video data output width of the HDMI RX core is equivalent to the value of symbols per clock\*16\*3.

- 5. The video data input width of the Clocked Video Input (CVI) and Clocked Video Output (CVO) IP cores are equivalent to the value of NUMBER\_OF\_PIXELS\_IN\_PARALLEL \* BITS\_PER\_PIXEL\_PER\_COLOR\_PLANE \* NUMBER\_OF\_COLOR\_PLANES. To interface with the HDMI core, the values of NUMBER\_OF\_PIXELS\_IN\_PARALLEL, BITS\_PER\_PIXEL\_PER\_COLOR\_PLANE, and NUMBER\_OF\_COLOR\_PLANES must match the symbols per clock, 16 and 3 respectively.

- 6. The video data input width of the HDMI TX core is equivalent to the value of symbols per clock\*16\*3. You can use the user switch to select the video data from the CVO IP core (VIP passthrough) or DCFIFO (VIP bypass).

- 7. The video data output width for each color channel of the HDMI TX core is equivalent to TX transceiver PCS-PLD parallel data width per channel.

- 8. The DCFIFO and the Oversampler (TX) instances are duplicated for each TMDS data channel (0,1,2) and clock channel.

- 9. The Oversampler (TX) uses the clock enable signal to read data from the DCFIFO.

- 10. The source TMDS data has four channels: data channel 0 (blue), data channel 1 (green), data channel 2 (red), and clock channel.

- 11. The RX Multirate Reconfiguration Controller requires the status of TMDS\_Bit\_clock\_Ratio port to perform appropriate RX reconfiguration between the TMDS character rates below 340 Mcsc (HDMI 1.4b) and above 340 Mcsc (HDMI 2.0b). The status of the port is also required by the Nios II processor and the HDMI TX core to perform appropriate TX reconfiguration and scrambling.

- 12. The reset control and lock status signals from HDMI PLL, RX Transceiver Reset Controller and HDMI RX core.

- 13. The reset and oversampling control signals for HDMI PLL, TX Transceiver Reset Controller, and HDMI TX core. The lock status and rate detection measure valid signals from the HDMI sink initiate the TX reconfiguration process.

- 14. The  $I^2C$  SCL and SDA lines with tristate buffer for bidirectional configuration. Use the ALTIOBUF IP core for Arria V and Stratix V devices.

- 15. The SCDC is mainly designed for the source to update the TMDS\_Bit\_Clock\_Ratio and Scrambler\_Enable bits of the sink TMDS Configuration register. .

## 4.3.1.1. Transceiver Native PHY (RX)

- Transceiver Native PHY in Arria V devices

- To operate the TMDS bit rate up to 3,400 Mbps, configure the Transceiver Native PHY at 20 bits at PCS – PLD interface with the HDMI RX core at 2 symbols per clock. When the PCS – PLD interface width is 20 bits, the minimum link rate is 611 Mbps.

- To operate the TMDS bit rate up to 6,000 Mbps, configure the Transceiver Native PHY at 40 bits with the HDMI RX core at 4 symbols per clock. When the PCS – PLD interface width is 40 bits, the minimum link rate is 1,000 Mbps.

- Oversampling is required for TMDS bit rate which is below the minimum link rate.

- Transceiver Native PHY in Stratix V devices

- To operate the TMDS bit rate up to 6,000 Mbps, configure the Transceiver Native PHY at 20 bits at PCS – PLD interface with the HDMI RX core at 2 symbols per clock. When the PCS – PLD interface width is 20 bits, the minimum link rate is 611 Mbps.

# Table 11. Arria V and Stratix V Transceiver Native PHY (RX) Configuration Settings (6,000 Mbps)

This table shows an example of Arria V and Stratix V Transceiver Native PHY (RX) configuration settings for TMDS bit rate of 6,000 Mbps.

| Parameters                       | Settings |

|----------------------------------|----------|

| Datapath Options                 |          |

| Enable TX datapath               | Off      |

| Enable RX datapath               | On       |

| Enable Standard PCS              | On       |

| Initial PCS datapath selection   | Standard |

| Number of data channels          | 3        |

| Enable simplified data interface | On       |

| RX PMA                                 |            |

|----------------------------------------|------------|

| Data rate                              | 6,000 Mbps |

| Enable CDR dynamic reconfiguration     | On         |

| Number of CDR reference clocks         | 2 (4)      |

| Selected CDR reference clock           | 0 (4)      |

| Selected CDR reference clock frequency | 600 MHz    |

| PPM detector threshold                 | 1,000 PPM  |

|                                        | continued  |

<sup>(4)</sup> The Bitec HDMI HSMC 2.0 daughter card routes the TMDS clock pin to the transceiver serial data pin. To use the TMDS clock to drive the HDMI PLL, the TMDS clock must also drive the transceiver dedicated reference clock pin. The number of CDR reference clocks is 2 with reference clock 1 (unused) driven by the TMDS clock and reference clock 0 driven by the HDMI PLL output clock. The selected CDR reference clock will be fixed at 0.

| RX PMA                                              |    |

|-----------------------------------------------------|----|

| Enable rx_pma_clkout port                           | On |

| Enable rx_is_lockedtodata port                      | On |

| Enable rx_is_lockedtoref port                       | On |

| Enable rx_set_locktodata and rx_set_locktoref ports | On |

| Standard PCS                     |                                                                                            |  |

|----------------------------------|--------------------------------------------------------------------------------------------|--|

| Standard PCS protocol            | Basic                                                                                      |  |

| Standard PCS/PMA interface width | <ul><li>10 (for 1 symbol per clock)</li><li>20 (for 2 and 4 symbols per clock)</li></ul>   |  |

| Enable RX byte deserializer      | <ul><li>Off (for 1 and 2 symbols per clock)</li><li>On (for 4 symbols per clock)</li></ul> |  |

Table 12. Arria V and Stratix V Transceiver Native PHY (RX) Common Interface Ports

This table describes the Arria V and Stratix V Transceiver Native PHY (RX) common interface ports.

| Signals               | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clocks                |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| rx_cdr_refclk[1:0]    | Input     | <ul> <li>Input reference clock for the RX CDR circuitry.</li> <li>To support arbitrary wide data rate range from 250 Mbps to 6,000 Mbps, you need a generic core PLL to obtain a higher clock frequency from the TMDS clock. You need a higher clock frequency to create oversampled stream for data rates below the minimum transceiver data rate—for example, 611 Mbps or 1,000 Mbps).</li> <li>If the TMDS clock pin is routed to the transceiver dedicated reference clock pin, you only need to create one transceiver reference clock input. You can use the TMDS clock as reference clock for a generic core PLL to drive the transceiver.</li> <li>If you use Bitec HDMI HSMC 2.0 daughter card, the TMDS clock pin is routed to the transceiver serial data pin. In this case, to use the TMDS clock as a reference clock for a generic core PLL, the clock must also drive the transceiver dedicated reference clock. Connect bit 0 to the generic core PLL output and bit 1 to the TMDS clock and set the selected CDR reference clock at 0.</li> </ul> |

| rx_std_clkout[2:0]    | Output    | RX parallel clock output.  The CDR circuitry recovers the RX parallel clock from the RX data stream when the CDR is configured at lock-to-data mode.  The RX parallel clock is a mirror of the CDR reference clock when the CDR is configured at lock-to-reference mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| rx_std_coreclkin[2:0] | Input     | RX parallel clock that drives the read side of the RX phase compensation FIFO.  Connect to rx_std_clkout ports.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| rx_pma_clkout[2:0]    | Output    | RX parallel clock (recovered clock) output from PMA. Leave unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Resets              |       |                                                         |

|---------------------|-------|---------------------------------------------------------|

| rx_analogreset[2:0] | Input | Active-high, edge-sensitive, asynchronous reset signal. |

|                     |       | continued                                               |

| Resets               |       |                                                                                                                                                                                   |

|----------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      |       | When asserted, resets the RX CDR circuit, deserializer.<br>Connect to Transceiver PHY Reset Controller IP core.                                                                   |

| rx_digitalreset[2:0] | Input | Active-high, edge-sensitive, asynchronous reset signal. When asserted, resets the digital component of the RX data path. Connect to the Transceiver PHY Reset Controller IP core. |

| PMA Ports               |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rx_set_locktoref[2:0]   | Input  | When asserted, programs the RX CDR to lock to reference mode manually. The lock to reference mode enables you to control the reset sequence using rx_set_locktoref and rx_set_locktodata.  The Multirate Reconfiguration Controller (RX) sets this port to 1 if oversampling mode is required. Otherwise, this port is set to 0.  Refer "Transceiver Reset Sequence" in Transceiver Reset Control in Arria V/Stratix V Devices for more information about manual control of the reset sequence. |

| rx_set_locktodata[2:0]  | Input  | Always driven to 0. When rx_set_locktoref is driven to 1, the CDR is configured to lock-to-reference mode. Otherwise, the CDR is configured to lock-to-data mode.                                                                                                                                                                                                                                                                                                                               |

| rx_is_lockedtoref[2:0]  | Output | When asserted, the CDR is locked to the incoming reference clock. Connect this port to rx_is_lockedtodata port of the Transceiver PHY Reset Controller IP core when rx_set_locktoref is 1.                                                                                                                                                                                                                                                                                                      |

| rx_is_lockedtodata[2:0] | Output | When asserted, the CDR is locked to the incoming data. Connect this port to rx_is_lockedtodata port of Transceiver PHY Reset Controller IP core when rx_set_locktoref is 0.                                                                                                                                                                                                                                                                                                                     |

| rx_serial_data[2:0]     | Input  | RX differential serial input data.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PCS Ports                    |        |                                                   |

|------------------------------|--------|---------------------------------------------------|

| unused_rx_parallel_data      | Output | Leave unconnected.                                |

| rx_parallel_data[S*3*10-1:0] | Output | PCS RX parallel data.  Note: S=Symbols per clock. |

| Calibration Status Port |        |                                                                                                                                                                                                          |

|-------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rx_cal_busy[2:0]        | Output | When asserted, indicates that the initial RX calibration is in progress. This port is also asserted if the reconfiguration controller is reset. Connect to the Transceiver PHY Reset Controller IP core. |

| Reconfiguration Ports     |        |                                                                          |

|---------------------------|--------|--------------------------------------------------------------------------|

| reconfig_to_xcvr[209:0]   | Input  | Reconfiguration signals from the Transceiver Reconfiguration Controller. |

| reconfig_from_xcvr[137:0] | Output | Reconfiguration signals to the Transceiver Reconfiguration Controller.   |

#### 4.3.1.2. PLL Intel FPGA IP Cores

Use the PLL Intel FPGA IP core as the HDMI PLL to generate reference clock for RX or TX transceiver, link speed, and video clocks for the HDMI RX or TX IP core.

The HDMI PLL is referenced by the arbitrary TMDS clock. For HDMI source, you can reference the HDMI PLL by a separate clock source in the VIP passthrough design, which contains frame buffer. The HDMI PLL for TX has the same desired output frequencies as RX across symbols per clock and color depth.

- For TMDS bit rates ranging from 3,400 Mbps to 6,000 Mbps (HDMI 2.0), the TMDS clock rate is 1/40 of the TMDS bit rate. The HDMI PLL generates reference clock for RX/TX transceiver at 4 times the TMDS clock.

- For TMDS bit rates below 3,400 Mbps (HDMI 1.4b), the TMDS clock rate is 1/10 of the TMDS bit rate. The HDMI PLL generates reference clock for RX/TX transceiver at identical rate as the TMDS clock.

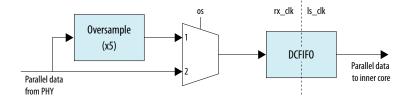

If the TMDS link operates at TMDS bit rates below the minimum RX/TX transceiver link rate, your design requires oversampling and a factor of 5 is chosen. The minimum link rate of the RX/TX transceiver vary across device families and symbols per clock. The HDMI PLL generates reference clock for RX/TX transceiver at 5 times the TMDS clock.

Note:

Place the PLL Intel FPGA block on the transmit path (pll\_hdmi\_tx) in the physical location next to the transceiver PLL.

## Table 13. HDMI PLL Desired Output Frequencies for 8-bpc Video

This table shows an example of HDMI PLL desired output frequencies across various TMDS clock rates and symbols per clock for all supported device families using 8-bpc video.

| Device<br>Family | Symbols<br>Per<br>Clock | Minimum<br>Link Rate<br>(Mbps) | TMDS Bit<br>Rate<br>(Mbps) | Oversampli<br>ng (5x)<br>Required | TMDS Clock<br>Rate (MHz) | RX/TX<br>Transceiver<br>Refclk<br>(MHz) | RX/TX Link<br>Speed<br>Clock<br>(MHz) | RX/TX<br>Video<br>Clock<br>(MHz) |

|------------------|-------------------------|--------------------------------|----------------------------|-----------------------------------|--------------------------|-----------------------------------------|---------------------------------------|----------------------------------|

|                  |                         | 611                            | 270                        | Yes                               | 27                       | 135                                     | 13.5                                  | 13.5                             |

|                  | 2                       |                                | 742.5                      | No                                | 74.25                    | 74.25                                   | 37.125                                | 37.125                           |

|                  | 2                       |                                | 1,485                      | No                                | 148.5                    | 148.5                                   | 74.25                                 | 74.25                            |

| Arria V          |                         |                                | 2,970                      | No                                | 297                      | 297                                     | 148.5                                 | 148.5                            |

| AITIG V          | 4                       | 4 1,000                        | 270                        | Yes                               | 27                       | 135                                     | 6.75                                  | 6.75                             |

|                  |                         |                                | 742.5                      | Yes                               | 74.25                    | 371.25                                  | 18.5625                               | 18.5625                          |

|                  |                         |                                | 1,485                      | No                                | 148.5                    | 148.5                                   | 37.125                                | 37.125                           |

|                  |                         |                                | 5,940                      | No                                | 148.5                    | 594                                     | 148.5                                 | 148.5                            |

|                  | 2                       | 611                            | 540                        | Yes                               | 54                       | 270                                     | 27                                    | 27                               |

| Stratix V        |                         |                                | 1,620                      | No                                | 162                      | 162                                     | 81                                    | 81                               |

|                  |                         |                                | 5,934                      | No                                | 148.35                   | 593.4                                   | 296.7                                 | 296.7                            |

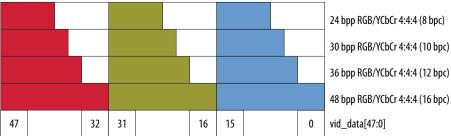

The color depths greater than 8 bpc or 24 bpp are defined to be deep color. For a color depth of 8 bpc, the core carries the pixels at a rate of one pixel per TMDS clock. At deeper color depths, the TMDS clock runs faster than the source pixel clock to provide the extra bandwidth for the additional bits.

The TMDS clock rate is increased by the ratio of the pixel size to 8 bits:

- 8 bits mode—TMDS clock = 1.0 × pixel or video clock (1:1)

- 10 bits mode—TMDS clock = 1.25 × pixel or video clock (5:4)

- 12 bits mode—TMDS clock = 1.5 × pixel or video clock (3:2)

- 16 bits mode—TMDS clock = 2 × pixel or video clock (2:1)

## Table 14. HDMI PLL Desired Output Frequencies for Deep Color Video

This table shows an example of HDMI PLL desired output frequencies across symbols per clock and color depths.

| Symbols<br>Per Clock | Oversam<br>pling<br>(5x)<br>Required | Bits Per<br>Compone<br>nt | TMDS Bit Rate<br>(Mbps) (5) | TMDS Clock<br>Rate (MHz) | RX/TX<br>Transceiver<br>Refclk (MHz) | RX/TX Link<br>Speed Clock<br>(MHz) | RX/TX Video<br>Clock (MHz) |

|----------------------|--------------------------------------|---------------------------|-----------------------------|--------------------------|--------------------------------------|------------------------------------|----------------------------|

|                      |                                      | 8                         | 270                         | 27                       | 135                                  | 13.5                               | 13.5                       |

| 2                    | Yes                                  | 10 (6)                    | 337.5                       | 33.75                    | 168.75                               | 16.875                             | 13.5                       |

| 2                    | ies                                  | 12 (6)                    | 405                         | 40.5                     | 202.5                                | 20.25                              | 13.5                       |

|                      |                                      | 16 <sup>(6)</sup>         | 540                         | 54                       | 270                                  | 27                                 | 13.5                       |

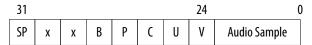

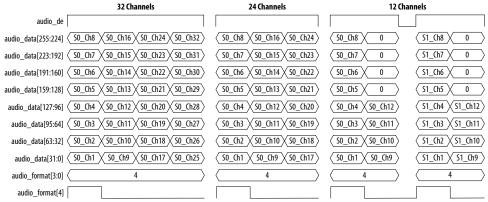

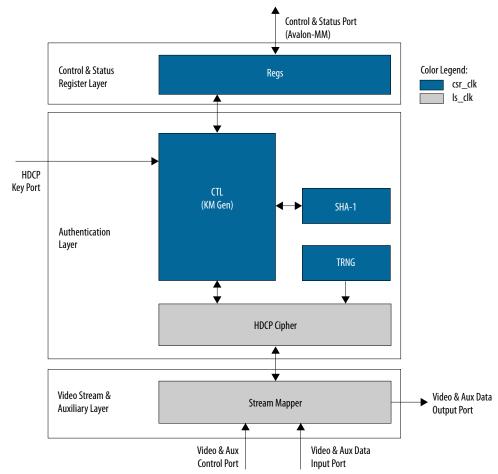

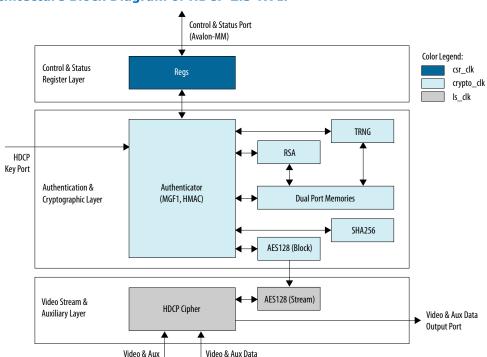

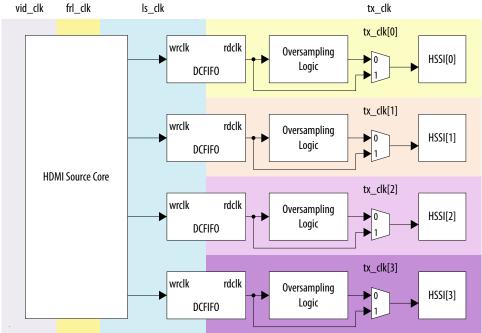

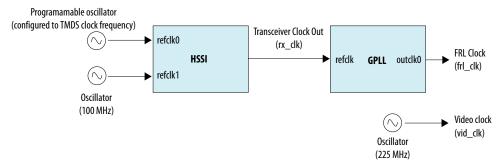

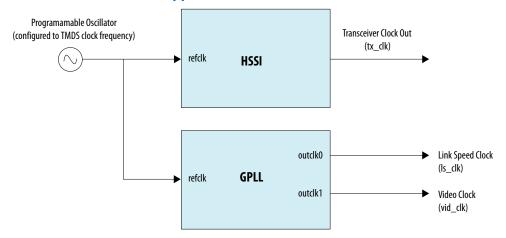

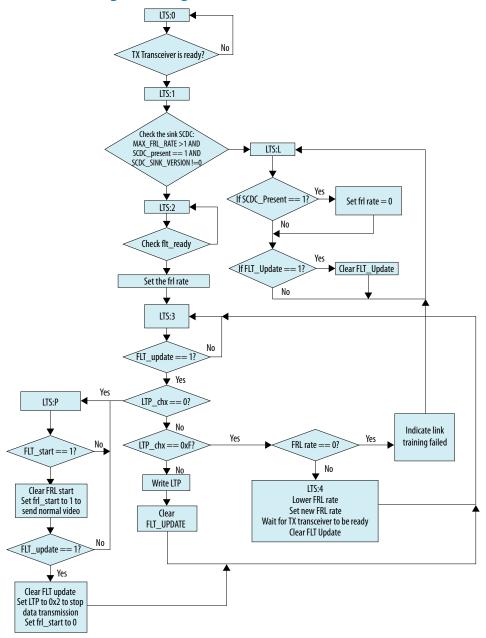

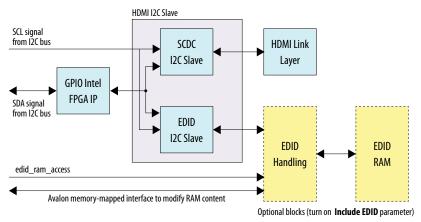

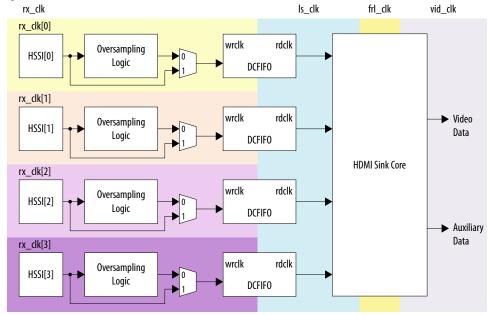

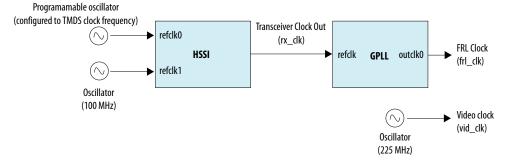

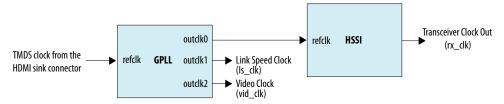

|                      |                                      | 8                         | 1,485                       | 148.5                    | 148.5                                | 37.125                             | 37.125                     |