# **50 Gbps Ethernet IP Core User Guide**

Updated for Intel® Quartus® Prime Design Suite: 17.0

Version: 2017.05.08

ID: **683158**

## **Contents**

| 1. Da             | tasheet                                                                                                                                                                                                                                                                                                        | 4                                                                        |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

|                   | 1.1. 50GbE IP Core Supported Features                                                                                                                                                                                                                                                                          | 5                                                                        |

|                   | 1.2. 50GbE IP Core Device Family and Speed Grade Support                                                                                                                                                                                                                                                       |                                                                          |

|                   | 1.2.1. Device Family Support                                                                                                                                                                                                                                                                                   |                                                                          |

|                   | 1.2.2. 50GbE IP Core Device Speed Grade Support                                                                                                                                                                                                                                                                | 7                                                                        |

|                   | 1.3. IP Core Verification                                                                                                                                                                                                                                                                                      |                                                                          |

|                   | 1.3.1. Simulation Environment                                                                                                                                                                                                                                                                                  |                                                                          |

|                   | 1.3.2. Compilation Checking                                                                                                                                                                                                                                                                                    |                                                                          |

|                   | 1.3.3. Hardware Testing                                                                                                                                                                                                                                                                                        |                                                                          |

|                   | 1.4. Performance and Resource Utilization                                                                                                                                                                                                                                                                      |                                                                          |

|                   | 1.5. Release Information                                                                                                                                                                                                                                                                                       | 9                                                                        |

| 2. Ge             | tting Started                                                                                                                                                                                                                                                                                                  | . 10                                                                     |

|                   | 2.1. Installing and Licensing IP Cores                                                                                                                                                                                                                                                                         |                                                                          |

|                   | 2.1.1. OpenCore Plus IP Evaluation                                                                                                                                                                                                                                                                             |                                                                          |

|                   | 2.2. Specifying the 50GbE IP Core Parameters and Options                                                                                                                                                                                                                                                       |                                                                          |

|                   | 2.3. Simulating the IP Core                                                                                                                                                                                                                                                                                    | 12                                                                       |

|                   | 2.4. Generated File Structure                                                                                                                                                                                                                                                                                  |                                                                          |

|                   | 2.5. Integrating Your IP Core in Your Design                                                                                                                                                                                                                                                                   |                                                                          |

|                   | 2.5.1. Pin Assignments                                                                                                                                                                                                                                                                                         |                                                                          |

|                   | 2.5.2. Adding the Transceiver PLL                                                                                                                                                                                                                                                                              |                                                                          |

|                   | 2.5.3. Placement Settings for the 50GbE IP Core                                                                                                                                                                                                                                                                |                                                                          |

|                   | 2.6. Compiling the Full Design and Programming the FPGA                                                                                                                                                                                                                                                        | . 17                                                                     |

|                   |                                                                                                                                                                                                                                                                                                                |                                                                          |

| 3. 50             | GbE IP Core Parameters                                                                                                                                                                                                                                                                                         | . 18                                                                     |

|                   |                                                                                                                                                                                                                                                                                                                |                                                                          |

|                   | nctional Description                                                                                                                                                                                                                                                                                           | . 19                                                                     |

|                   | nctional Description                                                                                                                                                                                                                                                                                           | . <b>19</b>                                                              |

|                   | 4.1. 50GbE IP Core Functional Description                                                                                                                                                                                                                                                                      | . <b>19</b><br>. 19                                                      |

|                   | 4.1. 50GbE IP Core Functional Description                                                                                                                                                                                                                                                                      | . <b>19</b><br>. 19<br>20                                                |

|                   | A.1. 50GbE IP Core Functional Description                                                                                                                                                                                                                                                                      | . <b>19</b><br>. 19<br>. 20<br>. 21                                      |

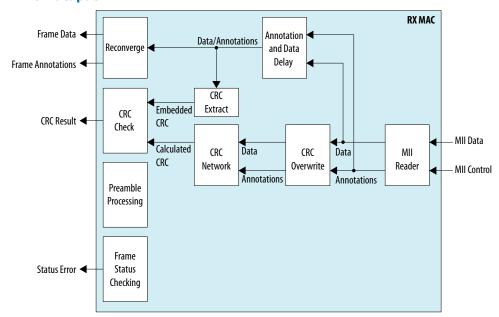

|                   | 4.1. 50GbE IP Core Functional Description                                                                                                                                                                                                                                                                      | . <b>19</b><br>. 19<br>. 20<br>. 21<br>. 25                              |

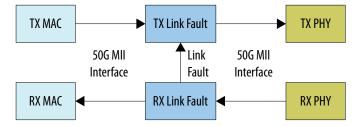

|                   | A.1. 50GbE IP Core Functional Description                                                                                                                                                                                                                                                                      | . 19<br>. 19<br>. 20<br>. 21<br>25<br>27                                 |

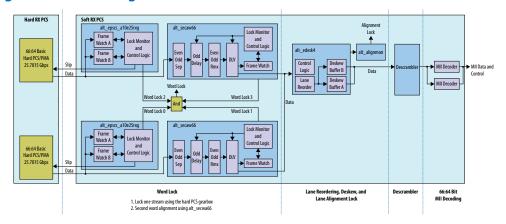

|                   | 4.1. 50GbE IP Core Functional Description                                                                                                                                                                                                                                                                      | . 19<br>. 20<br>. 21<br>. 25<br>. 27                                     |

| 4. Fu             | A.1. 50GbE IP Core Functional Description                                                                                                                                                                                                                                                                      | . 19<br>. 19<br>. 20<br>. 21<br>. 25<br>. 27<br>. 28                     |

| 4. Fu<br>5. Re    | A.1. 50GbE IP Core Functional Description                                                                                                                                                                                                                                                                      | . 19<br>19<br>20<br>21<br>25<br>27<br>28                                 |

| 4. Fu<br>5. Re    | A.1. 50GbE IP Core Functional Description.  4.1.1. 50GbE IP Core TX Datapath.  4.1.2. 50GbE IP Core RX Datapath.  4.1.3. Link Fault Signaling Interface.  4.1.4. 50 GbE RX PCS.  4.2. User Interface to Ethernet Transmission.  4.2.1. Order of Transmission.  4.2.2. Bit Order For TX and RX Datapaths.  set. | . 19<br>19<br>21<br>25<br>27<br>28<br>29                                 |

| 4. Fu<br>5. Re    | A.1. 50GbE IP Core Functional Description                                                                                                                                                                                                                                                                      | . 19<br>19<br>21<br>25<br>27<br>28<br>29                                 |

| 4. Fu<br>5. Re    | A.1. 50GbE IP Core Functional Description                                                                                                                                                                                                                                                                      | . 19<br>20<br>25<br>27<br>28<br>29<br>31                                 |

| 4. Fu<br>5. Re    | A.1. 50GbE IP Core Functional Description                                                                                                                                                                                                                                                                      | . 19<br>20<br>25<br>27<br>28<br>29<br>30                                 |

| 4. Fu<br>5. Re    | A.1. 50GbE IP Core Functional Description                                                                                                                                                                                                                                                                      | . 19<br>. 19<br>20<br>21<br>25<br>27<br>28<br>29<br>30<br>31<br>33       |

| 4. Fu<br>5. Re    | nctional Description                                                                                                                                                                                                                                                                                           | . 19<br>. 19<br>20<br>21<br>25<br>27<br>28<br>29<br>30<br>31<br>35<br>35 |

| 4. Fu<br>5. Re    | A.1. 50GbE IP Core Functional Description                                                                                                                                                                                                                                                                      | . 19<br>. 19<br>20<br>25<br>27<br>28<br>29<br>30<br>31<br>35<br>35<br>37 |

| 4. Fu<br>5. Re    | nctional Description                                                                                                                                                                                                                                                                                           | . 19<br>. 19<br>20<br>25<br>27<br>28<br>29<br>30<br>31<br>35<br>35<br>37 |

| 4. Fu 5. Re 6. In | A.1. 50GbE IP Core Functional Description                                                                                                                                                                                                                                                                      | . 19<br>20<br>25<br>28<br>29<br>31<br>33<br>35<br>35                     |

#### Contents

| 7.2. TX MAC Registers        | 42 |

|------------------------------|----|

| 7.3. RX MAC Registers        |    |

| 8. Debugging the Link        |    |

| 9. Document Revision History |    |

## 1. Datasheet

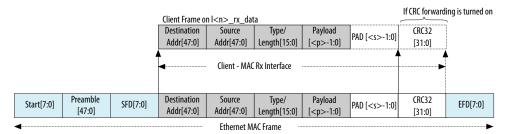

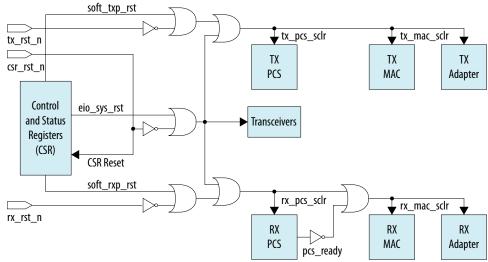

The Intel® 50 Gbps Ethernet (50GbE) IP core implements the 25G & 50G Ethernet Specification, Draft 1.4 from the 25 Gigabit Ethernet Consortium and the IEEE 802.3by 25Gb Ethernet draft. The IP core includes an option to support unidirectional transport as defined in Clause 66 of the IEEE 802.3-2012 Ethernet Standard. The MAC client side interface for the 50 Gbps Ethernet IP core is a 128-bit Avalon® Streaming (Avalon-ST) interface. It maps to two 25.78125 Gbps transceivers.

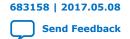

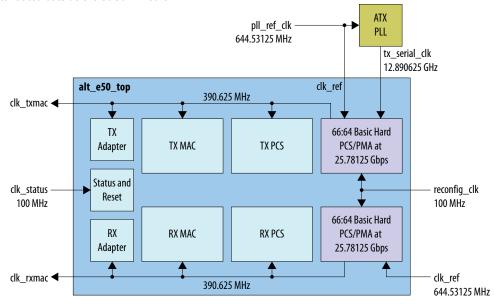

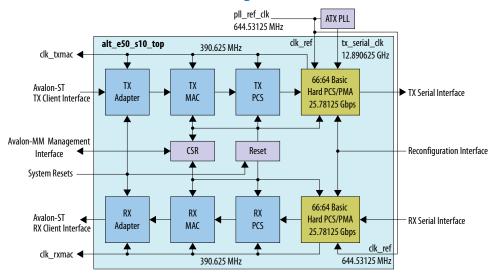

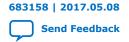

The IP core provides standard media access control (MAC) and physical coding sublayer (PCS), and PMA functions shown in the following block diagram. The PHY comprises the PCS and PMA.

Figure 1. 50GbE MAC and PHY IP Clock Diagram

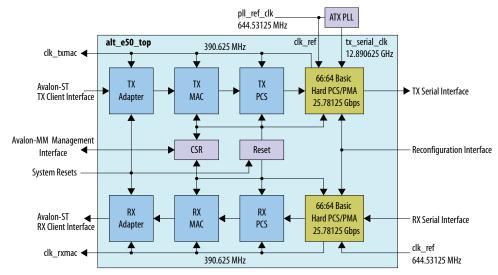

The following block diagram shows an example of a network application with 50GbE MAC and PHY.

Figure 2. Example Network Application

#### **Related Information**

- Introduction to Intel FPGA IP Cores

- Provides general information about all Intel FPGA IP cores, including parameterizing, generating, upgrading, and simulating IP cores.

- Creating Version-Independent IP and Qsys Simulation Scripts

Create simulation scripts that do not require manual updates for software or IP version upgrades.

- Project Management Best Practices

Guidelines for efficient management and portability of your project and IP files.

- 25 Gigabit Ethernet Consortium

## 1.1. 50GbE IP Core Supported Features

The 50GbE IP core supports the following features:

- Parameterizable through the IP Catalog available with the Quartus<sup>®</sup> Prime software.

- Designed to the 25G & 50G Ethernet Specification, Draft 1.4 from the 25 Gigabit Ethernet Consortium and designed to the IEEE 802.3by 25Gb Ethernet draft specification.

- Designed to the *IEEE 802.3ba-2012 High Speed Ethernet Standard* available on the *IEEE* website (www.ieee.org).

- Soft PCS logic that interfaces seamlessly to Intel FPGA 25.78125 gigabits per second (Gbps) serial transceivers.

- Avalon Memory-Mapped (Avalon-MM) management interface to access the IP core control and status registers.

- Avalon Streaming (Avalon-ST) data path interface connects to client logic.

- Support for jumbo packets, defined as packets greater than 1500 bytes.

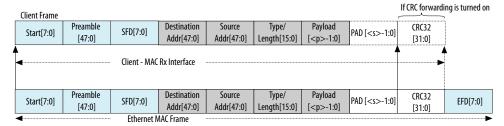

- Receive (RX) CRC removal and pass-through control.

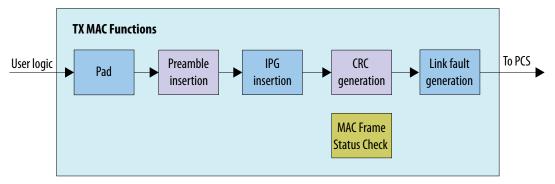

- · Transmit (TX) CRC generation.

- RX CRC checking and error reporting.

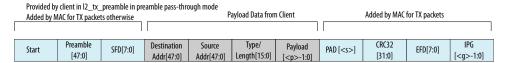

- RX and TX preamble pass-through option for applications that require proprietary user management information transfer.

- Optional RX strict SFD checking per IEEE specification.

- RX malformed packet checking per IEEE specification.

- TX automatic frame padding to meet the 64-byte minimum Ethernet frame length.

- Unidirectional transport as defined in Clause 66 of the IEEE 802.3-2012 Ethernet Standard

- Hardware and software reset control.

- MAC provides RX cut-through frame processing; MAC does not support RX storeand-forward capability.

- Deficit idle counter (DIC) to maintain a 12-byte inter-packet gap (IPG) average.

- Optional fault signaling detects and reports local fault and generates remote fault, with IEEE 802.3ba-2012 Ethernet Standard Clause 66 support.

- Programmable serial PMA local loopback (TX to RX) at the serial transceiver for self-diagnostic testing.

- Optional access to Altera Debug Master Endpoint (ADME) for serial link debugging.

- Ready latency of 0 clock cycles for Avalon-ST TX interface.

For a detailed specification of the Ethernet protocol refer to the *IEEE 802.3 Ethernet Standard*.

#### **Related Information**

**IEEE** website

The IEEE 802.3 Ethernet Standard is available on the IEEE website.

## 1.2. 50GbE IP Core Device Family and Speed Grade Support

#### 1.2.1. Device Family Support

**Table 1.** Intel IP Core Device Support Levels

| Device Support<br>Level | Definition                                                                                                                                                                                                                                            |  |  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Preliminary             | The IP core is verified with preliminary timing models for this device family. The IP core meets all functional requirements, but might still be undergoing timing analysis for the device family. It can be used in production designs with caution. |  |  |

| Final                   | The IP core is verified with final timing models for this device family. The IP core meets all functional and timing requirements for the device family and can be used in production designs.                                                        |  |  |

#### Table 2. 50GbE IP Core Device Family Support

Shows the level of support offered by the 50GbE IP core for each Intel device family.

| <b>Device Family</b>     | Support                                                                                                                                                                                                                                         |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arria <sup>®</sup> 10 GT | Default support level provided in the Quartus Prime software. Refer to the <i>Quartus Prime Standard Edition Software and Device Support Release Notes</i> and the <i>Quartus Prime Pro Edition Software and Device Support Release Notes</i> . |

| Other device families    | Not supported                                                                                                                                                                                                                                   |

#### **Related Information**

Timing and Power Models

Reports the default device support levels in the current version of the Quartus Prime Standard Edition software.

Timing and Power Models

Reports the default device support levels in the current version of the Quartus Prime Pro Edition software.

## 1.2.2. 50GbE IP Core Device Speed Grade Support

#### Table 3. Slowest Supported Device Speed Grades

| IP Core | Device Family | Supported Speed Grades |

|---------|---------------|------------------------|

| 50GbE   | Arria 10 GT   | E2                     |

#### 1.3. IP Core Verification

To ensure functional correctness of the 50GbE IP core, Intel performs extensive validation through both simulation and hardware testing. Before releasing a version of the 50GbE IP core, Intel runs comprehensive regression tests in the current version of the Quartus Prime software.

Intel verifies that the current version of the Quartus Prime software compiles the previous version of each IP core. Any exceptions to this verification are reported in the *Intel FPGA IP Release Notes*. Intel does not verify compilation with IP core versions older than the previous release.

#### **Related Information**

• Intel FPGA IP Release Notes

Changes to the IP core in major releases are noted in the 50GbE Intel FPGA IP Release Notes starting from the Quartus Prime software v17.0

• Quartus Prime Design Suite Update Release Notes

Includes changes in minor releases (updates).

#### 1.3.1. Simulation Environment

Intel performs the following tests on the 50GbE IP core in the simulation environment using internal and third-party standard bus functional models (BFM):

- Constrained random tests that cover randomized frame size and contents

- Assertion based tests to confirm proper behavior of the IP core with respect to the specification

- Extensive coverage of our runtime configuration space and proper behavior in all possible modes of operation

### 1.3.2. Compilation Checking

Intel performs compilation testing on an extensive set of 50GbE IP core variations and designs to ensure the Quartus Prime software places and routes the IP core ports correctly.

### 1.3.3. Hardware Testing

Intel performs hardware testing of the key functions of the 50GbE IP core using internal loopback and also with other 50G switches. The hardware tests also ensure reliable solution coverage for hardware related areas such as performance, link synchronization, and reset recovery.

#### 1.4. Performance and Resource Utilization

The following table shows the typical device resource utilization for selected configurations using the current version of the Quartus Prime software. With the exception of M20K memory blocks, the numbers of ALMs and logic registers are rounded up to the nearest 100. The timing margin for this IP core is a minimum of 15%.

#### Table 4. Performance and Resource Utilization for 50GbE IP Core

The following results are for a variant that excludes all optional features.

| Product ALMs I |      | Dedicated Logic Registers | M20K Memory Blocks |

|----------------|------|---------------------------|--------------------|

| 50GbE          | 9300 | 18600                     | 3                  |

#### **Related Information**

- 50GbE IP Core Parameters on page 18 Information about the IP core parameters.

- Fitter Resources Reports in the Quartus Prime Help

## 1.5. Release Information

### **Table 5. 50GbE IP Core Current Release Information**

| Item           | Description                                  |  |

|----------------|----------------------------------------------|--|

| Version        | 17.0                                         |  |

| Release Date   | 2017.05.08                                   |  |

| Ordering Codes | IP-50GEUMACPHY (IPR-50GEUMACPHY for renewal) |  |

## 2. Getting Started

## 2.1. Installing and Licensing IP Cores

The Intel Quartus Prime software installation includes the Intel FPGA IP library. This library provides useful IP core functions for your production use without the need for an additional license. Some IP cores in the library require that you purchase a separate license for production use. The OpenCore® feature allows evaluation of any Intel FPGA IP core in simulation and compilation in the Quartus Prime software. Upon satisfaction with functionality and performance, visit the Self Service Licensing Center to obtain a license number for any Intel FPGA product.

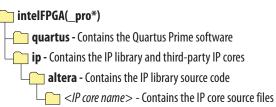

The Quartus Prime software installs IP cores in the following locations by default:

#### Figure 3. IP Core Installation Path

#### **Table 6. IP Core Installation Locations**

| Location                                                               | Software                       | Platform |

|------------------------------------------------------------------------|--------------------------------|----------|

| <pre><drive>:\intelFPGA_pro\quartus\ip\altera</drive></pre>            | Quartus Prime Pro Edition      | Windows* |

| <pre><drive>:\intelFPGA\quartus\ip\altera</drive></pre>                | Quartus Prime Standard Edition | Windows  |

| <pre><home directory="">:/intelFPGA_pro/quartus/ip/altera</home></pre> | Quartus Prime Pro Edition      | Linux*   |

| <pre><home directory="">:/intelFPGA/quartus/ip/altera</home></pre>     | Quartus Prime Standard Edition | Linux    |

### 2.1.1. OpenCore Plus IP Evaluation

The free OpenCore Plus feature allows you to evaluate licensed MegaCore IP cores in simulation and hardware before purchase. Purchase a license for MegaCore IP cores if you decide to take your design to production. OpenCore Plus supports the following evaluations:

- Simulate the behavior of a licensed IP core in your system.

- Verify the functionality, size, and speed of the IP core quickly and easily.

- Generate time-limited device programming files for designs that include IP cores.

- Program a device with your IP core and verify your design in hardware.

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2015 Registered

OpenCore Plus evaluation supports the following two operation modes:

- Untethered—run the design containing the licensed IP for a limited time.

- Tethered—run the design containing the licensed IP for a longer time or indefinitely. This operation requires a connection between your board and the host computer.

Note:

All IP cores that use OpenCore Plus time out simultaneously when any IP core in the design times out.

#### **Related Information**

- Quartus Prime Licensing Site

- Quartus Prime Installation and Licensing

## 2.2. Specifying the 50GbE IP Core Parameters and Options

The 50GbE parameter editor allows you to quickly configure your custom IP variation. Use the following steps to specify IP core options and parameters in the Quartus Prime software.

- Depending on whether you are using the Quartus Prime Pro Edition software or the Quartus Prime Standard Edition software, perform one of the following actions:

- In the Quartus Prime Pro Edition, click File ➤ New Project Wizard to create

a new Quartus Prime project, or File ➤ Open Project to open an existing

Quartus Prime project. The wizard prompts you to specify a device.

- In the Quartus Prime Standard Edition software, in the IP Catalog (Tools ➤ IP Catalog), select the Arria 10 target device family.

- 2. In the IP Catalog (**Tools** ➤ **IP Catalog**), locate and double-click the name of the IP core to customize. The New IP Variation window appears.

- 3. In the **New IP Variation** dialog box, specify a top-level name for your custom IP variation. The parameter editor saves the IP variation settings in a file named <your\_ip>.qsys (in Quartus Prime Standard Edition) or <your\_ip>.ip (in Quartus Prime Pro Edition).

- 4. In the Quartus Prime Standard Edition software, you must select a specific Arria 10 device in the **Device** field, or keep the default device the Quartus Prime software proposes.

- 5. Click **OK**. The parameter editor appears.

- 6. On the **IP** tab, specify the parameters for your IP core variation. Refer to 50GbE IP Core Parameters on page 18 for information about specific IP core parameters.

- 7. Optionally, to generate a simulation testbench or compilation and hardware design example, follow the instructions in the *Arria 10 50G Ethernet Design Example User Guide*.

- 8. Click **Generate HDL**. The **Generation** dialog box appears.

- 9. Specify output file generation options, and then click **Generate**. The IP variation files generate according to your specifications.

Note: A functional VHDL IP core is not available. Specify Verilog HDL only, for your IP core variation.

- 10. Click Finish. The parameter editor adds the top-level .qsys or .ip file to the current project automatically. If you are prompted to manually add the .qsys or .ip file to the project, click Project ➤ Add/Remove Files in Project to add the file.

- 11. After generating and instantiating your IP variation, make appropriate pin assignments to connect ports.

#### **Related Information**

Arria 10 50G Ethernet Design Example User Guide

Information about the **Example Design** tab in the 50GbE parameter editor.

## 2.3. Simulating the IP Core

You can simulate your 50GbE IP core variation with the functional simulation model and the testbench generated with the IP core. The functional simulation model is a cycle-accurate model that allows for fast functional simulation of your IP core instance using industry-standard Verilog HDL simulators. You can simulate the Intel-provided testbench or create your own testbench to exercise the IP core functional simulation model.

The functional simulation model and testbench files are generated in project subdirectories. These directories also include scripts to compile and run the design example.

Note:

Use the simulation models only for simulation and not for synthesis or any other purposes. Using these models for synthesis creates a nonfunctional design.

In the top-level wrapper file for your simulation project, you can set the the following RTL parameters to enable simulation optimization. These optimizations significantly decrease the time to reach link initialization.

- SIM\_SHORT\_RST: Shortens the reset times to speed up simulation.

- SIM\_SHORT\_AM: Shortens the interval between alignment markers to accelerate alignment marker lock.

- SIM\_SIMPLE\_RATE: Sets the PLL reference clock (clk\_ref) to 625 MHz instead of 644.53125 MHz to optimize PLL simulation model behavior

In general, parameters are set through the IP core parameter editor and you should not change them manually. The only exceptions are these simulation optimization parameters.

To set these parameters on the PHY blocks, add the following lines to the top-level wrapper file:

```

defparam <dut instance>.SIM_SHORT_RST = 1'b1;

defparam <dut instance>.SIM_SHORT_AM = 1'b1;

defparam <dut instance>.SIM_SIMPLE_RATE = 1'b1;

```

Note:

You can use the example testbench as a guide for setting the simulation parameters in your own simulation environment. These lines are already present in the Intel-provided testbench for the IP core.

#### **Related Information**

#### Simulating Intel FPGA Designs

Quartus Prime Standard Edition Handbook Volume 3: Verification chapter that provides information about simulating Intel FPGA IP cores.

#### 2.4. Generated File Structure

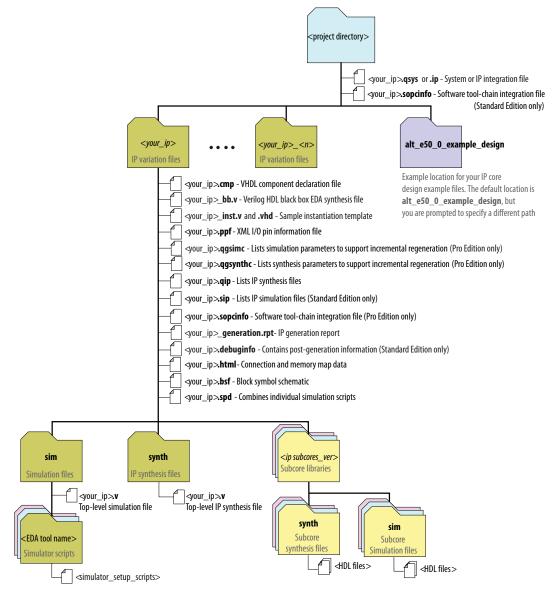

The Quartus Prime software generates the following IP core output file structure.

For information about the file structure of the design example, refer to the *Arria 10 50GbE Design Example User Guide*.

Figure 4. IP Core Generated Files

### **Table 7.** IP Core Generated Files

| File Name                                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre><your_ip>.qsys (Quartus Prime Standard Edition only)</your_ip></pre> | The Qsys system or top-level IP variation file. <pre></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <pre><your_ip>.ip (Quartus Prime Pro Edition only)</your_ip></pre>        | give your IP variation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <system>.sopcinfo</system>                                                | Describes the connections and IP component parameterizations in your Qsys system. You can parse its contents to get requirements when you develop software drivers for IP components.  Downstream tools such as the Intel Nios® II tool chain use this file.  The .sopcinfo file and the system.h file generated for the Nios II tool chain include address map information for each slave relative to each master that accesses the slave. Different masters may have a different address map to access a particular slave component. |

| <pre><your_ip>.cmp</your_ip></pre>                                        | The VHDL Component Declaration (.cmp) file is a text file that contains local generic and port definitions that you can use in VHDL design files.  This IP core does not support VHDL. However, the Quartus Prime software generates this file.                                                                                                                                                                                                                                                                                        |

| <pre><your_ip>.html</your_ip></pre>                                       | A report that contains connection information, a memory map showing the address of each slave with respect to each master to which it is connected, and parameter assignments.                                                                                                                                                                                                                                                                                                                                                         |

| <pre><your_ip>_generation.rpt</your_ip></pre>                             | IP or Qsys generation log file. A summary of the messages during IP generation.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <pre><your_ip>.debuginfo</your_ip></pre>                                  | Contains post-generation information. Used to pass System Console and Bus Analyzer Toolkit information about the Qsys interconnect. The Bus Analysis Toolkit uses this file to identify debug components in the Qsys interconnect. (Quartus Prime Standard Edition only)                                                                                                                                                                                                                                                               |

| <pre><your_ip>.qgsimc</your_ip></pre>                                     | Lists simulation parameters to support incremental regeneration. (Quartus Prime Pro Edition only)                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <pre><your_ip>.qgsynthc</your_ip></pre>                                   | Lists synthesis parameters to support incremental regeneration. (Quartus Prime Pro Edition only)                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <pre><your_ip>.qip</your_ip></pre>                                        | Contains all the required information about the IP component to integrate and compile the IP component in the Quartus Prime software.                                                                                                                                                                                                                                                                                                                                                                                                  |

| <pre><your_ip>.csv</your_ip></pre>                                        | Contains information about the upgrade status of the IP component.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <pre><your_ip>.bsf</your_ip></pre>                                        | A Block Symbol File (. <b>bsf</b> ) representation of the IP variation for use in Quartus Prime Block Diagram Files (. <b>bdf</b> ).                                                                                                                                                                                                                                                                                                                                                                                                   |

| <pre><your_ip>.spd</your_ip></pre>                                        | Required input file for ip-make-simscript to generate simulation scripts for supported simulators. The <b>.spd</b> file contains a list of files generated for simulation, along with information about memories that you can initialize.                                                                                                                                                                                                                                                                                              |

| <pre><your_ip>.ppf</your_ip></pre>                                        | The Pin Planner File (.ppf) stores the port and node assignments for IP components created for use with the Pin Planner.                                                                                                                                                                                                                                                                                                                                                                                                               |

| <pre><your_ip>_bb.v</your_ip></pre>                                       | You can use the Verilog black-box ( <b>_bb.v</b> ) file as an empty module declaration for use as a black box.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <pre><your_ip>.sip</your_ip></pre>                                        | Contains information required for NativeLink simulation of IP components. You must add the <b>.sip</b> file to your Quartus Prime project. (Quartus Prime Standard Edition only)                                                                                                                                                                                                                                                                                                                                                       |

| <pre><your_ip>_inst.v and _inst.vhd</your_ip></pre>                       | HDL example instantiation template. You can copy and paste the contents of this file into your HDL file to instantiate the IP variation.  This IP core does not support VHDL. However, the Quartus Prime software generates the _inst.vhd file.                                                                                                                                                                                                                                                                                        |

| File Name                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre><your_ip>.regmap</your_ip></pre>                        | If IP contains register information, .regmap file generates. The .regmap file describes the register map information of master and slave interfaces. This file complements the .sopcinfo file by providing more detailed register information about the system. This enables register display views and user customizable statistics in the System Console.                                                                      |

| <pre><your_ip>.svd</your_ip></pre>                           | Allows hard processor system (HPS) System Debug tools to view the register maps of peripherals connected to HPS within a Qsys system.  During synthesis, the .svd files for slave interfaces visible to System Console masters are stored in the .sof file in the debug section. System Console reads this section, which Qsys can query for register map information. For system slaves, Qsys can access the registers by name. |

| <pre><your_ip>.v and <your_ip>.vhd</your_ip></your_ip></pre> | HDL files that instantiate each submodule or child IP core for synthesis or simulation.  This IP core does not support VHDL. However, the Quartus Prime software generates this file.                                                                                                                                                                                                                                            |

| mentor/                                                      | Contains a ModelSim script msim_setup.tcl to set up and run a simulation.                                                                                                                                                                                                                                                                                                                                                        |

| aldec/                                                       | Contains a Riviera-PRO script rivierapro_setup.tcl to setup and run a simulation.                                                                                                                                                                                                                                                                                                                                                |

| synopsys/vcs/<br>synopsys/vcsmx/                             | Contains a shell script vcs_setup.sh to set up and run a VCS® simulation.  Contains a shell script vcsmx_setup.sh and synopsys_ sim.setup file to set up and run a VCS MX® simulation.                                                                                                                                                                                                                                           |

| cadence/                                                     | Contains a shell script ncsim_setup.sh and other setup files to set up and run an NCSIM simulation.                                                                                                                                                                                                                                                                                                                              |

| submodules/                                                  | Contains HDL files for the IP core submodule.                                                                                                                                                                                                                                                                                                                                                                                    |

| <pre><child cores="" ip="">/</child></pre>                   | For each generated child IP core directory, Qsys generates $\mathtt{synth/andsim/sub-directories}.$                                                                                                                                                                                                                                                                                                                              |

#### **Related Information**

50G Ethernet Design Example User Guide

Information about the 50GbE design example file structure.

## 2.5. Integrating Your IP Core in Your Design

## 2.5.1. Pin Assignments

When you integrate your 50GbE IP core instance in your design, you must make appropriate pin assignments. While compiling the IP core alone, you can create virtual pins to avoid making specific pin assignments for top-level signals. When you are ready to map the design to hardware, you can change to the correct pin assignments.

#### **Related Information**

Quartus Prime Help

For information about the Quartus Prime software, including virtual pins.

## 2.5.2. Adding the Transceiver PLL

The 50GbE IP core targets Arria 10 GT devices. Arria 10 GT devices require an external PLL to drive the TX transceiver serial clock, in order to compile and to function correctly in hardware.

#### Figure 5. PLL Configuration Example

The TX transceiver PLL is instantiated with an ATX PLL IP core. The TX transceiver PLL must always be instantiated outside the 50GbE IP core.

You can use the IP Catalog to create a transceiver PLL.

- Select Arria 10 Transceiver ATX PLL.

- In the parameter editor, set the following parameter values:

- PLL output frequency to 12890.625 MHz. The transceiver performs dual edge clocking, using both the rising and falling edges of the input clock from the PLL. Therefore, this PLL output frequency setting supports a 25.78125 Gbps data rate through the transceiver.

- PLL reference clock frequency to 644.53125 MHz.

You must connect the ATX PLL to the 50GbE IP core as follows:

- Connect the clock output port of the ATX PLL to the tx\_serial\_clk input pin for each 50GbE IP core PHY link to the same output port of the ATX PLL. Connect the ATX PLL output port to both tx serial clk[1] and tx serial clk[0].

- Connect the pll\_locked output port of the ATX PLL to the tx\_pll\_locked input port of the 50GbE IP core.

- Drive the ATX PLL reference clock port and the 50GbE IP core clk\_ref input port

with the same clock. The clock frequency must be the frequency you specify for

the ATX PLL IP core PLL reference clock frequency parameter.

#### **Related Information**

- Transceivers on page 35

- Arria 10 Transceiver PHY User Guide

Information about the correspondence between PLLs and transceiver channels, and information about how to configure an external transceiver PLL for your own design. You specify the clock network to which the PLL output connects by setting the clock network in the PLL parameter editor.

### 2.5.3. Placement Settings for the 50GbE IP Core

The Quartus Prime software provides the options to specify design partitions and LogicLock® or LogicLock Plus regions for incremental compilation, to control placement on the device. To achieve timing closure for your design, you might need to provide floorplan guidelines using one or both of these features.

The appropriate floorplan is always design-specific, and depends on your full design.

#### **Related Information**

Quartus Prime Standard Edition Handbook Volume 2: Design Implementation and Optimization

Describes incremental compilation, design partitions, and LogicLock regions.

Quartus Prime Pro Edition Handbook Volume 2: Design Implementation and Optimization

Describes incremental compilation, design partitions, and LogicLock Plus regions.

## 2.6. Compiling the Full Design and Programming the FPGA

You can use the **Start Compilation** command on the Processing menu in the Quartus Prime software to compile your design. After successfully compiling your design, program the targeted Intel FPGA with the Programmer and verify the design in hardware.

Note:

The 50GbE IP core design example synthesis directories include Synopsys Constraint (.sdc) files that you can copy and modify for your own design.

#### **Related Information**

- Incremental Compilation for Hierarchical and Team-Based Design

- Programming Intel Devices

- 50G Ethernet Design Example User Guide

Information about generating the design example and the design example directory structure.

## 3. 50GbE IP Core Parameters

The 50GbE parameter editor provides the parameters you can set to configure the 50GbE IP core and simulation testbenches.

The 50GbE parameter editor includes an **Example Design** tab. For information about that tab, refer to the *50G Ethernet Design Example User Guide*.

**Table 8.** IP Core Parameters

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Range                | <b>Default Setting</b>                                                                                                                                                                                                                                                                                                                                                     | Description                                                                                                                |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|

| General Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                            |  |  |

| Device Family Arria 10 Arria 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |                                                                                                                                                                                                                                                                                                                                                                            | Selects the device family.                                                                                                 |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      | MAC Optio                                                                                                                                                                                                                                                                                                                                                                  | ns                                                                                                                         |  |  |

| generation  Disabled  Signaling as defined in the IEEE 8 Standard for Ethernet. The MAC i Reconciliation Sublayer (RS) to m remote faults. When enabled, the transmit remote fault sequences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      | When enabled, the IP core implements link fault signaling as defined in the IEEE 802.3-2012 IEEE Standard for Ethernet. The MAC includes a Reconciliation Sublayer (RS) to manage local and remote faults. When enabled, the local RS TX logic can transmit remote fault sequences in case of a local fault and can transmit IDLE control words in case of a remote fault. |                                                                                                                            |  |  |

| Enable strict SFD checking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Enabled,<br>Disabled | Disabled                                                                                                                                                                                                                                                                                                                                                                   | When enabled, the IP core can implement strict SFD checking, depending on register settings.                               |  |  |

| passthrough  Disabled  pass-through mode. In RX preamble mode, the IP core passes the pream Frame Delimiter (SFD) to the client them out of the Ethernet packet. In through mode, the client specifies the passes the pream passes the pream passes the pream passes. The passes the pream passes the p |                      | When enabled, the IP core is in RX and TX preamble pass-through mode. In RX preamble pass-through mode, the IP core passes the preamble and Start Frame Delimiter (SFD) to the client instead of stripping them out of the Ethernet packet. In TX preamble pass-through mode, the client specifies the preamble and provides the SFD to be sent in the Ethernet frame.     |                                                                                                                            |  |  |