## austriamicrosystems AG

is now

# ams AG

The technical content of this austriamicrosystems datasheet is still valid.

#### **Contact information:**

### **Headquarters:**

ams AG

Tobelbaderstrasse 30

8141 Unterpremstaetten, Austria

Tel: +43 (0) 3136 500 0

e-Mail: ams\_sales@ams.com

Please visit our website at www.ams.com

AS3604 DataSheet

## Multi-Standard Power Management Unit

## 1 General Description

The AS3604 is a highly-integrated CMOS power management device designed specifically for portable devices such as mobile phones, PDAs, CD players, digital cameras and other devices powered by 1-cell lithium-based or 3- to 4-cell nickel-based batteries. It can be used for any mobile phone handset standards such as CDMA, WCDMA, GSM, GPRS, EDGE, UTMS and other Japanese or American standards.

The device incorporates low dropout regulators (LDOs), DC/DC converters, a complete battery charger, and an audio power amplifier onto one die.

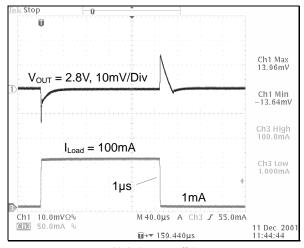

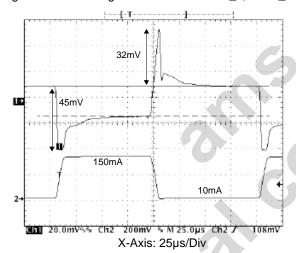

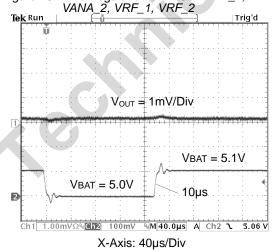

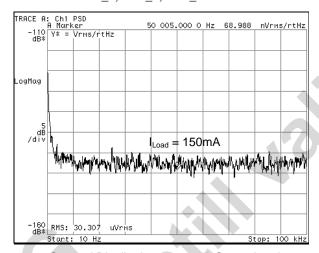

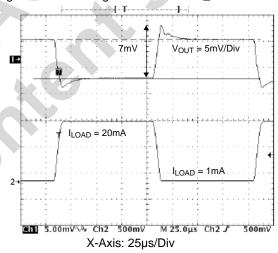

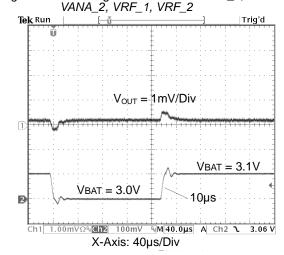

The linear analog LDOs feature extremely high performance regarding:

- Noise typ 30µVRMs from 100Hz to 100kHz

- Line/Load Regulation < 1mV static, < 10mV transient

- Power Supply Rejection > 70dB @ 1kHz

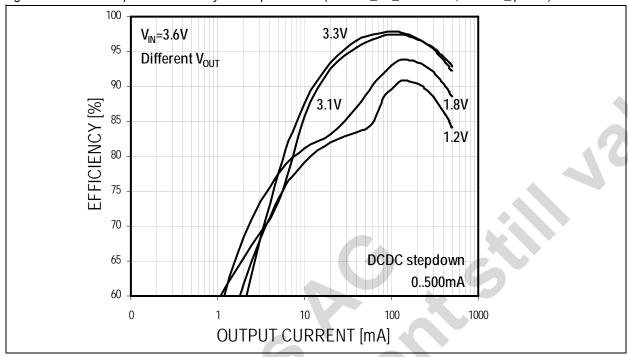

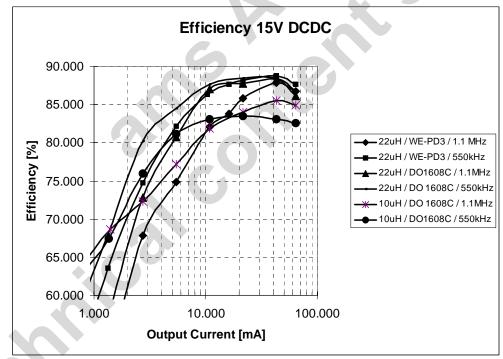

The integrated Step Down DC/DC Converter does not require an external Schottky diode yet provides very high efficiency (up to 95%) throughout the whole operating range. It can be either used as a stand-alone device or as a pre-regulator for LDOs to increase overall device efficiency.

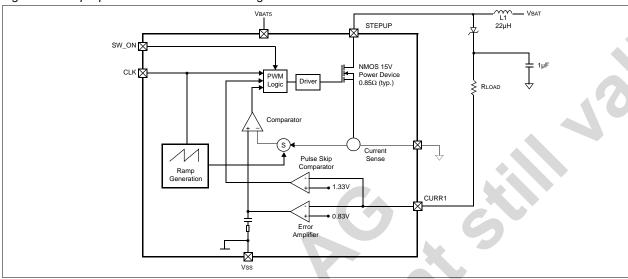

A Step Up DC/DC Converter is included to supply power for white LEDs, together with programmable current sources to control LED brightness.

A low-distortion audio power amplifier (1 Watt @  $8\Omega$ ) supports handsfree operation and HiFi ring-tones.

The device also features a chemistry-independent battery charger including automatic trickle charging, gas gauge, and programmable constant voltage and current charging.

The AS3604 is controlled via a serial interface and integrates all necessary system specific functions such as Reset, Watchdog, and Power-On Detection.

Output voltages and start-up timings can be programmed on metal-mask level, by register or by an external resistor.

## 2 Key Features

- Ten Programmable High Performance LDOs

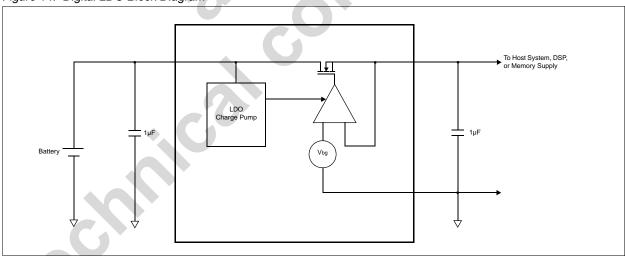

- Two Digital Low-Power LDOs (0.75 to 2.5V, 200mA; 250mA up to 1.4V)

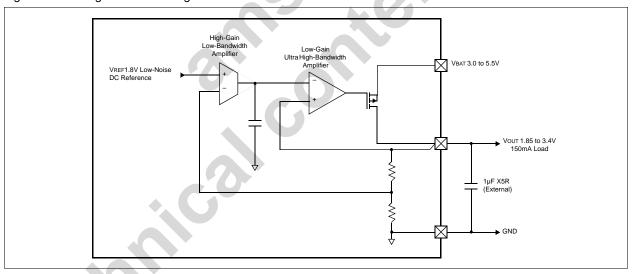

- Three RF Low-Noise LDOs (1.85 to 3.4V, 200mA)

- Two RF Low-Noise LDOs (1.85 to 3.4V, 150mA; 200mA up to 2.6V)

- One SIM Low-Power LDO (1.8 to 3.0V, 20mA)

- One Periphery Low-Noise LDO (2.5 to 3.2V, 200mA)

- One Low-Power LDO (2.5V, 10mA)

- Programmable High Efficiency DC/DC Converters

- Step Down: 0.8 to 3.4V, up to 500mA with 2.2MHz Operating Frequency and Small External Coil (2.2µH)

- Step Up: 15V, 45mA, (for White LEDs)

- Stereo Audio Power Amplifier

- 0.5W @  $4\Omega$  Stereo; 1W @  $8\Omega$  Bridged

- Digital Volume Control, 3dB Steps

- Click- and Pop-Less Start-Up and Power-Down

- Complete Chemistry-Independent Battery Charger

- Integrated Gas Gauge

- Automatic Trickle Charging

- Programmable Constant Current Charging

- Programmable Constant Voltage Charging

- Pulse Charging

- Safety Functions (Low Battery Shutdown)

- Over- and Under-Temperature Charge Disable

- Operation without Battery

- Can Regulate the Current Through the Battery or from the Charger

- Charger Input Overvoltage Protection (6V)

- Shutdown even with Connected Charger

- Charger Resume Operation

- Charger Interrupts (Inserted, Removed, Overvoltage, Resume)

- No-Battery Detection

- Momentary Power Loss Detection

- Battery Supply Short-Interruption Detection (<200ms); (e.g., due to a dropped phone)</li>

- Four Programmable Current Sources

- 8-Bit (0.625 to 160mA)

- Buzzer

- Vibrator

- LEDs

- Wide Battery Supply Range 3.0 to 5.5V

- Four General Purpose Switches ( $1\Omega$  and  $2\Omega$ )

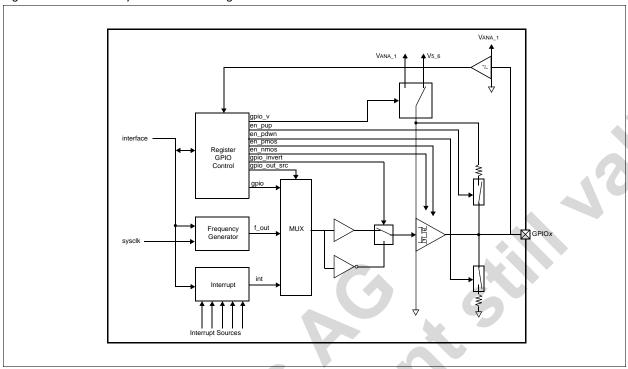

- Three Programmable General Purpose I/O Pins

- On-Chip Bandgap Tuning for High Accuracy (±1%)

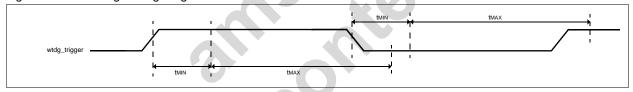

- Integrated Programmable Watchdog (7.5 to 1900ms)

- Programmable Reset (10 to 110ms)

- Shutdown Current typ 7µA (2.5V Always On)

- Overcurrent and Thermal Protection

- 0.35µ CMOS Solution

- 2.1 Watt Power Dissipation @ SCSB = 70°C

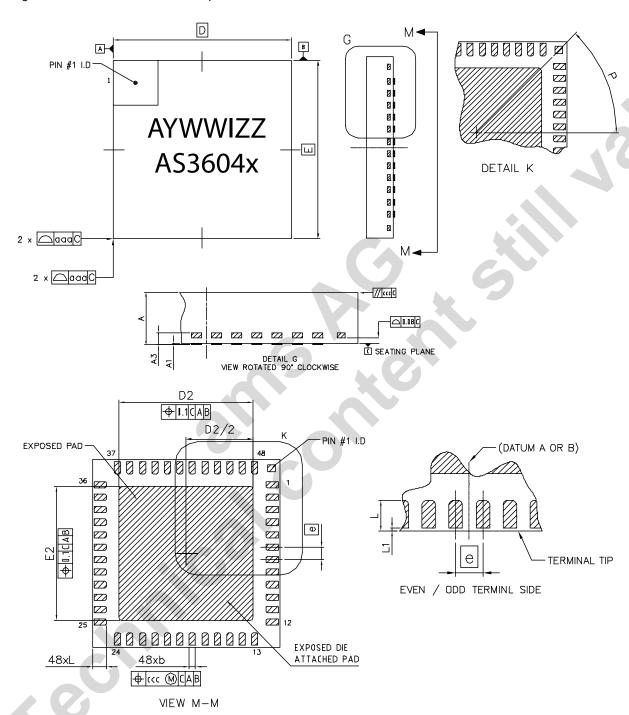

- 48-pin, 6x6mm QFN Package (0.4mm pitch)

## 3 Applications

Multi-standard power management for mobile phones, PDAs, and any other 1-cell Li+ or 3- to 4-cell NiMh powered devices.

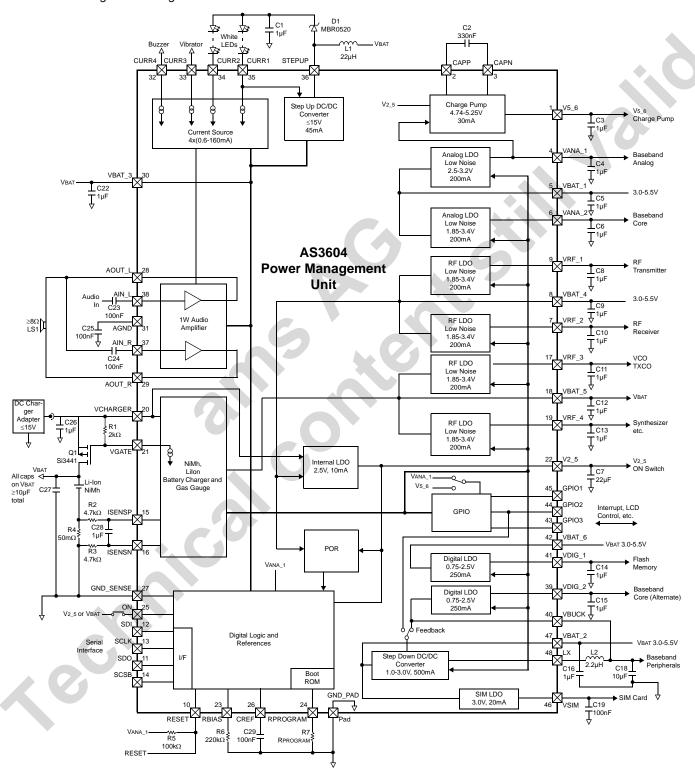

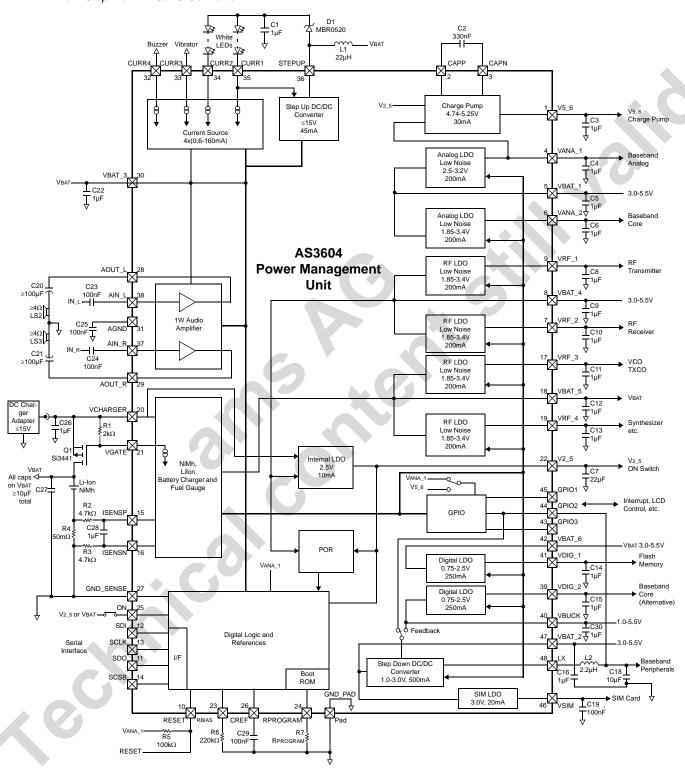

## 4 Block Diagrams

Figure 1. AS3604 Block Diagram. Option: Audio Amplifier In Differential Mode, Step Down DC/DC Converter as Pre-Regulator for Digital LDOs

Note: Refer to Table 38 on page 74 for specifications of external components.

Figure 2. AS3604 Block Diagram. Option: Audio Amplifier in Stereo Single-Ended Mode, Digital LDOs Separated from Step Down DC/DC Converter

Note: Refer to Table 38 on page 74 for specifications of external components.

#### Content

| 1  | General Description                      | ····· '  |

|----|------------------------------------------|----------|

| 2  | Key Features                             | <i>'</i> |

| 3  | Applications                             | <i>'</i> |

| 4  | Block Diagrams                           | 2        |

|    | Absolute Maximum Ratings (Non-Operating) |          |

|    | 5.1 Operating Conditions                 |          |

| 6  | Detailed Functional Descriptions         |          |

|    | 6.1 Battery Charger Controller           |          |

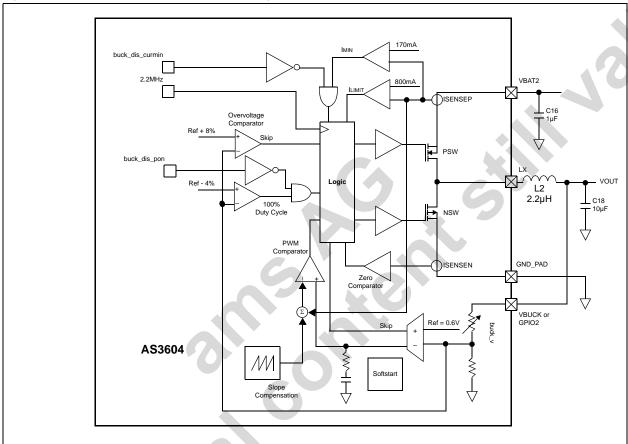

|    | 6.2 Step Down DC/DC Converter            |          |

|    | 6.3 Low Dropout Regulators               | 3        |

|    | 6.4 Charge Pump                          |          |

|    | 6.5 Step Up DC/DC Converter              | 4        |

|    | 6.6 General Purpose Input/Output         | 4        |

|    | 6.7 Current Sinks                        | 5        |

|    | 6.8 Audio Amplifier                      |          |

| 7  | System Supervisory Functions             |          |

|    | 7.1 Reset                                |          |

|    | 7.2 Startup                              |          |

|    | 7.3 Protection Functions                 |          |

|    | 7.4 Watchdog Block                       | 6        |

|    | 7.5 Internal Reference Circuits          |          |

|    | 7.6 Low Power Mode                       |          |

|    | 7.7 Boot Sequence Detection              |          |

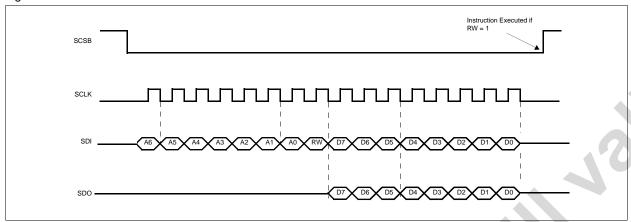

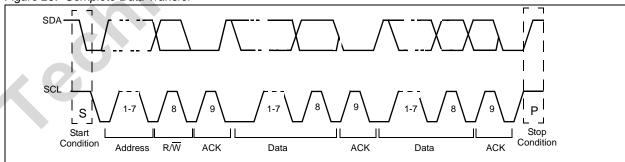

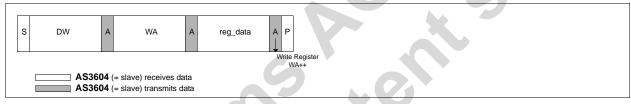

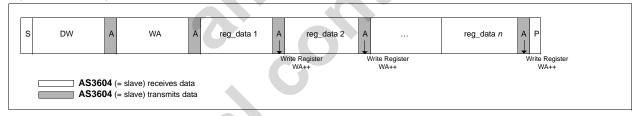

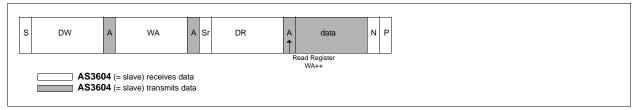

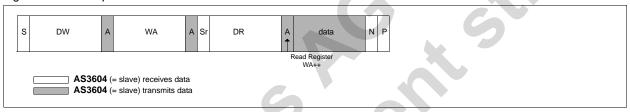

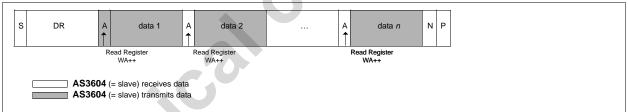

|    | 7.8 Serial Interface                     |          |

|    | Register Map                             |          |

| 9  | Pinout and Packaging                     |          |

|    | 9.1 Pin Descriptions                     |          |

|    | 9.2 Package Drawings and Markings        |          |

|    | External Parts List                      |          |

| 11 | Ordering Information                     | 7        |

## **Revision History**

| Revision | Date         | Owner | Description                                                     |

|----------|--------------|-------|-----------------------------------------------------------------|

| 1.0      | 23 June 2006 | ptr   | - Initial release.                                              |

| 1.1      | 3 March 2007 | ptr   | - Updated ambient temperature range.                            |

| 1.11     | 4 Dec 2008   | pkm   | - Updated internal LDO supply description                       |

| 1.2      | 8 Apr 2009   | pkm   | - Updated ordering info for AS3604B chip version                |

| 1.21     | 15 Mai 2009  | pkm   | - Updated abs. max ratings and stand-by current, deleted errata |

| 1.22     | 21 Aug 2009  | pkm   | - Updated operating current, SNR and VCHOV                      |

## 5 Absolute Maximum Ratings (Non-Operating)

Stresses beyond the absolute maximum ratings may cause permanent damage to the AS3604. These are stress ratings only. Functional operation of the device at these or beyond those in Operating Conditions is not implied.

Caution: Exposure to absolute maximum rating conditions may affect device reliability.

Table 1. Absolute Maximum Ratings

| Symbol | Parameter                            | Min   | Max  | Unit | Notes                                                                                                                                                                    |

|--------|--------------------------------------|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VIN_HV | High Voltage Pins                    | -0.3  | 18.0 | V    | Applicable for high voltage pins:<br>VCHARGER, VGATE, and STEPUP                                                                                                         |

| VIN_MV | 5V Pins                              | -0.3  | 7.0  | V    | Applicable for pins 5V pins:  VBAT_1 - VBAT_6, V5_6, VBUCK, GPIO1 - GPIO3, CURR1 - CURR4, AIN_L, AIN_R, AOUT_L, AOUT_R, VRF_1 - VRF_4 (when not in LDO-mode), ON, and LX |

| VIN_LV | 3.3V Pins                            | -0.3  | 5.0  | V    | Applicable for 3.3V pins:<br>RESET, SCSB, SCLK, SDI, SDO, VANA_1,<br>VANA_2, VSIM, VDIG_1, VDIG_2, CAPN,<br>AGND, ISENSP, ISENSN, V2_5, CREF,<br>RBIAS, and RPROGRAM     |

| lin    | Input Pin Current                    | -25   | +25  | mA   | At 25°C Norm: JEDEC 17                                                                                                                                                   |

| Tstrg  | Storage Temperature Range            | -55   | 125  | °C   | *                                                                                                                                                                        |

|        | Humidity                             | 5     | 85   | %    | Non-condensing                                                                                                                                                           |

| VESD   | Electrostatic Discharge              | -1000 | 1000 | V    | Norm: MIL 883 E Method 3015; ±1000V.                                                                                                                                     |

| Рт     | Total Power Dissipation              |       | 2.1  | W    | TAMB = 70°C                                                                                                                                                              |

| Tmax   | Peak Reflow Soldering<br>Temperature |       | 260  | °C   | T = 20 to 40s, according to the <i>IPC/JEDEC J-STD 020C</i> .                                                                                                            |

## 5.1 Operating Conditions

Table 2. Operating Conditions

| Symbol    | Parameter                                         | Min  | Тур         | Max  | Unit     | Notes                                                                                                              |

|-----------|---------------------------------------------------|------|-------------|------|----------|--------------------------------------------------------------------------------------------------------------------|

| VHV       | High Voltage                                      | 0.0  |             | 15.0 | V        | Pins VCHARGER, VGATE and STEPUP                                                                                    |

| VBAT      | Battery Voltage                                   | 3.0  | 3.6         | 5.5  | ٧        | For pins VBAT_1 - VBAT_6. During startup from ext. battery charger adapter, the battery voltage can be below 3.0V. |

| VANA_1    | Periphery Supply Voltage (for RESET and SPI pins) | 2.5  | Boot<br>ROM | 3.2  | <b>V</b> | Internally generated from VANA_1.                                                                                  |

| Von       | Activation voltage for ON pin                     | 1.75 | V2_5        | VBAT | V        |                                                                                                                    |

| V2_5      | Voltage on Pin V2_5                               | 2.4  | 2.5         | 2.6  | V        | Internally generated.                                                                                              |

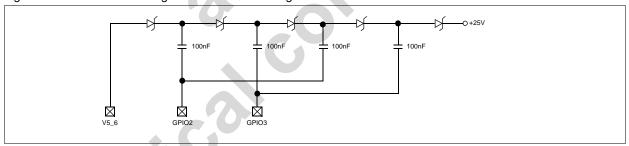

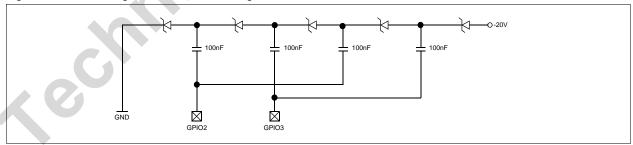

| V5_6      | Output Voltage of Charge Pump                     | 5.0  | 5.2         | 5.6  | ٧        | 2 x VANA_1                                                                                                         |

| Тамв      | Ambient Temperature                               | -40  | 25          | 85   | ô        |                                                                                                                    |

| Іват      | Operating Current                                 |      | 195         | 260  | μA       | Normal operating current. With bit low_power_on (page 62) = 0; only VANA_1 active, no additional external loads.   |

| ILOWPOWER | Low-Power Mode Current<br>Consumption             |      | 110         |      | μA       | With bit low_power_on (page 62) = 1; only VANA_1 active, no additional external loads.                             |

| IPOWEROFF | Power-Off Mode Current<br>Consumption             |      | 13          | 20   | μΑ       | With bit <b>power_off (page 57)</b> = 1; only V2_5 is active in power off mode. not tested, guaranteed by design   |

## 6 Detailed Functional Descriptions

#### 6.1 Battery Charger Controller

The AS3604 can serve as a standalone Battery Charger Controller supporting rechargeable lithium-ion (Li+), lithium-polymer (LiPo) and 3- or 4-cell nickel metal-hydride (NiMh) batteries.

The main features of the Battery Charger Controller are:

- Constant Voltage Charge Mode Described on page 9

- Pulse Charge Mode Described on page 11

- Battery Presence Detection Described on page 14

- Operation Without Battery Described on page 14

- Charge Controller Bypass Described on page 14

- Overvoltage and Undervoltage Supervision Described on page 15

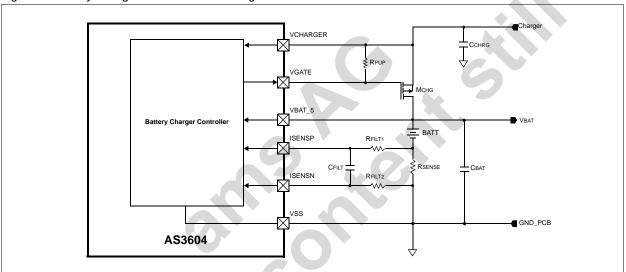

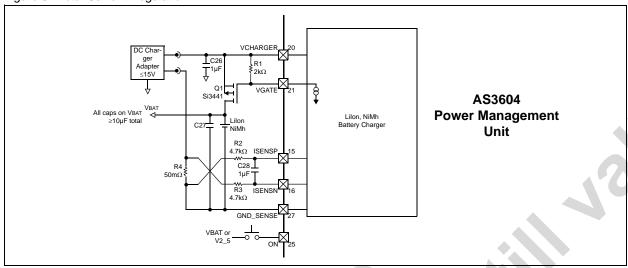

Figure 3. Battery Charger Controller Block Diagram

Table 3. Battery Charger Controller Components

| Symbol   | Parameter                                        | Value                                           | Notes                                                                          |  |

|----------|--------------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------|--|

| Мснв     | P-Channel MOSFET                                 | Si3441BDV, Si8401DB<br>or similar               | The maximum power dissipation of this transistor is not limited by the AS3604. |  |

| Rpup     | Pull-Up Resistor                                 | 2KΩ ± 5%                                        |                                                                                |  |

| Rsense   | Current Sense Resistor                           | $50m\Omega \pm 1\%$ , 125mW for IVBAT,DC < 1.5A | e.g. Vishay Dale WSL0805                                                       |  |

| RFILT1,2 | Filter Resistor                                  | 47KΩ ± 1%                                       | Can be omitted if Gas Gauge functionality                                      |  |

| CFILT    | Filter Capacitor                                 | 100nF ± 20%, X5R or<br>X7R Dielectric           | is not used (RFILT1,2 = $0\Omega$ )                                            |  |

| CCHRG    | Bypass Capacitor on pin VCHARGER                 | 1μF ± 20%, X5R or<br>X7R Dielectric             |                                                                                |  |

| Сват     | Minimum Total Capacitance<br>Parallel to Battery | 10μF                                            |                                                                                |  |

Table 4. Battery Charger Controller Parameters

| Symbol    | Parameter                                                             | Min  | Тур   | Max  | Unit     | Notes                                                                    |  |

|-----------|-----------------------------------------------------------------------|------|-------|------|----------|--------------------------------------------------------------------------|--|

| VCHDET    | Charger Detection Threshold.<br>VCHARGER - VBAT_5: Charger On         | 50   | 75    | 105  | mV       | Hysteresis = (VCHDET - VCHMIN)<                                          |  |

| VCHMIN    | Charger Detection Threshold.<br>VCHARGER - VBAT_5: Charger Off        | 5    | 20    | 35   | mV       | 40mV                                                                     |  |

| VCHREG    | Bootstrap Regulator Voltage                                           | 2.4  | 2.5   | 2.6  | V        | VCHARGER > 5V                                                            |  |

| Vсноvн    | VOLIA DOED Occurrents on Data etter                                   | 6.2  | 6.45  | 6,71 | V        | Monitor voltage on VCHARGER and                                          |  |

| Vсноv     | VCHARGER Overvoltage Detection                                        | 5,81 | 6.05  | 6,29 | V        | disable charging if this voltage is exceeded.                            |  |

| Vuvlo     | Undervoltage Leekeut Threehold                                        |      | 3.1   |      | V        | VBAT rising                                                              |  |

| VUVLO     | Undervoltage Lockout Threshold                                        |      | 2.8   |      | V        | VBAT falling                                                             |  |

| Vovlo     | Over reliance Leader to Three held                                    |      | 5.5   |      | <b>\</b> | VBAT rising                                                              |  |

| VOVLO     | Overvoltage Lockout Threshold                                         |      | 5.4   |      | V        | VBAT falling                                                             |  |

|           | Charge Termination Threshold                                          |      | 4.20  | 4.26 |          | Li+ Battery: <b>BatType (page 20)</b> = 0,<br><b>Li4v2 (page 20)</b> = 1 |  |

| VCHOFF    |                                                                       |      | 4.1   | 4.15 | V        | Li+ Battery: BatType = $0$ , Li4v2 = $0$ .<br>From -5 to +50°C           |  |

|           |                                                                       | 5.44 | 5.5   | 5.6  |          | NiMh Battery: BatType = 1                                                |  |

| VNOBATDET | No-Battery Detection Threshold and Charger Resume Detection Threshold |      | 3.644 |      | V        | <b>DisOWB (page 21)</b> = 0                                              |  |

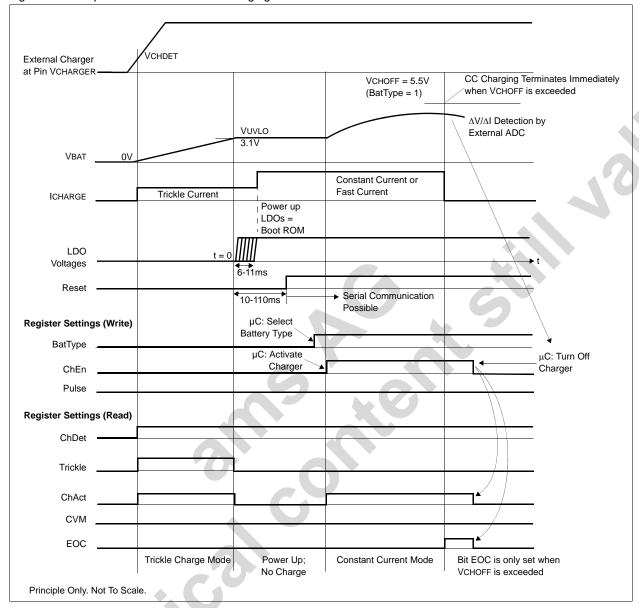

#### 6.1.1 Low-Current Trickle Charge Mode

Low-Current Trickle Charge mode is initiated when an external battery charger has been detected, bit chDet (page 19) = 1, and the battery voltage is below the VUVLO threshold; bits ChAct (page 19) and Trickle (page 19) will be set. In Trickle Charge mode the charge current will be limited to the value specified by Trickle Current (page 21) to prevent undue stress on either the battery or the Battery Charger in case of deeply discharged batteries.

Once VUVLO has been exceeded, the Battery Charger will terminate Trickle Charge mode (charger must not be disabled between trickle and constant current (fast) charging), reset bits **ChAct** and **Trickle**, and switch on the device.

The trickle charge is terminated in any case after approximately 60 minutes (as it is assumed that the battery is damaged in this case)

#### 6.1.2 Constant Current Charge Mode

Constant Current mode is initiated by setting bit ChEn (page 20) and resetting bit Fast (page 20). Bit ChAct (page 19) is set automatically when the Battery Charger starts. Charge current will be limited to the value specified by bit Constant Current (page 21) by the Battery Charger Controller.

#### 6.1.3 Charging Nickel-based Batteries

For nickel-based batteries (NiMh), BatType (page 20) must be 1 (see Figure 4 on page 9). The endpoint detection ( $\Delta V/\Delta t$ ) must be performed by the host controller. It must turn off the charger duly to avoid overcharging. In any case, when the battery voltage exceeds the charge termination threshold (typ. 5.5V), the charger will be turned off and bit EOC (page 20) will be set.

#### 6.1.4 Charging Lithium-based Batteries

For lithium-based batteries (Lithium-Ion, Lithium-Polymer), BatType (page 20) must be 0. Additionally, bit Li4v2 (page 20) can select between coke- and graphite-anode, setting different charge termination thresholds (typ. 4.1 or 4.2V). The charger is designed to charge 1-cell lithium-based batteries independently, using Trickle Charge, Constant Current, Constant Voltage, or Pulse Charge modes.

When the battery voltage exceeds the charge termination threshold during Constant Current mode, it automatically continues charging with either Constant Voltage mode, bit **Pulse** (page 20), or Pulse Charge mode, **Pulse**, and terminates when the end-of-charge conditions are met (see Figure 5 on page 11 and Figure 6 on page 13).

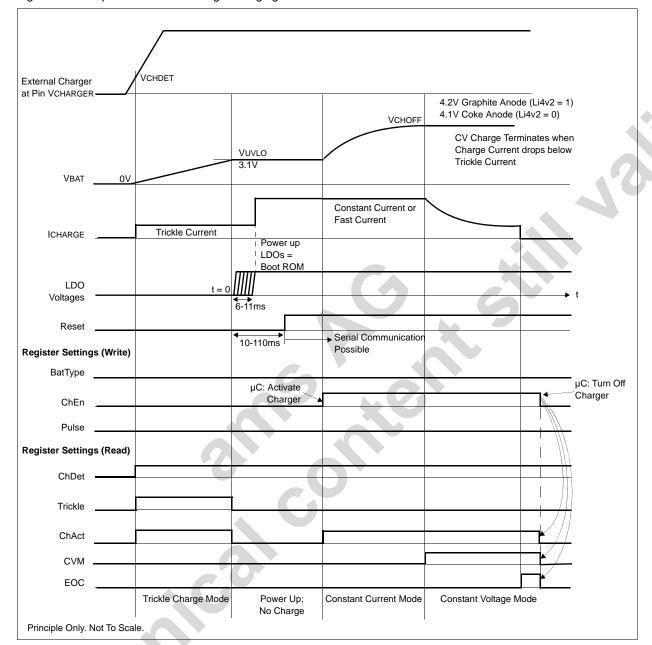

Figure 4. Startup and Constant Current Charging of Nickel-based Batteries

#### 6.1.5 Fast Charge Mode

As an alternative to Constant Current mode, Fast Charge mode may be selected. The charge current will not be controlled in this mode and is only limited by the external battery charger adapter.

Fast Charge mode is initiated by setting bits ChEn (page 20) and Fast (page 20). Bit ChAct (page 19) is set when the Battery Charger has started.

#### End of Charge

In Fast Charge mode, the same charge termination thresholds apply as for Constant Current mode. Additionally, depending on bit **Fast (page 20)**, the current during pulse charging is either the selected constant current or maximum. Charging will resume if the battery voltage drops below VNOBATDET.

#### 6.1.6 Constant Voltage Charge Mode

Constant Voltage mode is initiated and bit CVM (page 19) will be set when threshold VCHOFF (page 8) has been exceeded for the first time (no debounce filter) and bit Pulse (page 20) is not set.

The charge controller will regulate the battery voltage to a value set by bit **Li4v2** (page 20). To enable operation of the device without a battery connected to the system it is necessary that the charger is not disabled between the moment when the VCHOFF threshold is exceeded for the first time and the beginning of constant voltage charge mode.

- During Constant Voltage mode, the charge current will decrease and eventually drop below the value set by Trickle Current (page 21). If the measured charge current is less than or equal to Trickle Current, charging is terminated and bit EOC is set. Charging will resume if the battery voltage drops below VNOBATDET.

If the battery has been removed during constant voltage charging the EOC condition and the no battery condition will probably conflict. To be able to properly detect the EOC state the EOC condition has to be dominant over the no battery condition.

- If the battery voltage (VBAT\_5) drops below VNOBATDETECT (page 8) (signal resume starts pulsing), e.g. if the battery is removed after charging is finished, EOC (page 20) will be cleared (after debounce time) and the battery charger controller will resume in constant voltage mode to enable operation of the device without battery. This only works if bit CVM (page 19) remains set when bit EOC is set, otherwise the comparators that are required for operation without battery are gated.

Three scenarios are possible at this point:

- If a battery is connected the charge current will now be high and charging will return to constant current charging.

- 2. No battery is connected and no current will flow through the sense resistor. Now the no battery condition is detected properly.

- 3. The battery was connected and is disconnected. No current will flow through the sense resistor and the no battery condition is detected properly.

In summary: When charging is resumed after an EOC state either a (dis)charge current will be measured and the charge controller will return to constant current mode or no current will be measured and a "no battery" condition is indicated. To be able to handle supply voltage spikes caused by e.g. battery bouncing when the system is heavily shaken the VNOBATDETECT detection has to be debounced for 1 current measurement cycle

before EOC is cleared. After the debounce time is over additional pulses must occur during the next current

If the battery is replaced after charging is finished and the charge current exceeds the value set by **Constant Current (page 21)**, the charge controller will clear bit **CVM** and return to Constant Current or Fast Charge mode, depending on bit **Fast (page 20)**.

measurement cycle to clear EOC. The no battery status is indicated with bit NoBat (page 20).

#### Notes:

- 1. Bit CVM will be ambiguous if bit Fast is set.

- 2. EOC will only be entered if bit AutoChgTerm (page 21) is set (default = 0).

Figure 5. Startup and Constant Voltage Charging of Lithium-based Batteries

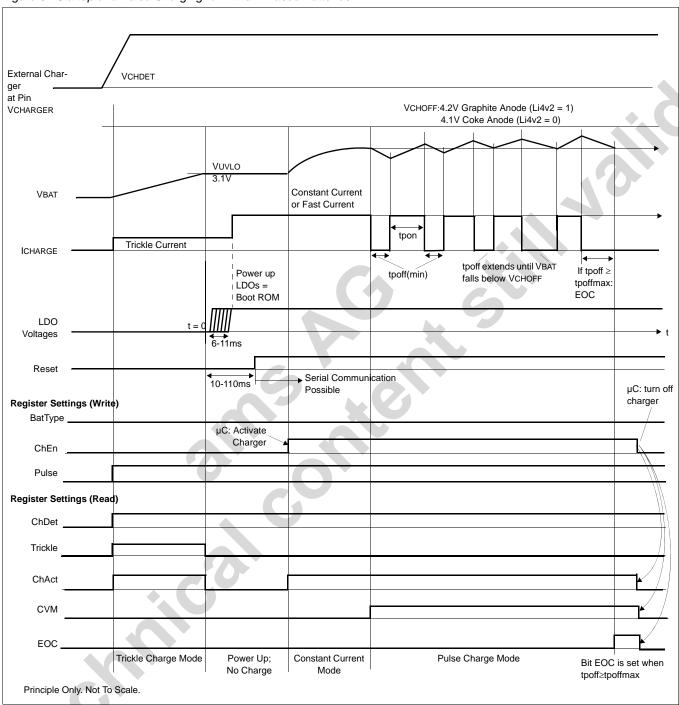

#### 6.1.7 Pulse Charge Mode

Pulse Charge mode is initiated and bit CVM (page 19) will be set when the VCHOFF (page 8) threshold has been exceeded for the first time and bit Pulse (page 20) is set. If the battery voltage is below the VCHOFF threshold, the Battery Charger will be enabled for a minimum on-time specified by bit TPON (page 21).

If the battery voltage drops below VCHOFF at the end of the minimum on-time, the Battery Charger will remain switched on until the battery voltage exceeds VCHOFF. The Battery Charger will then be disabled for at least the minimum off-time specified by bit **TPOFF** (page 21), and the Battery Charger will only be switched on again when the battery voltage falls below VCHOFF. In any case, whenever the instantaneous battery voltage exceeds the overvoltage lockout threshold VOVLO, charging is disabled immediately.

Battery Charger Controller

Data Sheet

During on-pulses, the charge current will be limited to the value set by **Constant Current (page 21)** if bit **Fast (page 20)** = 0. If bit **Fast** = 1, the charger transistor Q1 (page 2) will be fully on and the charge current during on-pulses will only be limited by the external charge adapter.

At the beginning of a Pulse Charge cycle, the Battery Charger will operate at a duty cycle close to 100%. Toward the end of the Pulse Charge cycle the Battery Charger will be switched off for long periods between short on-pulses. Eventually, the off-time will become longer than the value specified by bit **TPOFFMAX (page 21)**, and the charging cycle will terminate (bit **EOC (page 20)** is set). Charging will resume if the battery voltage drops below VNOBATDET.

If the battery voltage drops below VNOBATDETECT (page 8), e.g. if the battery is removed after charging is finished, **EOC (page 20)** will be cleared and the battery charger controller will resume in pulse charge mode to enable operation of the device without battery. The no battery status is indicated with bit **NoBat (page 20)**.

If the battery is replaced after charging is finished and the on-pulse duration TPON (page 21) becomes longer than TPOFFMAX (page 21), the charge controller will clear bit CVM (page 19) and return to Constant Current or Fast Charge mode, depending on bit Fast (page 20).

**Note:** With **TPOFFMAX** = 11 (no termination), the condition for returning to Constant Current or Fast Charge mode will never be met. Bit **CVM** will be ambiguous in this case.

If AutoChgTerm (page 21) is 0, the battery continues to be charged after EOC.

During on-pulses the instantaneous battery voltage may exceed VCHOFF by several hundred millivolts. However, no harm will be done to the battery if **TPON** (page 21) is selected to be shorter than the electrochemical time constant of the battery.

By adding an external gate-source capacitor the switching edges of the P-channel MOSFET can be slowed down further. This prevents an external battery charge adapter with poor transient response from subjecting the VCHARGER pin to excessive voltage when the P-channel MOSFET turns off, and prevents excessive current into the battery when the P-channel MOSFET turns on.

Figure 6. Startup and Pulse Charging for Lithium-Based Batteries

Battery Charger Controller

Data Sheet

#### 6.1.8 Battery Presence Detection

When active, the charge controller constantly monitors the voltage drop across an external current sense resistor (RSENSE) connected in series between the negative battery terminal and ground. In case no battery is connected to the system, no current can flow through RSENSE. If no (dis)charge current flow is detected, bits NoBat (page 20) and CVM (page 19) will be set.

If a battery is re-connected to the system, current will be flowing through R<sub>sense</sub>. If a (dis)charge current flow is detected, **NoBat** and **CVM** will be cleared. Battery presence indication can be disabled by setting bit **DisBDet (page 21)**.

#### 6.1.9 Operation Without Battery

This feature allows operation of the device without a battery if a charge adapter is applied to the VCHARGER pin and bit **ChEn (page 20)** is set. The battery voltage is regulated to the charge termination threshold VCHOFF (page 8), depending on the setting of bits **BatType (page 20)** and **Li4v2 (page 20)**.

Note that when the charge controller is disabled by clearing bit **ChEn** e.g., during measurement of the battery voltage by an external ADC, the device will be reset when the battery is removed. The "operation without battery" feature can be disabled by setting **DisOWB** (page 21). The minimum required capacitance on VBAT (all buffer caps combined) must be ≥10µF to reduce the ripple on VBAT when operating the AS3604 without battery.

#### 6.1.10 Charge Controller Bypass

The charge controller can be bypassed by setting bit Bypass (page 20). In bypass mode, the charger transistor Q1 (page 2) is fully on. The overvoltage protection however will turn off the transistor, when VBAT ≥ VOVLO (page 8). End-of-charge detection is disabled and has to be performed by the system host, bit EOC is cleared.

Removal of the charge adapter will be indicated in the **Charger Status Register (page 19)** but the charge controller will not be disabled. This feature is especially useful when using current-limited charge adapters with an output voltage close to the charge termination threshold and the system is operating without battery. Note that when the voltage difference between the charge adapter output voltage and the battery is smaller than VCHMIN (page 8) the charger detection circuit will indicate that no charge adapter is connected. Furthermore, Trickle Charge mode is not supported in bypass mode because the current regulation is overruled by bit **Bypass**.

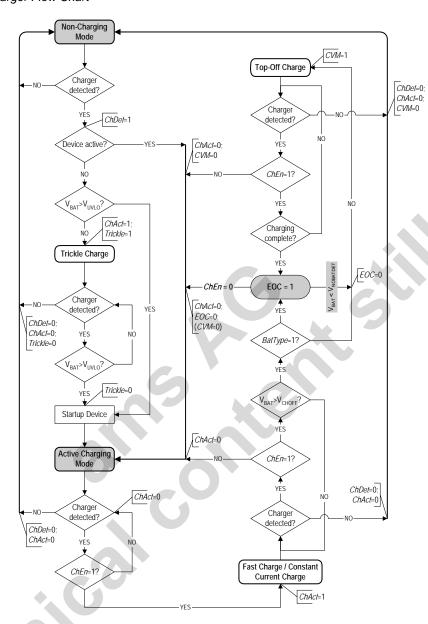

Figure 7. Battery Charger Flow Chart

#### 6.1.11 Overvoltage and Undervoltage Supervision

When the battery voltage exceeds the Vovlo (page 8) threshold (VBAT rising), the charger transistor Q1(page 2) is turned off. Charging will resume if the battery voltage drops below Vovlo (VBAT falling).

Likewise, when the battery voltage drops below the Undervoltage Lockout Threshold VUVLO (VBAT falling) (page 8), a Reset is generated (page 56), which also clears bit ChEn (page 20).

The charger will remain in low current Trickle Charge mode (page 8) until the VUVLO threshold (VBAT rising) has been exceeded.

If ChOv (page 21) =1, the AS3604 monitors the voltage on pin VCHARGER. If the voltage on VCHARGER exceeds VCHOV (bit ChOvH (page 21) = 0) or VCHOVH (bit ChOvH =1) the Battery Charger stops. If the voltage subsequently drops below this limit, the Battery Charger automatically resumes charging.

#### 6.1.12 Charger Detection Circuit

The Battery Charger Controller uses an integrated Charger Detection Circuit to determine if an external battery charger adapter has been applied to pin VCHARGER.

Charger register bits will be set/reset when any of the following conditions are met:

- 1. When the charger voltage exceeds the battery voltage by VCHDET (page 8), Bit chDet (page 19) will be set.

- 2. When the charger voltage drops below VCHMIN (page 8) above the battery voltage, bit **chDet** will be reset. If the charger was active, bit **ChEn** (page 20) = 1, bit **ChAct** (page 19) will also be reset. Charging will resume when the conditions for bit **chDet** = 1 are met.

- 3. If a Reset occurs during charging, the charger will also be reset (ChAct = 0). Bits ChEn and chDet will remain set to 1. To resume charging, the charger must be turned off (ChEn = 0) and then on (ChEn = 1).

#### 6.1.13 Bootstrap Voltage Regulator

To charge even completely discharged batteries, the AS3604 contains an internal bootstrap voltage regulator (LDO V2\_5) which generates a bootstrap voltage (VCHREG) to supply power to the internal Battery Charger circuitry.

#### 6.1.14 Battery Charger Operation

The Battery Charger Controller controls an 8-bit current DAC which delivers a current (IDAC) that will generate a voltage (VGS) over an external resistor (RGS) connected between the gate and source of an external P-channel MOSFET.

#### Charge Current Regulator

The Charge Current Regulator has a resolution of 0.625 mV or 12.5 mA when using a  $50 \text{m}\Omega$  sense resistor. The resolution is programmable using the **Charger Control Register** (page 20).

Table 5. Charge Current Regulator Parameters

| Symbol     | Parameter                                               | Min | Тур   | Max | Unit |

|------------|---------------------------------------------------------|-----|-------|-----|------|

| IVGATE,LSB | Resolution of VGATE current; bit Boost (page 20) = 0    |     | 0.5   |     | μΑ   |

| IVGATE,FS  | Full-scale value of VGATE current; bit <b>Boost</b> = 0 |     | 127.5 |     | μΑ   |

Note: Setting bit Boost (page 20) = 1 multiplies this current by a factor of 10.

#### 6.1.15 Charger Total Current Regulation

During normal operation, the AS3604 controls the charging current through the battery. Alternatively, it is possible to regulate the maximum current from the charger (see Figure 8).

If the shunt resistor is connected as shown in Figure 8, the charger regulates the current from the charger adapter. The internal register bit **AutoChgTerm** (page 21) must be set to 0 in this configuration. If **AutoChgTerm** is reset, the charger is not switched off if an end-of-charge condition is reached (only an interrupt is sent to the baseband processor).

If the end-of-charge interrupt is sent to the baseband processor, the baseband processor can terminate the charging cycle by setting bit AutoChgTerm to 1. This should only be done if a battery is present. If bit AutoChgTerm is 1 and the battery is subsequently removed, the baseband processor should immediately reset bit AutoChgTerm to 0 and bit ChEn (page 20) should be set to 0 and then to 1 again to restart the charger and avoid a reset cycle of the system due to undervoltage condition on the battery.

To avoid a reset cycle of the system under any condition, bit AutoChgTerm' should usually be left at 0.

**Note:** The AS3604 measures the current from the charger including the current used for charging the battery and the current flowing to the whole system. The end-of-charge detection is done by comparing this current against the value set in the bits **Trickle Current (page 21)**. Therefore this value has to be set sufficiently high to obtain a proper end-of-charge condition. If this is not possible, a timeout timer inside the baseband processor should be set allowing for an end-of-charge indication in the user interface.

Figure 8. Total Current Regulation

#### 6.1.16 Gas Gauge

The Gas Gauge enables remaining capacity estimation of the battery by tracking the net current flow into and out of the battery using a Voltage-to-Frequency Converter.

Table 6. Gas Gauge Parameters

| Symbol              | Parameter                    | Min  | Тур     | Max | Unit | Notes                                  |

|---------------------|------------------------------|------|---------|-----|------|----------------------------------------|

| fclk                | Internal Reference Clock     | 1.0  | 1.1     | 1.2 | MHz  |                                        |

| fvFC                | Sample Frequency             |      | fcLK/59 |     | Hz   | fclk: internal reference clock.        |

| VISENSP/<br>VISENSN | Input Voltage                | -0.1 |         | 0.1 | V    |                                        |

| ZISENSP/<br>ZISENSN | Input Impedance              | 4.67 |         |     | ΜΩ   |                                        |

| Avfc                | (Dis)Charge Gain             |      | 91.0    | _   | Hz/V | fcLK = 1.1MHz                          |

| FRvfc               | Fundamental Rate             |      | 3.05    |     | μVh  | ICLK = 1.1WIFIZ                        |

| Voff                | Uncompensated Offset Voltage | -500 |         | 500 | μV   | Offset voltage ISENSP - ISENSN         |

| Voff,comp           | Compensated Offset Voltage   | -50  | ±10     | 50  | μV   | Offset error after offset compensation |

#### Voltage-to-Frequency Converter

The Voltage-to-Frequency Converter constantly monitors the voltage drop across an external current sense resistor (RSENSE) connected in series between the negative battery terminal and ground.

The use of an additional external RC lowpass filter is highly recommended. Using two  $47k\Omega$  resistors, R2 and R3 (page 2), and a  $0.1\mu\text{F}$  ceramic capacitor, C28 (page 2), the filter cutoff is approximately 16.9 Hz. This filter will capture the effect of most spikes, and will thus allow the Gas Gauge to accurately detect the total charge that has gone into or out of the battery.

#### Charge Current Accumulator

The Charge Current Accumulator is an internal 15-bit up/down counter with sign bit. It is incremented when current is charged into the battery and decremented when current is drawn out of the battery. It is updated at a rate of one count per  $3.05\mu\text{Vh}$ , which is equivalent to one count per  $61.03\mu\text{Ah}$  (using a  $50\text{m}\Omega$  current sense resistor).

If the counter is not read, it will roll over beyond FFFF<sub>h</sub>, which occurs after approximately 2000mAh of charge (using a  $50m\Omega$  sense resistor). It is the responsibility of the host system to read and reset the counter before rollover occurs.

The contents of the Charge Current Accumulator will be transferred into the **Delta Charge MSB Register** (page 22) and the **Delta Charge LSB Register** (page 22) when bit **UpdReq** (page 22) has been set. After the Delta Charge MSB/LSB registers have been updated successfully, bit **UpdReq** is cleared automatically and the Charge Current Accumulator will be reset along with bit **sign**.

Battery Charger Controller

**Data Sheet**

#### Constant Voltage Regulator

The Constant Voltage Regulator acts directly on the setting of the 8-bit current DAC. It will commence when threshold VCHOFF (page 8) has been exceeded for the first time as long as bit **Pulse (page 20)** is not set.

#### Elapsed Time Counter

The sample clock (fVFC) of the Gas Gauge is fed to a 14-bit clock count divider, whose output signal is used as a clocking signal for the 16-bit Elapsed Time Counter, resulting in an equivalent rate of 1.1379 counts per second (4096.60 counts = 1 hour, 1 count = 0.8788s).

The Elapsed Time Counter can rollover beyond FFFFh which occurs after about 16 hours. If this happens the value given by the counter will be ambiguous. It is the responsibility of the host system to read the Elapsed Time Counter before rollover occurs.

The content of the Elapsed Time Counter is transferred into the **Elapsed Time MSB Register** (page 23) and the **Elapsed Time LSB Register** (page 23) when bit **UpdReq (page 22)** has been set. After the Elapsed Time MSB/LSB registers have been updated successfully, bit **UpdReq** is cleared automatically and the Elapsed Time Counter is reset.

#### Offset Calibration Mode

Although the Voltage-to-Frequency Converter compensates for the offset of the Integrator, the Gas Gauge features an additional offset calibration mode to enhance the measurement accuracy even further. By setting bit CalReq (page 22) the Integrator is reset and the offset calibration mode is activated.

The offset is accumulated during 16 clocks of the elapsed time counter (16x0.8788s = 14.06 sec). When offset calibration is complete, bit **CalReq** is cleared automatically and the offset value is transferred into the **Delta Charge MSB Register** (page 22) and the **Delta Charge LSB Register** (page 22) for calculating the actual average current (page 18).

The calculated value defines the measured offset between ISENSP and ISENSN. It has a resolution of  $3.05\mu V$ . This offset value is used as a correction factor for calculating the actual average current.

Note: Offset calibration is not possible while the charger is active. If bit CalReq is set while the charger is active, the calibration will start automatically after the charger has been disabled by clearing bit ChEn or if the external battery charger adapter has been removed. If, during offset calibration, the charger is enabled, offset calibration mode is terminated, bit CalReq is cleared, the current value of the Elapsed Time Counter is transferred to the Elapsed Time MSB/LSB registers, and the Delta Charge MSB/LSB registers are loaded with FFFFh.

#### Calculation of Battery Status

The host system can calculate all the parameters necessary for estimating the remaining battery capacity by evaluating FGOffCal (the Elapsed Time MSB/LSB (page 23) and the Delta Charge MSB/LSB (page 22) registers).

#### Calculating Elapsed Time

The host system can evaluate the change in time ( $\Delta t$ ) by setting bit **UpdReq** (page 22) and reading the Elapsed Time MSB/LSB registers after bit **UpdReq** has been automatically cleared. The change in time in seconds is given by:

$$\Delta t = ElapsedTime \times 3600 / 4096.60 [s]$$

(EQ 1)

The absolute accuracy of  $(\Delta t)$  is directly related to the absolute accuracy of fCLK. To cancel errors associated with the accuracy of the oscillator, a correction factor (CV) can be introduced. CV can be evaluated by comparing the change in time calculated by (EQ 1) with a reference value  $(\Delta tREF)$  obtained from a RTC or measured during system calibration. CV is given by:

$$CV = \Delta t REF / \Delta t$$

(EQ 2)

By multiplying  $\Delta t$  with CV, the correct value for the change in time ( $\Delta t corr$ ) can be calculated:

$$\Delta t CORR = CV \times \Delta t [s]$$

(EQ 3)

#### Calculating Average Current

The host system can calculate the average current (IAVG) during the last time period by setting bit **UpdReq** (page 22) and reading the Delta Charge MSB/LSB registers and the Elapsed Time MSB/LSB registers after **UpdReq** has been automatically cleared. Together with FGOffCal, determined during offset calibration mode, IAVG is given by:

$$IAVG = DeltaCharge / (\Delta t \times AVFC \times Rsense) - FGOffCal \times 3.05 \,\mu V / Rsense [A]$$

(EQ 4)

Battery Charger Controller

Data Sheet

$\Delta t$  is the change in time in seconds calculated by (EQ 1), AVFC is the gain of the Voltage-to-Frequency Converter in Hz/V, RSENSE is the value of the sense resistor in ohms, and FGOffCal is the offset calibration value. As *DeltaCharge* and  $\Delta t$  both are proportional to the oscillator frequency, no correction factor needs to be introduced in the formula.

#### Calculating Accumulated Capacity

Accumulated capacity is used to calculate the absolute remaining capacity of the battery. It is given by:

$$QACC = IAVG \times \Delta tCORR [As]$$

(EQ 5)

#### Calculating the Remaining Capacity

Calculation of the remaining battery capacity (RC) is the goal of the Gas Gauge. It is given by:

$$RC = RC + QACC [As]$$

(EQ 6)

#### Calculating the Time to Empty

Time to empty (*tte*) is calculated from the average current (*IAVG*) given by (EQ 4). The longer the time period for which *IAVG* is calculated, the more accurate the value for *IAVG* and therefore the estimated the will be. It is given by:

$$tTE = RC / IAVG [s]$$

(EQ 7)

#### 6.1.17 Battery Charger Controller Registers

The Battery Charger Controller is controlled by the registers listed in Table 7.

Table 7. Battery Charger Controller Register Summary

| Name                      | Addr | B7     | B6              | B5          | В4                      | В3      | B2       | B1      | В0    | Page |

|---------------------------|------|--------|-----------------|-------------|-------------------------|---------|----------|---------|-------|------|

| Charger Status Register   | 53   | Bypass | NoBat           | EOC         | CVM                     | Trickle | IntReg   | ChAct   | chDet | 19   |

| Charger Control Register  | 20   | ChOvEn | Boost           | Bypass      | Pulse                   | Li4v2   | Fast     | BatType | ChEn  | 20   |

| Charger Timing Register   | 44   | TPOF   | FMAX            |             | TPOFF                   |         |          | TPON    |       | 21   |

| Charger Current Register  | 22   | ChOv   | ChOvH           | Bat_v       | Bat_v ConstantCurrent T |         | Trickle  | Current | 21    |      |

| Charger Config Register   | 66   | N/A    | AutoChg<br>Term | CVMtst      | DisOWB                  | DisBDet | Dis Hyst | Wide    | N/A   | 21   |

| Gas Gauge Register        | 21   |        | N.              | /A          |                         | CalMod  | CalReq   | UpdReq  | FGEn  | 22   |

| Delta Charge MSB Register | 54   | sign   | 214             | <u>2</u> 13 | 212                     | 211     | 210      | 29      | 28    | 22   |

| Delta Charge LSB Register | 55   | 27     | 26              | 25          | 24                      | 23      | 22       | 21      | 20    | 22   |

| Elapsed Time MSB Register | 56   | 215    | 214             | <u>2</u> 13 | 212                     | 211     | 210      | 29      | 28    | 23   |

| Elapsed Time LSB Register | 57   | 27     | 26              | 25          | 24                      | 23      | 22       | 21      | 20    | 23   |

| PreCurDac Register        | 67   | 27     | 26              | 25          | 24                      | 23      | 22       | 21      | 20    | 23   |

| ٨٨٨      | r: 52    | Charger S         | Charger Status Register                        |                                                                                                                                                      |  |  |  |  |  |  |

|----------|----------|-------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Addr: 53 |          | Displays st       | Displays status of Battery Charger Controller. |                                                                                                                                                      |  |  |  |  |  |  |

| Bit      | Bit Name | Default           | Default Access Bit Description                 |                                                                                                                                                      |  |  |  |  |  |  |

| 0        | chDet    | 00 <sub>h</sub>   | R                                              | O = No external battery charger detected.     External battery charger adapter has been detected. Charger voltage exceeds battery voltage by VCHDET. |  |  |  |  |  |  |

| 1        | ChAct    | 00 <sub>h</sub>   | R                                              | 0 = Charger is off or in Trickle Charge mode.<br>1 = Charger is in Constant Current, Fast Charge, or Pulse Charge mode.                              |  |  |  |  |  |  |

| 2        | IntReg   | 00 <sub>h</sub>   | R                                              | 0 = Bit is cleared when VBAT > VUVLO.                                                                                                                |  |  |  |  |  |  |

| 2        |          |                   |                                                | 1 = LDO V2_5 is operating.                                                                                                                           |  |  |  |  |  |  |

|          |          | 00 <sub>h</sub>   | R                                              | 0 = Trickle charging is off.                                                                                                                         |  |  |  |  |  |  |

| 3        | Trickle  |                   |                                                | 1 = Charger is in Trickle Charge mode. Trickle current is set by the Charger Current Register (page 21).                                             |  |  |  |  |  |  |

|          |          |                   | 00 <sub>h</sub> R                              | 0 = Battery charger is not in top-off charge mode.                                                                                                   |  |  |  |  |  |  |

| 4        | CVM      | И 00 <sub>h</sub> |                                                | 1 = Battery charger is in top-off charge mode (constant voltage or pulse charge mode).                                                               |  |  |  |  |  |  |

| ۸۵۵      | r: 52    | Charger S                                      | Charger Status Register |                                                                                                                                                                                             |  |  |  |  |  |  |

|----------|----------|------------------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Addr: 53 |          | Displays status of Battery Charger Controller. |                         |                                                                                                                                                                                             |  |  |  |  |  |  |

| Bit      | Bit Name | Default                                        | Access                  | Bit Description                                                                                                                                                                             |  |  |  |  |  |  |

|          |          |                                                | R                       | 0 = Battery charger is off or charging is in progress; automatically cleared when <b>ChEn</b> (page 20) is cleared.                                                                         |  |  |  |  |  |  |

| 5        | EOC      | 00 <sub>h</sub>                                |                         | 1 = End of Charge. Automatically set when CV or pulse charging is completed or when VCHOFF is exceeded during charging of Ni-based batteries.                                               |  |  |  |  |  |  |

| 6        | NoBat    | 00 <sub>h</sub>                                | R                       | No battery detection.  0 = Battery is connected, when <b>DisBDet</b> (page 21) is set, and/or <b>ChEn</b> (page 20) is cleared.  1 = No battery detected at VBAT.                           |  |  |  |  |  |  |

| 7        | Bypass   | 00 <sub>h</sub>                                | R                       | Indicates charger bypass mode.  0 = Normal charger operating mode.  1 = Indicates that charger is in bypass mode; charger transistor Q1 (page 2) is fully on and EOC detection is disabled. |  |  |  |  |  |  |

| Addr: 20 |          | Charger Control Register                              |        |                                                                                                                                                                                  |  |  |  |  |  |

|----------|----------|-------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Addi     | . 20     | Controls operation of the Battery Charger Controller. |        |                                                                                                                                                                                  |  |  |  |  |  |

| Bit      | Bit Name | Default                                               | Access | Bit Description                                                                                                                                                                  |  |  |  |  |  |

| 0        | ChEn     | Boot ROM                                              | R/W    | 0 = Disables charging. 1 = Enables charging.                                                                                                                                     |  |  |  |  |  |

| 1        | BatType  | Boot ROM                                              | R/W    | Li4v2  00 = Li-ion battery with coke anode; VCHOFF (page 8) = 4.1V  10 = Li-ion battery with graphite anode; VCHOFF = 4.2V  x1 = Nickel-based battery; VCHOFF = 5.52V            |  |  |  |  |  |

| 2        | Fast     | Boot ROM R/W                                          |        | 0 = Selects Constant Current charge mode.<br>1 = Selects Fast Charge mode.                                                                                                       |  |  |  |  |  |

| 3        | Li4v2    | Boot ROM                                              | R/W    | Selects the type of lithium-based battery.  0 = VCHOFF (page 8) = 4.1V for Li+ battery with coke anode.  1 = VCHOFF = 4.2V for Li+ battery with graphite anode.                  |  |  |  |  |  |

| 4        | Pulse    | Boot ROM                                              | R/W    | Selects top-off charging mode.  0 = Select constant voltage charging mode.  1 = Select pulse charging mode.                                                                      |  |  |  |  |  |

| 5        | Bypass   | Boot ROM                                              | R/W    | Enable bypassing of charge controller.  0 = Normal charger operation.  1 = Select charger bypass mode; charger transistor Q1 (page 2) is fully on and EOC detection is disabled. |  |  |  |  |  |

| 6        | Boost    | Boot ROM                                              | R/W    | Selects output of current DAC at pin VGATE.  0 = Nominal current (max. 128µA).  1 = 10x nominal current (default; max.1.28mA).                                                   |  |  |  |  |  |

| 7        | ChOvEn   | Boot ROM                                              | R/W    | <ul><li>0 = Disable automatic termination of charging.</li><li>1 = Enable automatic termination of charging.</li></ul>                                                           |  |  |  |  |  |

| Addı | r. 11    | Charger Timing Register             |        |                                                                                     |                                           |  |  |  |  |

|------|----------|-------------------------------------|--------|-------------------------------------------------------------------------------------|-------------------------------------------|--|--|--|--|

| Addi |          | Sets parameters for pulse charging. |        |                                                                                     |                                           |  |  |  |  |

| Bit  | Bit Name | Default                             | Access | Bit Description                                                                     |                                           |  |  |  |  |

|      |          |                                     |        | Sets pulse charge mode minimum steps of 137.31ms.                                   | on-time from 137.31ms to 1098.48ms in     |  |  |  |  |

| 0.0  | TDON     | 004                                 | D 444  | 000 = 137.31ms                                                                      | 100 = 686.55ms                            |  |  |  |  |

| 2:0  | TPON     | 001                                 | R/W    | 001 = 274.68ms (default)                                                            | 101 = 823.86ms                            |  |  |  |  |

|      |          |                                     |        | 010 = 411.93ms                                                                      | 110 = 961.17ms                            |  |  |  |  |

|      |          |                                     |        | 011 = 549.24ms                                                                      | 111 = 1098.48ms                           |  |  |  |  |

|      |          |                                     | R/W    | Sets pulse charge mode minimum steps of 68.65ms.                                    | off-time from 68.65ms to 549.24ms in      |  |  |  |  |

| - 0  | TDOEE    |                                     |        | 000 = 68.65ms                                                                       | 100 = 343.28ms                            |  |  |  |  |

| 5:3  | TPOFF    | 001                                 |        | 001 = 137.31ms (default)                                                            | 101 = 411.93ms                            |  |  |  |  |

|      |          |                                     |        | 010 = 205.97ms                                                                      | 110 = 480.59ms                            |  |  |  |  |

|      |          |                                     |        | 011 = 274.62ms                                                                      | 111 = 549.24ms                            |  |  |  |  |

|      |          |                                     |        | , ,                                                                                 | n off-time before charging is terminated. |  |  |  |  |

|      | TPOFFMA  |                                     |        | $00 = 4 \times \text{TPON}$ (page 21) (yields 1/5 of the constant charging current. |                                           |  |  |  |  |

| 7:6  | X        | 01                                  | R/W    | 10 = 19 x <b>TPON</b> (yields 1/20 of the constant charging current.                |                                           |  |  |  |  |

|      | <u> </u> |                                     |        | 01 = 9 x <b>TPON</b> (yields 1/10 of the constant charging current).                |                                           |  |  |  |  |

|      |          |                                     |        | 11 = No termination (not recomme                                                    | ended).                                   |  |  |  |  |

| ۸۸۸      | r: 66     | Charger C  | Charger Config Register                 |                                                                    |  |  |  |  |  |

|----------|-----------|------------|-----------------------------------------|--------------------------------------------------------------------|--|--|--|--|--|

| Addr: 66 |           | Sets addit | Sets additional charger configurations. |                                                                    |  |  |  |  |  |

| Bit      | Bit Name  | Default    | Access                                  | Bit Description                                                    |  |  |  |  |  |

| 0        |           |            |                                         | N/A                                                                |  |  |  |  |  |

| 1        | Wide      | 0          | R/W                                     | For test purposes only.                                            |  |  |  |  |  |

| 2        | Dis Hyst  | 0          | R/W                                     | For test purposes only.                                            |  |  |  |  |  |

| 3        | D:-DD-4   | 0          | R/W                                     | 0 = Enable battery presence indication (default).                  |  |  |  |  |  |

| 3        | DisBDet   | U          |                                         | 1 = Disable battery presence indication.                           |  |  |  |  |  |

| 4        | DisOWB    | 0          | R/W                                     | 0 = Enable operation without battery (default).                    |  |  |  |  |  |

| 4        | DISOVIB   | U          | IX/VV                                   | 1 = Disable operation without battery. Disable analog comparators. |  |  |  |  |  |

| 5        | CVMtst    | 0          | R/W                                     | For test purposes only.                                            |  |  |  |  |  |

| 6        | AutoChgT  | 0          | R/W                                     | 0 = Disable automatic EOC.                                         |  |  |  |  |  |

| 0        | erm 0 R/W |            | FX/VV                                   | 1 = Enable automatic EOC.                                          |  |  |  |  |  |

| 7        |           |            |                                         | N/A                                                                |  |  |  |  |  |

| ۸۵۵      | 22       | Charger Current Register |                                                         |                                                                                                                |                                                           |  |  |  |  |

|----------|----------|--------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|--|--|--|

| Addr: 22 |          | Sets current             | Sets current for trickle and Constant Current charging. |                                                                                                                |                                                           |  |  |  |  |

| Bit      | Bit Name | Default                  | Access                                                  | Bit Description                                                                                                | Bit Description                                           |  |  |  |  |

| 1.0      | Trickle  | Boot ROM                 | DAV                                                     | Sets the Trickle Charge mode from (1.25mV to 10mV)/RSENSE in steps                                             |                                                           |  |  |  |  |

| 1:0      | Current  | (01)                     | R/W                                                     | 00 = 1.25mV/Rsense                                                                                             | 10 = 5.00mV/Rsense                                        |  |  |  |  |

|          |          |                          |                                                         | 01 = 2.5mV/Rsense (default)                                                                                    | 11 = 10mV/Rsense                                          |  |  |  |  |

|          |          |                          |                                                         | Sets the charging current in Constant Current mode from: (0mV to 35mV) x Rsense-1 in steps of 5mV x Rsense -1. |                                                           |  |  |  |  |

| 4:2      | Constant | Boot ROM<br>(011)        | R/W                                                     | 000 = No current.                                                                                              | 100 = 20mv/Rsense                                         |  |  |  |  |

| 4.2      | Current  |                          |                                                         | 001 = 5mV/Rsense                                                                                               | 101 = 25mV/Rsense                                         |  |  |  |  |

|          |          |                          |                                                         | 010 = 10mV/Rsense                                                                                              | 110 = 30mV/Rsense                                         |  |  |  |  |

|          |          |                          |                                                         | 011 = 15mV/Rsense (default)                                                                                    | 111 = 35mV/Rsense                                         |  |  |  |  |

| 5        | Bat_v    | N/A                      | R                                                       | 0 = If battery voltage is < 4.1V (bit                                                                          | <b>Li4v2 (page 20)</b> ) = 1 or 4.0V ( <b>Li4v2</b> = 0). |  |  |  |  |

| 5        | Dai_v    | IN/A                     | K                                                       | 1 = If battery voltage is $> 4.1 \text{V} \text{ (Li4v2)} = 1 \text{ or } 4.0 \text{V} \text{ (Li4v2} = 0).$   |                                                           |  |  |  |  |

| 6        | ChOvH    | Boot ROM                 | R/W                                                     | 0 = Sets overvoltage protection low-threshold to 6.05V.                                                        |                                                           |  |  |  |  |

|          | CHOVII   | (0h)                     |                                                         | 1 = Sets overvoltage protection high-threshold to 6.5V                                                         |                                                           |  |  |  |  |

| 7        | ChOv     | 0h                       | R                                                       | 0 = No charger overvoltage detected.                                                                           |                                                           |  |  |  |  |

|          | CHOV     | UH                       |                                                         | 1 = Charger overvoltage detected (VCHARGER).                                                                   |                                                           |  |  |  |  |

| Addr: 21 |          | Gas Gauge Register |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|----------|----------|--------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Add      | 1. 21    | Controls the       | Fuel Gauge. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| Bit      | Bit Name | Default Access     |             | Bit Description                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 0        | FGEn     | 0b                 | R/W         | Controls the operation of the Gas Gauge.  0 = Disables Gas Gauge.                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 1        | UpdReq   | Ob                 | R/W         | 1 = Enables Gas Gauge.  Controls the updates of the Delta Charge MSB/LSB registers and the Elapsed Time MSB/LSB registers. When set, this bit is cleared automatically after the Delta Charge MSB/LSB registers and the Elapsed Time MSB/LSB registers have been successfully updated.  O = Indicates update of Delta Charge MSB/LSB registers and Elapsed Time MSB/LSB registers has been completed.  1 = Request update of Delta Charge and Elapsed Time Registers |  |  |  |

| 2        | CalReq   | Ob                 | R/W         | Controls offset calibration. When set, this bit is cleared automatically after offset calibration has successfully completed.  0 = Indicates offset calibration has completed or forces termination of offset calibration.  1 = Request offset calibration.                                                                                                                                                                                                          |  |  |  |

| 3        | CalMod   | 0b                 | R/W         | Sets the offset calibration mode.  0 = Connect inputs to ground.  1 = Use ISENSP and ISENSN (for testing purposes only).                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 7:4      |          |                    |             | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| Addı | r: 51    | Delta Charge MSB Register |                 |                                                                                                                                                    |  |  |  |  |

|------|----------|---------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Auui | 1. 54    | Holds the an              | nount of charge | e since last reading.                                                                                                                              |  |  |  |  |

| Bit  | Bit Name | Default                   | Access          | Bit Description                                                                                                                                    |  |  |  |  |

| 0    | 28       | 00 <sub>h</sub>           | R               |                                                                                                                                                    |  |  |  |  |

| 1    | 29       | 00 <sub>h</sub>           | R               | This register (along with Delta Charge LSB Register) is                                                                                            |  |  |  |  |

| 2    | 210      | 00 <sub>h</sub>           | R               | maintained in two's complement form with a resolution of 3.05µVh and a full-scale value of ±99.98mVh. When using a                                 |  |  |  |  |

| 3    | 211      | 00 <sub>h</sub>           | R               | $5.05\mu\text{VH}$ and a full-scale value of ±99.96HVH. When using a $50\text{m}\Omega$ current sense resistor, this is equivalent to a resolution |  |  |  |  |

| 4    | 212      | 00 <sub>h</sub>           | R               | of 61.03uAh and a full-scale value of 1.999Ah. The <b>sign</b> bit is                                                                              |  |  |  |  |

| 5    | 213      | 00 <sub>h</sub>           | R               | set for negative values. This register will be updated after                                                                                       |  |  |  |  |

| 6    | 214      | 00 <sub>h</sub>           | R               | setting bit UpdReq (page 22) = 1.                                                                                                                  |  |  |  |  |

| 7    | sign     | 00 <sub>h</sub>           | R               | 3 · · · · · · · · · · · · · · · · · · ·                                                                                                            |  |  |  |  |

| Addı | ·· 55    | Delta Charge LSB Register                      |        |                                                                    |  |  |  |  |  |

|------|----------|------------------------------------------------|--------|--------------------------------------------------------------------|--|--|--|--|--|

| Addi | . 33     | Holds the amount of charge since last reading. |        |                                                                    |  |  |  |  |  |

| Bit  | Bit Name | Default                                        | Access | Bit Description                                                    |  |  |  |  |  |

| 0    | 20       | 00 <sub>h</sub>                                | R      |                                                                    |  |  |  |  |  |

| 1    | 21       | 00 <sub>h</sub>                                | R      | This register (along with Delta Charge MSB Register) is            |  |  |  |  |  |

| 2    | 22       | 00 <sub>h</sub>                                | R      | maintained in two's complement form with a resolution of           |  |  |  |  |  |

| 3    | 23       | 00 <sub>h</sub>                                | R      | 3.05uVh and a full-scale value of ±99.98mVh. When using a          |  |  |  |  |  |

| 4    | 24       | 00 <sub>h</sub>                                | R      | 50m $Ω$ current sense resistor, this is equivalent to a resolution |  |  |  |  |  |

| 5    | 25       | 00 <sub>h</sub>                                | R      | of 61.03uAh and a full-scale value of 1.999Ah. This register is    |  |  |  |  |  |

| 6    | 26       | 00 <sub>h</sub>                                | R      | updated after setting bit UpdReq (page 22) = 1.                    |  |  |  |  |  |

| 7    | 27       | 00 <sub>h</sub>                                | R      |                                                                    |  |  |  |  |  |

| Add | r: 56    | Elapsed Time MSB Register                  |                        |                                                                |  |  |  |  |

|-----|----------|--------------------------------------------|------------------------|----------------------------------------------------------------|--|--|--|--|

| Add | 1. 30    | Holds the elapsed time since last reading. |                        |                                                                |  |  |  |  |

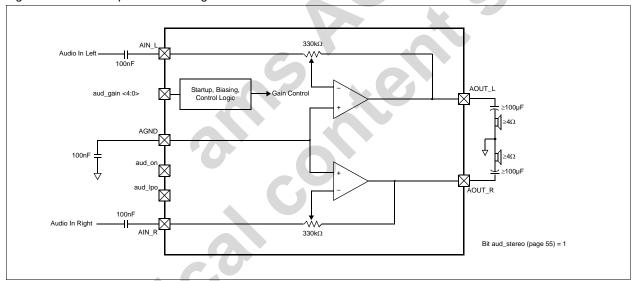

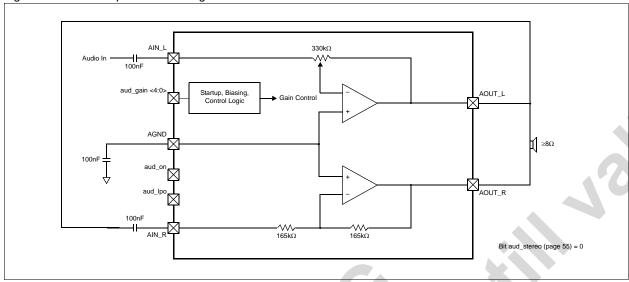

| Bit | Bit Name | Default                                    | Access Bit Description |                                                                |  |  |  |  |